Waktu adalah benang tak terlihat yang menghubungkan perangkat keras dan perangkat lunak. Dalam sistem tertanam, mikrokontroler, dan perangkat IoT, milidetik sangat berarti. Penundaan beberapa mikrodetik dapat menyebabkan kegagalan sistem, kejadian kehilangan data, atau bahaya keselamatan. Untuk memvisualisasikan hubungan temporal ini, insinyur beralih ke Diagram Waktu UML. Diagram ini menyediakan cara ketat untuk memodelkan perilaku sinyal seiring waktu, memastikan komponen perangkat keras dan logika perangkat lunak beroperasi secara sinkron.

Memodelkan antarmuka perangkat keras-perangkat lunak membutuhkan ketepatan. Berbeda dengan diagram interaksi standar, diagram waktu berfokus pada momen tepat saat sinyal berubah keadaan. Panduan ini mengeksplorasi cara membuat, menafsirkan, dan menerapkan diagram ini dalam skenario rekayasa dunia nyata. Kita akan membahas transisi sinyal, wilayah aktif, dan batasan waktu tanpa bergantung pada alat tertentu.

⚙️ Memahami Tujuan Utama

Diagram Waktu UML adalah diagram perilaku yang menekankan batasan waktu objek dan sinyal. Ini sangat berguna ketika kebenaran suatu sistem bergantung pada waktu kejadian, bukan hanya urutan pesan.

- Akurasi Temporal: Menentukan kapan suatu sinyal harus naik atau turun.

- Pemantauan Status: Melacak status suatu objek selama interval waktu tertentu.

- Verifikasi Antarmuka: Memvalidasi apakah perangkat keras memenuhi ekspektasi perangkat lunak.

Ketika merancang kontroler tertanam, perangkat lunak mengirim perintah, dan perangkat keras harus merespons dalam jendela waktu tertentu. Jika perangkat keras membutuhkan waktu terlalu lama, perangkat lunak bisa mengalami timeout. Jika merespons terlalu cepat, data bisa tidak bisa dibaca. Diagram waktu menangkap tarian ini.

📉 Komponen Utama Diagram Waktu

Untuk membuat diagram yang valid, Anda harus memahami sintaksnya. Notasi ini distandarisasi, memastikan bahwa insinyur mana pun dapat membaca model ini.

1. Garis Kehidupan

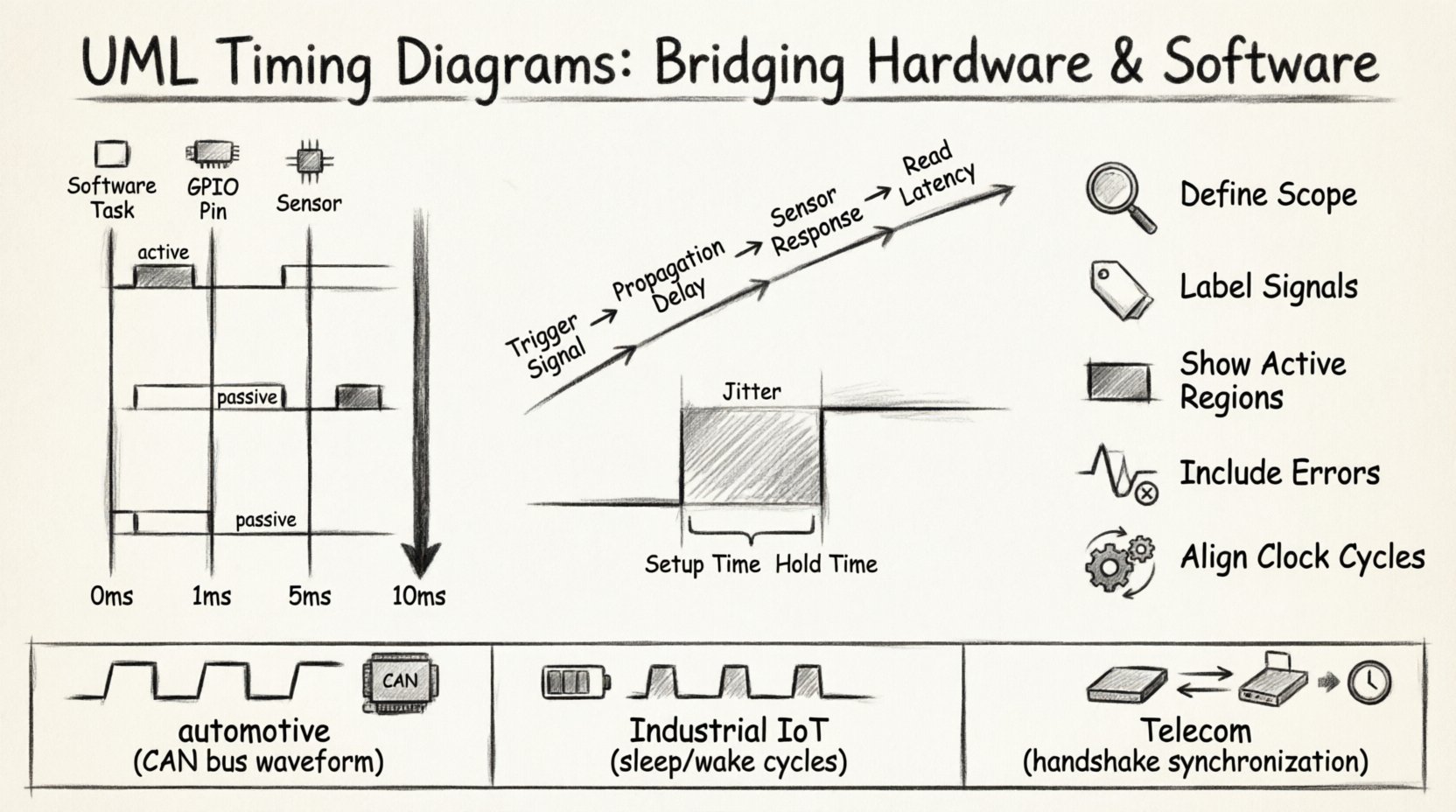

Garis kehidupan mewakili suatu objek atau antarmuka. Dalam konteks perangkat keras-perangkat lunak, garis kehidupan sering sesuai dengan:

- Tugas Perangkat Lunak: Loop utama, penangan interupsi, atau driver.

- Sinyal Perangkat Keras:Pin GPIO, jalur bus (SPI, I2C), atau jalur interupsi.

- Perangkat Eksternal:Sensor, aktuator, atau modul komunikasi.

Setiap garis kehidupan adalah garis vertikal yang membentang ke bawah diagram. Waktu mengalir dari atas ke bawah.

2. Sumbu Waktu

Berbeda dengan diagram urutan, yang fokus pada urutan pesan, diagram waktu memiliki sumbu waktu yang eksplisit. Ini bisa berupa waktu absolut (misalnya, milidetik) atau waktu relatif (misalnya, siklus jam).

- Waktu Absolut:Berguna untuk persyaratan tingkat sistem seperti ‘respons harus terjadi dalam waktu 50ms’.

- Waktu Relatif: Berguna untuk logika internal, seperti “tunggu 3 siklus jam setelah mulai”.

3. Status dan Nilai Sinyal

Sinyal berubah antara status yang telah ditentukan. Dalam logika digital, ini biasanya 0 dan 1. Pada diagram, ini digambarkan dengan batang horizontal pada garis kehidupan.

- Status Aktif:Batang yang terisi menunjukkan sinyal berada pada level tinggi atau diaktifkan.

- Status Pasif:Ruangan kosong atau garis putus-putus yang menunjukkan sinyal berada pada level rendah atau tidak diaktifkan.

- Tidak Diketahui:Tanda tanya atau simbol khusus ketika status tidak ditentukan.

4. Nilai Sinyal

Untuk sinyal kompleks seperti bus data, diagram dapat menampilkan nilai aktual yang sedang dikirim. Ini sangat penting saat memodelkan protokol di mana pola data tertentu memicu perilaku perangkat keras tertentu.

🔌 Pemodelan Antarmuka Perangkat Keras-Perangkat Lunak

Persilangan antara perangkat keras dan perangkat lunak adalah tempat kebanyakan kesalahan waktu terjadi. Perangkat lunak mengasumsikan perangkat keras berperilaku secara terduga; perangkat keras bereaksi terhadap keterbatasan fisik. Diagram waktu menghubungkan celah ini.

Skenario: Pengendalian GPIO dan Penanganan Interupsi

Pertimbangkan sistem di mana mikrokontroler mengendalikan sensor melalui pin Input/Output Umum (GPIO). Perangkat lunak harus membaca data sensor segera setelah sinyal pemicu diberikan.

Elemen-elemen berikut sangat krusial:

- Sinyal Pemicu:Perangkat lunak menulis nilai ke GPIO.

- Keterlambatan Propagasi:Waktu yang dibutuhkan sinyal untuk menempuh jalur dalam rangkaian.

- Respons Sensor:Waktu yang dibutuhkan sensor untuk menstabilkan data.

- Latensi Baca:Waktu yang dibutuhkan CPU untuk mengambil data.

Diagram waktu menggambarkan jarak antara penulisan perangkat lunak dan pembacaan perangkat keras. Jika jaraknya terlalu kecil, pembacaan bisa gagal. Jika jaraknya terlalu besar, sistem menjadi tidak efisien.

Skenario: Latensi Interupsi

Interupsi adalah kejadian asinkron. Diagram harus menunjukkan transisi dari alur eksekusi normal ke rutin layanan interupsi (ISR).

- Pernyataan Interupsi:Pin perangkat keras menjadi tinggi.

- Pergantian Konteks: Perangkat lunak menyimpan status saat ini.

- Eksekusi ISR: Handler berjalan.

- Pemulihan Konteks: Perangkat lunak melanjutkan tugas sebelumnya.

Memodelkan urutan ini membantu insinyur menghitung latensi kasus terburuk, metrik penting untuk sistem waktu nyata.

📊 Menganalisis Kendala Waktu

Kendala adalah aturan yang mengatur diagram. Mereka memastikan bahwa desain memenuhi persyaratan kinerja. Kendala ini sering dinyatakan sebagai ketidaksamaan atau jendela waktu tertentu.

Waktu Siap dan Waktu Tahan

Pada sistem sinkron, data harus stabil sebelum dan sesudah tepi jam. Diagram waktu secara eksplisit menunjukkan jendela-jendela ini.

| Jenis Kendala | Deskripsi | Dampak terhadap Desain |

|---|---|---|

| Waktu Siap | Waktu data harus stabil sebelum tepi jam. | Mengharuskan jam yang lebih lambat atau perangkat keras yang lebih cepat. |

| Waktu Tahan | Waktu data harus tetap stabil setelah tepi jam. | Mengharuskan buffering atau jam yang lebih lambat. |

| Keterlambatan Propagasi | Waktu yang dibutuhkan sinyal untuk menempuh perjalanan dari sumber ke tujuan. | Mempengaruhi frekuensi jam maksimum. |

Jitter dan Variabilitas

Tidak semua kejadian terjadi pada waktu yang persis sama. Jitter adalah variasi dalam waktu sinyal. Dalam diagram, hal ini sering ditampilkan sebagai daerah yang diarsir atau rentang tepi yang mungkin terjadi.

- Jitter Tinggi: Menunjukkan ketidakstabilan, sering disebabkan oleh gangguan atau masalah catu daya.

- Jitter Rendah: Menunjukkan sistem yang stabil dan dapat diprediksi.

Ketika memodelkan antarmuka, desainer harus mempertimbangkan jitter kasus terburuk. Jika jendela waktu terlalu sempit, sistem menjadi tidak dapat diandalkan.

🛠️ Praktik Terbaik untuk Pemodelan yang Efektif

Membuat diagram itu mudah; membuat diagram yang bermanfaat membutuhkan disiplin. Ikuti panduan ini untuk memastikan kejelasan dan manfaatnya.

- Tentukan Ruang Lingkup Secara Jelas: Tentukan apakah Anda memodelkan mikrodetik atau detik. Jangan mencampurkan tingkat ketelitian tanpa penskalaan yang jelas.

- Beri Label Sinyal Secara Jelas: Gunakan nama yang sesuai dengan skema perangkat keras (misalnya,

INT0,CS_N). - Tampilkan Wilayah Aktif: Soroti di mana sinyal sedang menggerakkan beban dibandingkan saat sinyal mengambang.

- Sertakan Kondisi Kesalahan: Tunjukkan apa yang terjadi jika terjadi timeout. Ini membantu dalam proses debugging.

- Sesuaikan dengan Siklus Jam: Jika sistem menggunakan jam, sesuaikan garis-garis grid vertikal dengan tepi jam sebagai acuan.

Kesalahan Umum yang Harus Dihindari

Hindari kesalahan-kesalahan ini untuk menghemat waktu selama proses tinjauan.

- Terlalu Memperumit: Jangan memodelkan setiap siklus instruksi secara terpisah kecuali diperlukan. Fokus pada perilaku antarmuka.

- Mengabaikan Kejadian Asinkron: Interupsi dan pemicu eksternal sering kali mengganggu alur. Pastikan mereka direpresentasikan.

- Mencampur Tingkatan: Jangan mencampurkan penjadwalan protokol tingkat tinggi dengan sinyal listrik tingkat rendah dalam tampilan yang sama.

- Mengasumsikan Kondisi Ideal: Perangkat keras nyata memiliki resistansi dan kapasitansi. Modelkan keterlambatan secara realistis.

🔄 Integrasi dengan Diagram Lainnya

Diagram waktu tidak ada secara terpisah. Mereka melengkapi diagram UML lainnya untuk memberikan tampilan sistem yang lengkap.

Diagram Urutan

Diagram urutan menunjukkan urutan pesan. Diagram waktu menambah dimensi waktu. Gunakan diagram urutan untuk menentukan alur, lalu gunakan diagram waktu untuk memvalidasi waktu pesan-pesan kritis.

Diagram Mesin Status

Mesin status mendefinisikan logika dari suatu objek. Diagram waktu mendefinisikan durasi dari status tersebut. Sebagai contoh, mesin status bisa mengatakan “Tunggu Masukan”. Diagram waktu menunjukkan secara tepat berapa lama tungguan tersebut berlangsung.

Diagram Aktivitas

Diagram aktivitas menunjukkan alur kerja. Diagram waktu dapat digunakan untuk memberi keterangan pada aktivitas tertentu dengan waktu eksekusinya. Ini berguna untuk analisis kinerja.

📡 Aplikasi Dunia Nyata

Mari kita lihat bagaimana diagram-diagram ini diterapkan pada bidang industri tertentu.

1. Sistem Otomotif

Elektronik otomotif membutuhkan waktu yang ketat untuk keamanan. Sinyal rem harus sampai ke kontroler dalam waktu milidetik. Diagram waktu digunakan untuk memverifikasi bahwa bus Controller Area Network (CAN) memenuhi persyaratan latensi ini.

- Fokus:Latensi dan jitter.

- Kendala:Persyaratan waktu nyata keras.

2. IoT Industri

Perangkat IoT sering beroperasi dengan daya terbatas. Diagram waktu membantu mengoptimalkan siklus tidur. Perangkat lunak dapat dimodelkan untuk membangunkan perangkat keras hanya ketika diperlukan, sehingga mengurangi konsumsi daya.

- Fokus:Transisi status daya.

- Kendala:Efisiensi energi.

3. Telekomunikasi

Protokol jaringan bergantung pada sinkronisasi yang tepat. Diagram waktu memodelkan proses saling berjabat tangan antar perangkat untuk memastikan integritas data dalam jarak jauh.

- Fokus:Keterlambatan propagasi dan sinkronisasi.

- Kendala:Throughput data.

🔍 Verifikasi dan Validasi

Setelah diagram dibuat, harus divalidasi. Proses ini memastikan model sesuai dengan implementasi fisiknya.

Simulasi

Gunakan lingkungan simulasi untuk menguji logika waktu. Berikan sinyal input dan amati output terhadap diagram. Perbedaan menunjukkan kelemahan desain.

Analisis Statis

Ulas diagram untuk konsistensi logis. Apakah ada sinyal yang berubah status tanpa pemicu? Apakah ada deadlock di mana status tunggu berlangsung tak terbatas?

Ulasan Kode

Bandingkan kode implementasi dengan diagram. Apakah kode tersebut mencakup penundaan yang diperlukan? Apakah kode tersebut menangani interupsi dengan prioritas yang benar? Diagram ini berfungsi sebagai dokumen referensi.

📝 Ringkasan Praktik

Pemodelan yang efektif dari antarmuka perangkat keras-perangkat lunak membutuhkan pemahaman mendalam terhadap kedua bidang tersebut. Diagram waktu menyediakan kejelasan yang diperlukan.

- Kejelasan:Pastikan lifeline dan sinyal diberi label dengan jelas.

- Presisi:Gunakan satuan waktu dan batasan yang akurat.

- Kelengkapan:Sertakan jalur kesalahan dan peristiwa asinkron.

- Konsistensi:Pertahankan diagram agar selaras dengan kode dan skematik.

Dengan mematuhi prinsip-prinsip ini, tim dapat mengurangi risiko integrasi dan memastikan kinerja sistem yang kuat. Upaya yang diinvestasikan dalam pemodelan akan terbayar saat fase debugging dan pemeliharaan.

🚀 Pertimbangan Akhir

Lanskap sistem tertanam terus berkembang. Seiring perangkat menjadi lebih kompleks, kebutuhan akan model waktu yang presisi meningkat. Diagram Waktu UML menawarkan bahasa standar untuk membahas kompleksitas ini.

Ketika Anda memulai proyek berikutnya, mulailah dengan memetakan antarmuka kritis. Identifikasi di mana waktu tidak dapat ditawar. Gunakan diagram untuk menetapkan ekspektasi bagi tim perangkat keras dan tim perangkat lunak. Pemahaman bersama ini mencegah salah komunikasi dan mempercepat pengembangan.

Ingatlah bahwa diagram adalah dokumen yang hidup. Perbarui sesuai perubahan desain. Jika batasan baru ditambahkan, cerminkan dalam model. Ini menjaga dokumentasi tetap akurat dan bernilai sepanjang siklus hidup produk.

Dengan pendekatan yang tepat, diagram waktu menjadi lebih dari sekadar dokumentasi. Mereka menjadi alat analisis, panduan implementasi, dan standar jaminan kualitas. Jadilah bagian dari presisi yang mereka tawarkan untuk membangun sistem yang handal, efisien, dan kuat.