タイミングは、ハードウェアとソフトウェアを結びつける目に見えない糸である。組み込みシステム、マイコン、IoTデバイスでは、ミリ秒単位の違いが重要になる。数マイクロ秒の遅延でも、システム障害、データ損失、あるいは安全上の危険を引き起こす可能性がある。こうした時間的関係を可視化するために、エンジニアたちはUMLタイミング図に頼る。これらの図は、時間の経過に伴う信号の振る舞いを厳密にモデル化する方法を提供し、ハードウェア部品とソフトウェア論理が同期して動作することを保証する。

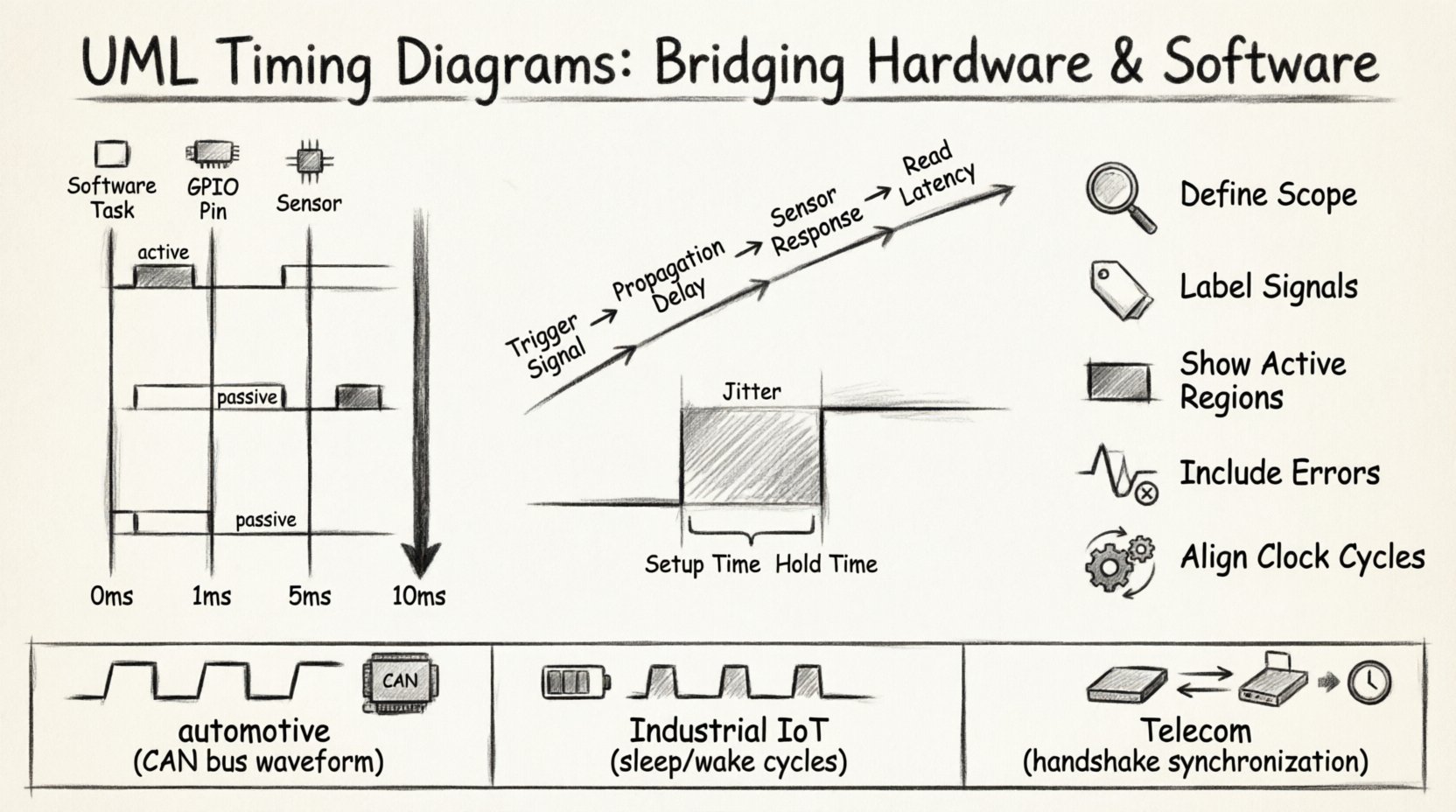

ハードウェア・ソフトウェアインターフェースをモデル化するには正確さが求められる。標準的な相互作用図とは異なり、タイミング図は信号の状態変化が発生する正確な瞬間を焦点とする。このガイドでは、これらの図を実際に構築・解釈・適用する方法を、具体的なツールに依存せずに、現実の工学的状況において探求する。信号遷移、アクティブ領域、タイミング制約について検討する。

⚙️ コア目的の理解

UMLタイミング図は、オブジェクトや信号のタイミング制約に重点を置いた行動図である。システムの正しさがメッセージの順序ではなく、イベントのタイミングに依存する場合に特に有用である。

- 時間的正確性: 信号が立ち上がったり、立ち下がったりするべき時刻を定義する。

- 状態監視: 特定の時間間隔にわたってオブジェクトの状態を追跡する。

- インターフェース検証: ハードウェアがソフトウェアの期待を満たしているかどうかを検証する。

組み込みコントローラーを設計する際、ソフトウェアがコマンドを送信し、ハードウェアは特定の時間枠内に応答しなければならない。ハードウェアが応答に時間がかかりすぎると、ソフトウェアがタイムアウトする可能性がある。逆に応答が早すぎると、データが読み取れなくなる。タイミング図はこうしたやり取りを捉えている。

📉 タイミング図の主要構成要素

有効な図を構築するためには、構文を理解する必要がある。表記法は標準化されており、どのエンジニアもモデルを読み取れるように保証している。

1. ライフライン

ライフラインは、オブジェクトまたはインターフェースを表す。ハードウェア・ソフトウェアの文脈では、ライフラインはしばしば次のようなものに対応する:

- ソフトウェアタスク: メインループ、割り込みハンドラ、またはドライバ。

- ハードウェア信号: GPIOピン、バスライン(SPI、I2C)、または割り込みライン。

- 外部デバイス: センサ、アクチュエータ、または通信モジュール。

各ライフラインは、図の下方向に伸びる垂直線である。時間は上から下へと流れます。

2. 時間軸

シーケンス図とは異なり、メッセージの順序に焦点を当てるのではなく、タイミング図には明確な時間軸がある。これは絶対時間(例:ミリ秒)または相対時間(例:クロックサイクル)のいずれかである。

- 絶対時間: 「応答は50ミリ秒以内に発生しなければならない」などのシステムレベルの要件に有用である。

- 相対時間: 内部論理に有用。たとえば「スタート後、3クロックサイクル待つ」など。

3. シグナルの状態と値

シグナルは定義された状態の間で変化する。デジタル論理では、これらは通常0と1である。図では、ライフライン上の水平なバーで表される。

- アクティブ状態:信号がハイまたはアサートされていることを示す塗りつぶされたバー。

- パッシブ状態:信号がローまたはデアサートされていることを示す空欄または破線。

- 不明:状態が定義されていない場合の疑問符または特定の記号。

4. シグナルの値

データバスのような複雑なシグナルの場合、図は実際に送信されている値を示すことがある。特定のデータパターンが特定のハードウェア動作をトリガーするプロトコルをモデル化する際には、これが重要である。

🔌 ハードウェア-ソフトウェアインターフェースのモデル化

ハードウェアとソフトウェアの交差点で、ほとんどのタイミングエラーが発生する。ソフトウェアはハードウェアが予測可能に動作すると仮定するが、ハードウェアは物理的制約に反応する。タイミング図はこのギャップを埋める。

シナリオ:GPIO制御と割り込み処理

マイコンが汎用入出力(GPIO)ピンを介してセンサーを制御するシステムを検討する。ソフトウェアはトリガーの直後にセンサーのデータを読み取らなければならない。

以下の要素が重要である:

- トリガー信号:ソフトウェアがGPIOに値を書き込む。

- 伝播遅延:信号が回路を通過するまでの時間。

- センサー応答:センサーがデータを安定させるまでの時間。

- 読み取り遅延:CPUがデータを取得するまでの時間。

タイミング図は、ソフトウェアの書き込みとハードウェアの読み取りの間のギャップを可視化する。ギャップが小さすぎると読み取りが失敗する可能性がある。逆にギャップが大きすぎると、システムの効率が低下する。

シナリオ:割り込み遅延

割り込みは非同期イベントである。図は、通常の実行フローから割り込みサービスルーチン(ISR)への遷移を示さなければならない。

- 割り込みアサーション:ハードウェアのピンがハイになる。

- コンテキスト切り替え: ソフトウェアは現在の状態を保存する。

- ISR 実行: ハンドラが実行される。

- コンテキストの復元: ソフトウェアは以前のタスクを再開する。

このシーケンスをモデル化することで、エンジニアはリアルタイムシステムにとって重要な指標である最悪ケース遅延を計算できる。

📊 時刻制約の分析

制約は図を支配するルールである。設計が性能要件を満たすことを保証する。これらはしばしば不等式または特定の時間窓として表現される。

セットアップ時間とホールド時間

同期システムでは、データはクロックエッジの前後で安定している必要がある。時刻図はこれらの窓を明示的に示す。

| 制約の種類 | 説明 | 設計への影響 |

|---|---|---|

| セットアップ時間 | データはクロックエッジの前に安定している必要がある時間。 | 遅いクロックまたは高速なハードウェアを必要とする。 |

| ホールド時間 | データはクロックエッジの後に安定したまま維持される必要がある時間。 | バッファリングまたは遅いクロックを必要とする。 |

| 伝播遅延 | 信号が送信元から受信先まで到達するまでの時間。 | 最大クロック周波数に影響する。 |

ジッターとばらつき

すべてのイベントが正確に同じ時刻に発生するわけではない。ジッターとは信号のタイミングのばらつきを指す。図では、しばしば陰影付き領域や可能なエッジの範囲として示される。

- 高ジッター:不安定性を示すことが多く、ノイズや電源の問題が原因である。

- 低ジッター:安定した、予測可能なシステムを示す。

インターフェースをモデル化する際、設計者は最悪ケースのジッターを考慮しなければならない。時刻窓がしすぎると、システムは信頼できなくなる。

🛠️ 効果的なモデル化のためのベストプラクティス

図を描くのは簡単ですが、有用な図を描くには自制心が必要です。明確さと実用性を確保するため、これらのガイドラインに従ってください。

- 範囲を明確に定義する:マイクロ秒か秒のどちらをモデル化するかを決定してください。明確なスケーリングなしに、粒度を混ぜてはいけません。

- 信号に明確にラベルを付ける:ハードウェアの回路図と一致する名前を使用してください(例:

INT0,CS_N). - アクティブ領域を表示する:信号が負荷を駆動している場所と、浮遊している場所を強調表示してください。

- エラー状態を含める:タイムアウトが発生した場合の動作を示してください。これによりデバッグが容易になります。

- クロックサイクルに合わせる:システムがクロック駆動の場合、垂直グリッド線をクロックのエッジに合わせて参照してください。

避けたい一般的な落とし穴

レビュー過程での時間を節約するために、これらのミスを避けてください。

- 複雑化しすぎない:必要でない限り、すべての命令サイクルをモデル化しないでください。インターフェースの動作に注目してください。

- 非同期イベントを無視しない:割り込みや外部トリガーはしばしば処理の流れを崩します。それらが表現されていることを確認してください。

- レベルの混同を避ける:同じビュー内で、高レベルのプロトコルタイミングと低レベルの電気信号を混ぜてはいけません。

- 理想的な状態を仮定しない:実際のハードウェアには抵抗と静電容量があります。遅延を現実的にモデル化してください。

🔄 他の図との統合

タイミング図は単独で存在するものではありません。他のUML図と補完し合い、包括的なシステムビューを提供します。

シーケンス図

シーケンス図はメッセージの順序を示します。タイミング図は時間の次元を追加します。流れを定義するためにシーケンス図を使用し、その後タイミング図で重要なメッセージのタイミングを検証してください。

状態機械図

状態機械はオブジェクトの論理を定義します。タイミング図は状態の持続時間を定義します。たとえば、状態機械が「入力を待つ」と言う場合、タイミング図はその待機時間が正確にどのくらいかを示します。

アクティビティ図

アクティビティ図はワークフローを示します。タイミング図は特定のアクティビティに実行時間を注釈するために使用できます。これはパフォーマンス分析に役立ちます。

📡 実世界のシナリオ

これらの図が特定の産業分野にどのように適用されるかを見てみましょう。

1. 自動車システム

自動車電子機器は安全のため厳密なタイミングを必要とします。ブレーキ信号はミリ秒以内にコントローラに到達しなければなりません。タイミング図は、コントローラー・エリア・ネットワーク(CAN)バスがこれらの遅延要件を満たしているかを検証するために使用されます。

- 注目点:レイテンシとジッター。

- 制約:ハードリアルタイム要件。

2. インダストリアルIoT

IoTデバイスはしばしば限られた電力で動作します。タイミング図はスリープサイクルの最適化に役立ちます。ソフトウェアは、必要がある場合にのみハードウェアを起動するようにモデル化でき、電力消費を削減できます。

- 注目点:電力状態遷移。

- 制約:エネルギー効率。

3. 通信

ネットワークプロトコルは正確な同期に依存しています。タイミング図は、長距離にわたるデータの整合性を保証するために、デバイス間のハンドシェイクをモデル化します。

- 注目点:伝播遅延と同期。

- 制約:データスループット。

🔍 検証と検証

図が作成されると、検証が必要です。このプロセスにより、モデルが物理的な実装と一致していることを確認できます。

シミュレーション

シミュレーション環境を使用してタイミング論理をテストします。入力信号を供給し、図と照らし合わせて出力を観察します。不一致は設計上の欠陥を示しています。

静的解析

論理的一貫性について図をレビューします。トリガーなしに状態が変化する信号はありますか?無限に続く待機状態が発生するデッドロックはありますか?

コードレビュー

実装コードと図を比較してください。コードには必要な遅延が含まれていますか?割り込みは正しい優先順位で処理されていますか?図は参照文書として機能します。

📝 ベストプラクティスの要約

ハードウェア・ソフトウェアインターフェースの効果的なモデル化には、両分野に対する深い理解が必要です。タイミング図は必要な明確さを提供します。

- 明確性:ライフラインと信号が明確にラベル付けされていることを確認してください。

- 正確性:正確な時間単位と制約を使用してください。

- 完全性:エラー経路と非同期イベントを含めてください。

- 一貫性:図をコードや回路図と同期させ続けてください。

これらの原則に従うことで、チームは統合リスクを低減し、堅牢なシステム性能を確保できます。モデル化に費やした努力は、デバッグや保守フェーズで実を結びます。

🚀 最終的な考察

組み込みシステムの環境は常に進化しています。デバイスがより複雑になるにつれて、正確なタイミングモデルの必要性が高まっています。UMLタイミング図は、こうした複雑性について標準化された言語を提供します。

次のプロジェクトを開始する際は、まず重要なインターフェースをマッピングすることから始めましょう。タイミングが妥協できない箇所を特定してください。図を使ってハードウェアチームとソフトウェアチームの期待を共有しましょう。この共有された理解により、誤解を防ぎ、開発を加速できます。

図は動的な文書であることを思い出してください。設計が変更されるたびに図を更新してください。新しい制約が追加されたら、モデルに反映させましょう。これにより、製品のライフサイクル全体を通じて文書の正確性と価値が保たれます。

適切なアプローチを取れば、タイミング図は単なる文書以上のものになります。分析のツールとなり、実装のガイドとなり、品質保証の基準となります。その提供する正確性を活かして、信頼性が高く、効率的で、堅牢なシステムを構築しましょう。