El tiempo es el hilo invisible que une el hardware y el software. En sistemas embebidos, microcontroladores y dispositivos IoT, los milisegundos importan. Un retraso de unos pocos microsegundos puede causar un fallo del sistema, un evento de pérdida de datos o un peligro para la seguridad. Para visualizar estas relaciones temporales, los ingenieros recurren aDiagramas de Tiempo de UML. Estos diagramas proporcionan una forma rigurosa de modelar el comportamiento de las señales con el paso del tiempo, asegurando que los componentes de hardware y la lógica de software operen sincronizados.

Modelar interfaces hardware-software requiere precisión. A diferencia de los diagramas de interacción estándar, los diagramas de tiempo se centran en el momento exacto en que las señales cambian de estado. Esta guía explora cómo construir, interpretar y aplicar estos diagramas en escenarios de ingeniería del mundo real. Analizaremos las transiciones de señal, las regiones activas y las restricciones de tiempo sin depender de herramientas específicas.

⚙️ Comprendiendo el Propósito Fundamental

Un diagrama de tiempo de UML es un diagrama de comportamiento que enfatiza las restricciones de tiempo de objetos y señales. Es especialmente útil cuando la corrección de un sistema depende del momento de los eventos, y no solo de la secuencia de mensajes.

- Precisión Temporal: Define cuándo una señal debe subir o bajar.

- Monitoreo de Estado: Rastrea el estado de un objeto durante un intervalo de tiempo específico.

- Verificación de la Interfaz: Valida si el hardware cumple con las expectativas del software.

Al diseñar un controlador embebido, el software envía un comando y el hardware debe responder dentro de una ventana específica. Si el hardware tarda demasiado, el software podría expirar. Si responde demasiado pronto, los datos podrían no ser legibles. Los diagramas de tiempo capturan este baile.

📉 Componentes Clave de un Diagrama de Tiempo

Para construir un diagrama válido, debes entender la sintaxis. La notación está estandarizada, asegurando que cualquier ingeniero pueda leer el modelo.

1. Líneas de vida

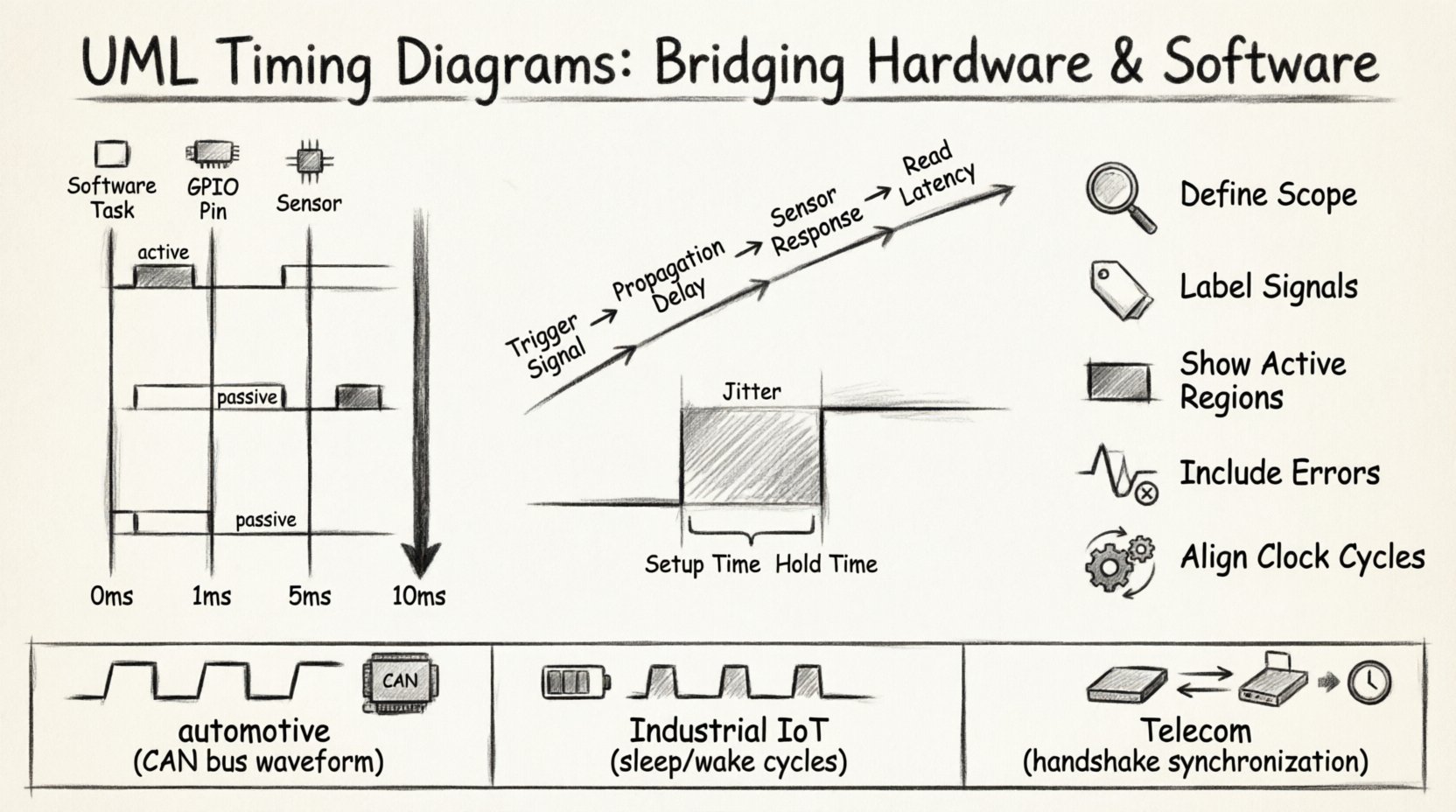

Una línea de vida representa un objeto o una interfaz. En contextos hardware-software, las líneas de vida a menudo corresponden a:

- Tareas de Software: El bucle principal, manejadores de interrupciones o controladores.

- Señales de Hardware: Pines GPIO, líneas de bus (SPI, I2C) o líneas de interrupción.

- Dispositivos Externos: Sensores, actuadores o módulos de comunicación.

Cada línea de vida es una línea vertical que se extiende hacia abajo en el diagrama. El tiempo fluye de arriba hacia abajo.

2. El Eje de Tiempo

A diferencia de los diagramas de secuencia, donde el enfoque está en el orden de los mensajes, los diagramas de tiempo tienen un eje de tiempo explícito. Este puede ser tiempo absoluto (por ejemplo, milisegundos) o tiempo relativo (por ejemplo, ciclos de reloj).

- Tiempo Absoluto:Útil para requisitos a nivel de sistema como «la respuesta debe ocurrir dentro de 50ms».

- Tiempo Relativo: Útil para la lógica interna, como por ejemplo “esperar 3 ciclos de reloj después del inicio”.

3. Estados y valores de las señales

Las señales cambian entre estados definidos. En la lógica digital, estos suelen ser 0 y 1. En el diagrama, se representan mediante barras horizontales en la línea de vida.

- Estado activo: Una barra llena que indica que la señal está alta o activada.

- Estado pasivo: Un espacio vacío o una línea punteada que indica que la señal está baja o desactivada.

- Desconocido: Un signo de interrogación o un símbolo específico cuando el estado no está definido.

4. Valores de las señales

Para señales complejas como buses de datos, el diagrama puede mostrar el valor real que se está transmitiendo. Esto es crucial al modelar protocolos donde patrones específicos de datos desencadenan comportamientos específicos del hardware.

🔌 Modelado de interfaces entre hardware y software

La intersección entre hardware y software es donde ocurren la mayoría de los errores de temporización. El software asume que el hardware se comporta de forma predecible; el hardware responde a las limitaciones físicas. Un diagrama de temporización cierra esta brecha.

Escenario: Control de GPIO y manejo de interrupciones

Considere un sistema en el que un microcontrolador controla un sensor a través de un pin de Entrada/Salida General (GPIO). El software debe leer los datos del sensor inmediatamente después de un disparo.

Los siguientes elementos son críticos:

- Señal de disparo: El software escribe un valor en el GPIO.

- Retardo de propagación: El tiempo que tarda la señal en recorrer el circuito.

- Respuesta del sensor: El tiempo que tarda el sensor en estabilizar los datos.

- Latencia de lectura: El tiempo que tarda la CPU en recuperar los datos.

Un diagrama de temporización visualiza la brecha entre la escritura del software y la lectura del hardware. Si la brecha es demasiado pequeña, la lectura podría fallar. Si la brecha es demasiado grande, el sistema se vuelve ineficiente.

Escenario: Latencia de interrupción

Las interrupciones son eventos asíncronos. El diagrama debe mostrar la transición desde el flujo de ejecución normal hasta la rutina de servicio de interrupción (ISR).

- Activación de interrupción: El pin de hardware se vuelve alto.

- Cambio de contexto: El software guarda el estado actual.

- Ejecución de ISR: El manejador se ejecuta.

- Restauración de contexto: El software reanuda la tarea anterior.

Modelar esta secuencia ayuda a los ingenieros a calcular la latencia peor caso, una métrica crítica para los sistemas en tiempo real.

📊 Análisis de las restricciones de tiempo

Las restricciones son las reglas que rigen el diagrama. Garantizan que el diseño cumpla con los requisitos de rendimiento. A menudo se expresan como desigualdades o ventanas de tiempo específicas.

Tiempo de preparación y tiempo de retención

En los sistemas síncronos, los datos deben ser estables antes y después de una transición de reloj. Los diagramas de tiempo muestran explícitamente estas ventanas.

| Tipo de restricción | Descripción | Impacto en el diseño |

|---|---|---|

| Tiempo de preparación | El tiempo en que los datos deben permanecer estables antes de la transición del reloj. | Requiere un reloj más lento o hardware más rápido. |

| Tiempo de retención | El tiempo en que los datos deben permanecer estables después de la transición del reloj. | Requiere amortiguación o un reloj más lento. |

| Retardo de propagación | Tiempo que tarda la señal en viajar desde la fuente hasta el destino. | Afecta la frecuencia máxima del reloj. |

Jitter y variabilidad

No todos los eventos ocurren exactamente al mismo tiempo. El jitter es la variación en el momento de una señal. En un diagrama, esto a menudo se muestra como una región sombreada o un rango de bordes posibles.

- Alto jitter:Indica inestabilidad, a menudo debida a ruido o problemas de alimentación.

- Bajo jitter:Indica un sistema estable y predecible.

Al modelar interfaces, los diseñadores deben tener en cuenta el jitter peor caso. Si la ventana de tiempo es demasiado estrecha, el sistema se vuelve poco confiable.

🛠️ Mejores prácticas para un modelado efectivo

Crear un diagrama es fácil; crear uno útil requiere disciplina. Siga estas pautas para garantizar claridad y utilidad.

- Defina el alcance claramente: Decida si está modelando microsegundos o segundos. No mezcle granularidades sin una escala clara.

- Etiquete las señales explícitamente: Use nombres que coincidan con el esquema de hardware (por ejemplo,

INT0,CS_N). - Muestre las regiones activas: Resalte dónde la señal está conduciendo la carga frente a cuando está flotando.

- Incluya condiciones de error: Muestre lo que sucede si ocurre un tiempo de espera. Esto ayuda en la depuración.

- Alinee con los ciclos de reloj: Si el sistema está relojado, alinee las líneas verticales de la cuadrícula con los bordes del reloj para referencia.

Errores comunes que deben evitarse

Evite estos errores para ahorrar tiempo durante el proceso de revisión.

- Sobrecargar: No modele cada ciclo de instrucción individual a menos que sea necesario. Enfóquese en el comportamiento de la interfaz.

- Ignorar eventos asíncronos: Las interrupciones y los desencadenantes externos a menudo interrumpen el flujo. Asegúrese de que estén representados.

- Mezclar niveles: No mezcle el tiempo de protocolo de alto nivel con la señalización eléctrica de bajo nivel en la misma vista.

- Asumir condiciones ideales: El hardware real tiene resistencia y capacitancia. Modele los retrasos de forma realista.

🔄 Integración con otros diagramas

Los diagramas de tiempo no existen de forma aislada. Complementan otros diagramas UML para proporcionar una visión completa del sistema.

Diagramas de secuencia

Los diagramas de secuencia muestran el orden de los mensajes. Los diagramas de tiempo añaden la dimensión del tiempo. Use un diagrama de secuencia para definir el flujo, y luego use un diagrama de tiempo para validar el tiempo de los mensajes críticos.

Diagramas de máquinas de estado

Las máquinas de estado definen la lógica de un objeto. Los diagramas de tiempo definen la duración de los estados. Por ejemplo, una máquina de estado podría decir «Esperar entrada». El diagrama de tiempo muestra exactamente cuánto dura esa espera.

Diagramas de actividad

Los diagramas de actividad muestran el flujo de trabajo. Los diagramas de tiempo se pueden utilizar para anotar actividades específicas con su tiempo de ejecución. Esto es útil para el análisis de rendimiento.

📡 Escenarios del mundo real

Veamos cómo se aplican estos diagramas a dominios industriales específicos.

1. Sistemas automotrices

Los sistemas electrónicos automotrices requieren un control estricto del tiempo para garantizar la seguridad. Una señal de frenado debe llegar al controlador en menos de un milisegundo. Los diagramas de tiempo se utilizan para verificar que el bus de red de control (CAN) cumpla con estos requisitos de latencia.

- Enfoque:Latencia y jitter.

- Restricción:Requisitos de tiempo real estricto.

2. IoT industrial

Los dispositivos IoT a menudo operan con energía limitada. Los diagramas de tiempo ayudan a optimizar los ciclos de suspensión. El software puede modelarse para activar el hardware solo cuando sea necesario, reduciendo el consumo de energía.

- Enfoque:Transiciones de estado de energía.

- Restricción:Eficiencia energética.

3. Telecomunicaciones

Los protocolos de red dependen de una sincronización precisa. Los diagramas de tiempo modelan el intercambio de señales entre dispositivos para garantizar la integridad de los datos a grandes distancias.

- Enfoque:Retardo de propagación y sincronización.

- Restricción:Rendimiento de datos.

🔍 Verificación y validación

Una vez creado el diagrama, debe validarse. Este proceso garantiza que el modelo coincida con la implementación física.

Simulación

Utilice entornos de simulación para probar la lógica de tiempo. Ingrese señales de entrada y observe la salida en comparación con el diagrama. Las discrepancias indican fallos en el diseño.

Análisis estático

Revise el diagrama para asegurar coherencia lógica. ¿Hay señales que cambien de estado sin un desencadenante? ¿Existen bloqueos donde un estado de espera dure indefinidamente?

Revisión de código

Compare el código de implementación con el diagrama. ¿El código incluye los retrasos necesarios? ¿Maneja las interrupciones con la prioridad correcta? El diagrama sirve como documento de referencia.

📝 Resumen de Prácticas

Una modelización eficaz de las interfaces hardware-software requiere un profundo conocimiento de ambos dominios. Los diagramas de tiempo proporcionan la claridad necesaria.

- Claridad: Asegúrese de que las líneas de vida y las señales estén claramente etiquetadas.

- Precisión: Utilice unidades de tiempo y restricciones precisas.

- Completitud: Incluya rutas de error y eventos asíncronos.

- Consistencia: Mantenga el diagrama sincronizado con el código y los esquemáticos.

Al adherirse a estos principios, los equipos pueden reducir los riesgos de integración y garantizar un rendimiento robusto del sistema. La inversión realizada en la modelización se ve recompensada durante las fases de depuración y mantenimiento.

🚀 Consideraciones Finales

El panorama de los sistemas embebidos sigue evolucionando. A medida que los dispositivos se vuelven más complejos, aumenta la necesidad de modelos de tiempo precisos. Los diagramas de tiempo de UML ofrecen un lenguaje estandarizado para discutir estas complejidades.

Cuando comience su próximo proyecto, comience por mapear las interfaces críticas. Identifique dónde el tiempo es irrenunciable. Utilice el diagrama para establecer expectativas para el equipo de hardware y el equipo de software. Esta comprensión compartida previene malentendidos y acelera el desarrollo.

Recuerde que un diagrama es un documento vivo. Actualícelo conforme cambie el diseño. Si se añade una nueva restricción, reflejéela en el modelo. Esto mantiene la documentación precisa y valiosa durante todo el ciclo de vida del producto.

Con el enfoque adecuado, los diagramas de tiempo dejan de ser solo documentación. Se convierten en una herramienta de análisis, una guía para la implementación y un estándar para la garantía de calidad. Aproveche la precisión que ofrecen para construir sistemas confiables, eficientes y robustos.