时间是连接硬件与软件的无形纽带。在嵌入式系统、微控制器和物联网设备中,毫秒级的差异至关重要。几微秒的延迟就可能导致系统故障、数据丢失事件或安全风险。为了可视化这些时间关系,工程师们会借助UML时序图。这些图表提供了一种严谨的方法来建模信号随时间的行为,确保硬件组件与软件逻辑保持同步。

建模软硬件接口需要精确性。与标准交互图不同,时序图关注的是信号状态变化的确切时刻。本指南探讨如何构建、解读并应用这些图表于实际工程场景中。我们将不依赖特定工具,分析信号转换、活跃区域和时间约束。

⚙️ 理解核心目的

UML时序图是一种行为图,强调对象和信号的时间约束。当系统的正确性取决于事件发生的时间而非消息的顺序时,它尤其有用。

- 时间准确性: 它定义了信号必须上升或下降的时间点。

- 状态监控: 它跟踪对象在特定时间区间内的状态。

- 接口验证: 它验证硬件是否满足软件的预期。

在设计嵌入式控制器时,软件发送一个命令,硬件必须在特定时间窗口内响应。如果硬件响应过慢,软件可能会超时;如果响应过早,数据可能无法读取。时序图捕捉到了这种微妙的交互。

📉 时序图的关键组成部分

要构建有效的图表,必须理解其语法。符号是标准化的,确保任何工程师都能读懂该模型。

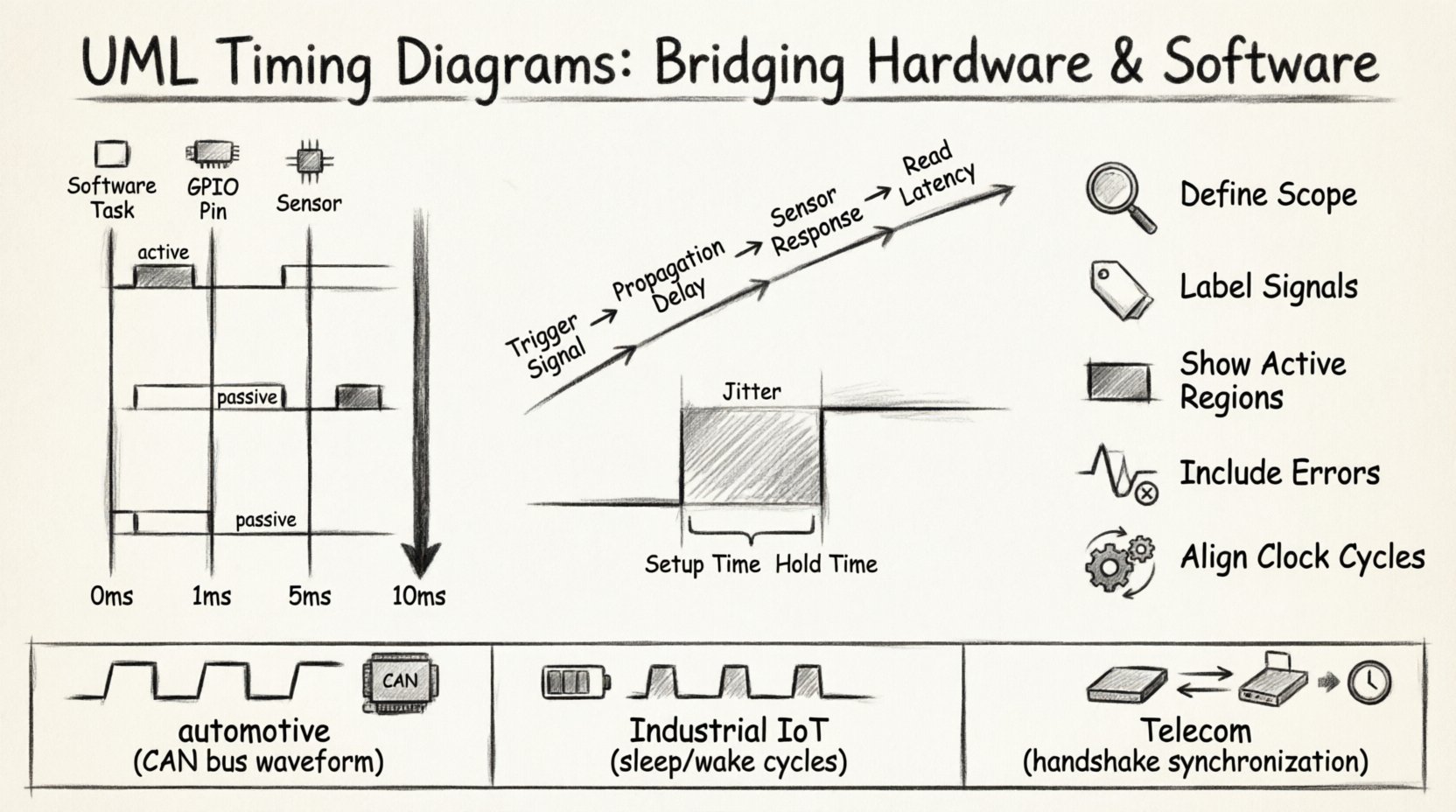

1. 生命线

生命线代表一个对象或接口。在软硬件上下文中,生命线通常对应:

- 软件任务: 主循环、中断处理程序或驱动程序。

- 硬件信号: GPIO引脚、总线线路(SPI、I2C)或中断线路。

- 外部设备: 传感器、执行器或通信模块。

每条生命线都是从图中向上延伸的垂直线。时间从上到下流动。

2. 时间轴

与侧重消息顺序的序列图不同,时序图具有明确的时间轴。它可以是绝对时间(例如毫秒)或相对时间(例如时钟周期)。

- 绝对时间: 适用于系统级需求,例如“响应必须在50毫秒内发生”。

- 相对时间: 用于内部逻辑,例如“启动后等待3个时钟周期”。

3. 信号状态和值

信号在定义的状态之间变化。在数字逻辑中,这些通常是0和1。在图中,这些状态由生命线上的水平条表示。

- 活动状态: 实心条表示信号处于高电平或有效状态。

- 静默状态: 空白区域或虚线表示信号处于低电平或无效状态。

- 未知: 当状态未定义时,使用问号或特定符号表示。

4. 信号值

对于复杂信号(如数据总线),图中可能显示实际传输的值。在建模协议时,这一点至关重要,因为特定的数据模式会触发特定的硬件行为。

🔌 建模软硬件接口

硬件与软件的交汇处是大多数时序错误发生的地方。软件假设硬件行为可预测;而硬件则对物理限制做出反应。时序图正是弥合这一差距的工具。

场景:GPIO 控制与中断处理

考虑一个系统,其中微控制器通过通用输入/输出(GPIO)引脚控制传感器。软件必须在触发后立即读取传感器数据。

以下要素至关重要:

- 触发信号: 软件向GPIO写入一个值。

- 传播延迟: 信号在电路中传播所需的时间。

- 传感器响应: 传感器稳定数据所需的时间。

- 读取延迟: CPU 获取数据所需的时间。

时序图展示了软件写入与硬件读取之间的间隔。如果间隔过小,读取可能失败;如果间隔过大,系统效率会降低。

场景:中断延迟

中断是异步事件。图中必须显示从正常执行流程到中断服务例程(ISR)的转换。

- 中断置位: 硬件引脚变为高电平。

- 上下文切换: 软件保存当前状态。

- ISR 执行: 处理程序运行。

- 上下文恢复: 软件恢复先前的任务。

对此序列进行建模有助于工程师计算最坏情况下的延迟,这是实时系统中的一个关键指标。

📊 分析时序约束

约束是控制图表的规则。它们确保设计满足性能要求。这些通常以不等式或特定时间窗口的形式表达。

建立时间和保持时间

在同步系统中,数据必须在时钟边沿之前和之后保持稳定。时序图明确显示这些窗口。

| 约束类型 | 描述 | 对设计的影响 |

|---|---|---|

| 建立时间 | 数据必须在时钟边沿之前保持稳定。 | 需要更慢的时钟或更快的硬件。 |

| 保持时间 | 数据必须在时钟边沿之后保持稳定。 | 需要缓冲或更慢的时钟。 |

| 传播延迟 | 信号从源到目的地传播所需的时间。 | 影响最大时钟频率。 |

抖动和变化性

并非所有事件都在完全相同的时间发生。抖动是信号时序的变化。在图表中,这通常以阴影区域或可能边沿的范围来表示。

- 高抖动: 表示不稳定,通常由噪声或电源问题引起。

- 低抖动: 表示一个稳定且可预测的系统。

在建模接口时,设计师必须考虑最坏情况下的抖动。如果时序窗口太窄,系统将变得不可靠。

🛠️ 有效建模的最佳实践

创建一个图表很容易;但创建一个有用的图表则需要纪律。遵循这些指南以确保清晰性和实用性。

- 明确界定范围: 决定你是在建模微秒还是秒。除非有明确的缩放,否则不要混合不同粒度。

- 明确标注信号: 使用与硬件原理图匹配的名称(例如,

INT0,CS_N). - 显示有效区域: 突出显示信号驱动负载的时段与信号浮空的时段。

- 包含错误条件: 显示超时发生时的情况。这有助于调试。

- 与时钟周期对齐: 如果系统是时钟驱动的,将垂直网格线与时钟边沿对齐以作参考。

应避免的常见陷阱

避免这些错误,以节省评审过程中的时间。

- 过度复杂化: 除非必要,否则不要建模每一个指令周期。应聚焦于接口行为。

- 忽略异步事件: 中断和外部触发通常会打断流程。确保它们被正确表示。

- 混用层级: 不要在同一视图中混用高层协议时序与底层电气信号。

- 假设理想条件: 实际硬件具有电阻和电容。应现实地建模延迟。

🔄 与其他图表的集成

时序图并非孤立存在。它们与其他UML图相辅相成,以提供完整的系统视图。

顺序图

顺序图显示消息的顺序。时序图增加了时间维度。先使用顺序图定义流程,再使用时序图验证关键消息的时序。

状态机图

状态机定义了对象的逻辑。时序图定义了状态的持续时间。例如,状态机可能表示“等待输入”。时序图会精确显示等待的时间长度。

活动图

活动图展示了工作流程。时序图可用于标注特定活动的执行时间。这对性能分析很有帮助。

📡 现实世界场景

让我们看看这些图表如何应用于特定的行业领域。

1. 汽车系统

汽车电子系统为了安全需要严格的时序控制。制动信号必须在毫秒内到达控制器。时序图用于验证控制器局域网(CAN)总线是否满足这些延迟要求。

- 关注点:延迟和抖动。

- 约束条件:硬实时要求。

2. 工业物联网

物联网设备通常在有限电源下运行。时序图有助于优化睡眠周期。软件可以建模为仅在必要时唤醒硬件,从而降低功耗。

- 关注点:电源状态转换。

- 约束条件:能效。

3. 电信

网络协议依赖于精确的同步。时序图用于建模设备之间的握手过程,以确保远距离传输中的数据完整性。

- 关注点:传播延迟和同步。

- 约束条件:数据吞吐量。

🔍 验证与确认

一旦图表创建完成,就必须进行验证。该过程确保模型与实际实现相匹配。

仿真

使用仿真环境来测试时序逻辑。输入信号并根据图表观察输出结果。不一致之处表明存在设计缺陷。

静态分析

检查图表的逻辑一致性。是否存在没有触发信号就改变状态的信号?是否存在等待状态无限持续的死锁情况?

代码审查

将实现代码与图表进行对比。代码是否包含了必要的延时?它是否以正确的优先级处理了中断?该图表作为参考文档。

📝 实践总结

有效建模软硬件接口需要对两个领域都有深入的理解。时序图提供了必要的清晰度。

- 清晰性: 确保生命线和信号被清晰地标记。

- 精确性: 使用准确的时间单位和约束条件。

- 完整性: 包含错误路径和异步事件。

- 一致性: 保持图表与代码和原理图同步。

遵循这些原则,团队可以降低集成风险并确保系统的稳健性能。建模所投入的努力在调试和维护阶段将得到回报。

🚀 最终思考

嵌入式系统的格局持续演变。随着设备变得越来越复杂,对精确时序模型的需求也在增加。UML时序图提供了一种标准化的语言来讨论这些复杂性。

当你开始下一个项目时,应从映射关键接口开始。识别出时序不可妥协的环节。使用图表来为硬件团队和软件团队设定预期。这种共同的理解可以防止误解并加速开发进程。

请记住,图表是一个动态文档。随着设计的变更及时更新它。如果新增了约束条件,应在模型中体现出来。这能确保文档在整个产品生命周期中保持准确和有价值。

采用正确的方法,时序图就不仅仅是文档了。它们成为分析工具、实施指南和质量保证的标准。拥抱它们所提供的精确性,以构建可靠、高效且稳健的系统。