Merancang sistem waktu nyata membutuhkan ketepatan. Ketika sinyal harus tiba dalam jendela tertentu, dan perubahan keadaan harus terjadi secara terduga, pemodelan standar sering kali tidak mencukupi. Anda sedang menangani logika yang tidak hanya mengalir; ia berdenyut, menunggu, dan berakhir. Dalam lingkungan ini, memilih notasi Bahasa Pemodelan Terpadu (UML) yang tepat bukan sekadar pilihan gaya. Ini adalah keputusan teknik kritis yang memengaruhi kebenaran sistem.

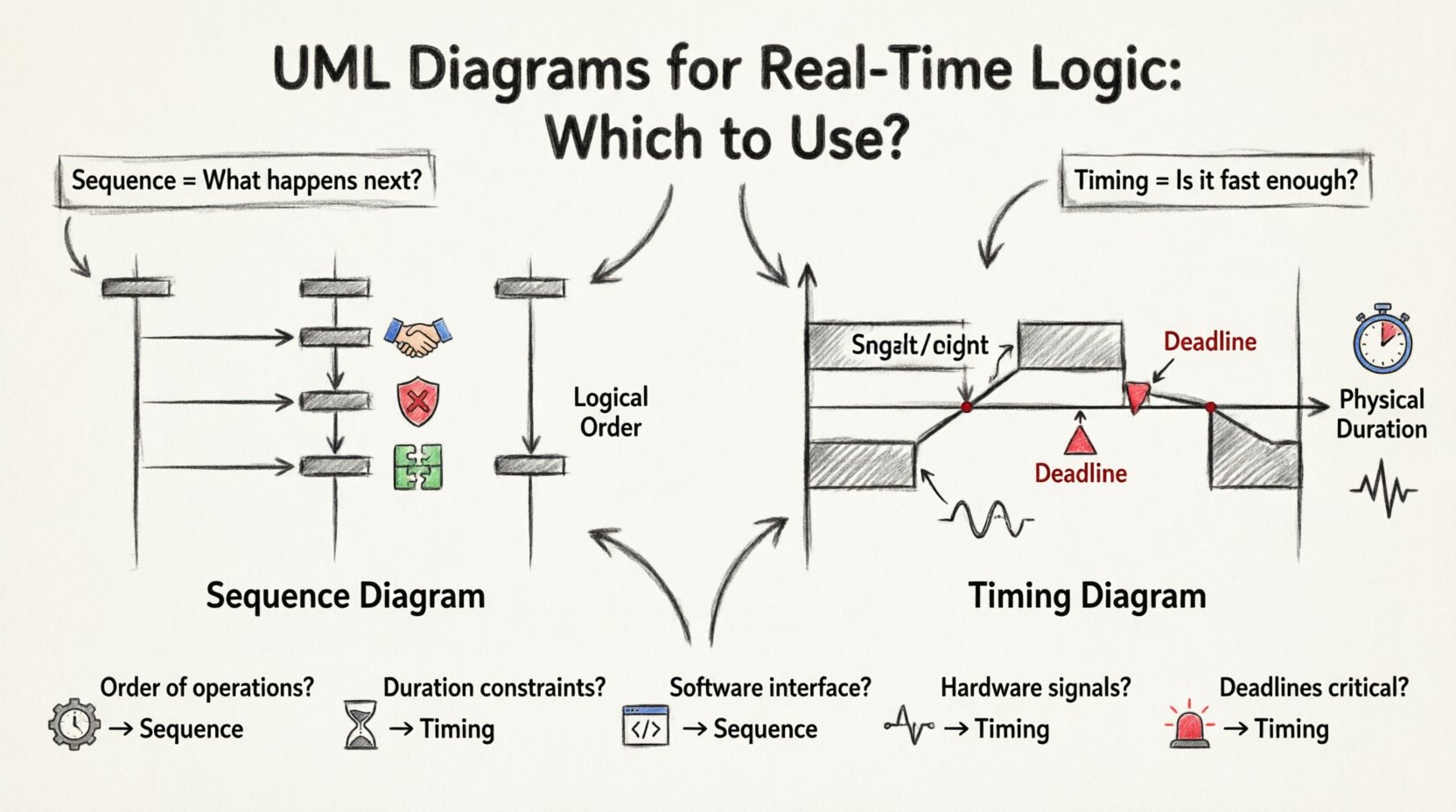

Dua jenis diagram utama mendominasi diskusi mengenai pemodelan interaksi: Diagram Urutan UML dan Diagram Waktu UML. Keduanya memvisualisasikan perilaku, namun menangkap dimensi yang berbeda dari kenyataan sistem. Satu fokus pada urutan pesan; yang lain fokus pada durasi dan keadaan objek sepanjang waktu.

Panduan ini menyediakan perbandingan teknis mendalam. Kami akan menganalisis bagaimana setiap diagram menangani sinkronisasi, latensi, dan batasan keadaan. Pada akhirnya, Anda akan memahami secara tepat kapan harus menggunakan diagram waktu dibandingkan diagram urutan untuk arsitektur logika waktu nyata Anda.

📡 Memahami Diagram Urutan dalam Konteks Waktu Nyata

Diagram Urutan UML adalah standar industri untuk memvisualisasikan urutan interaksi. Diagram ini memetakan bagaimana objek berkomunikasi sepanjang waktu, dengan mengatur objek secara vertikal dan pesan secara horizontal. Dalam konteks logika waktu nyata, diagram ini unggul dalam mendefinisikan aliran logis daripada durasi fisik.

- Fokus:Pengiriman pesan dan aliran kontrol.

- Sumbu Waktu:Implisit. Waktu mengalir dari atas ke bawah, tetapi skala tidak didefinisikan.

- Elemen Kunci:Lifeline, batang aktivasi, pesan (sinkron/asinkron), dan nilai kembali.

- Terbaik Digunakan Untuk:Mendefinisikan algoritma, protokol handshaking, dan urutan operasi.

Ketika memodelkan sistem waktu nyata, diagram urutan menjawab pertanyaan: “Apa yang terjadi selanjutnya?”Ini sangat berharga untuk mendiagnosis kondisi persaingan yang bergantung pada urutan eksekusi, bukan kecepatan eksekusi.

Komponen Kunci Diagram Urutan

Untuk menggunakan alat ini secara efektif, Anda harus memahami kosakata strukturnya:

- Lifeline:Mewakili contoh kelas atau komponen. Dalam sistem waktu nyata, ini sering mewakili sensor, pengendali, atau bus komunikasi.

- Batas Aktivasi: Tampilkan saat suatu objek sedang melakukan suatu tindakan. Ini menunjukkan transfer kendali.

- Pesan Sinkron:Digambarkan dengan panah padat. Pengirim menunggu respons sebelum melanjutkan. Ini sangat penting untuk logika yang memblokir.

- Pesan Asinkron:Digambarkan dengan panah terbuka. Pengirim melanjutkan segera. Ini memodelkan skenario fire-and-forget yang umum dalam arsitektur berbasis peristiwa.

- Fragmen Gabungan:Kotak seperti

alt,opt, danloopmemungkinkan Anda memodelkan logika bersyarat dan iterasi tanpa membuat diagram menjadi berantakan.

⏱️ Memahami Diagram Waktu dalam Konteks Waktu Nyata

Diagram Waktu UML sering diabaikan, namun merupakan alat utama untuk memodelkan perilaku yang kritis terhadap waktu. Berbeda dengan diagram urutan yang menyederhanakan waktu, diagram waktu memperlakukan waktu sebagai sumbu utama. Diagram ini menunjukkan bagaimana keadaan suatu objek berubah sepanjang timeline tertentu.

- Fokus:Perubahan keadaan dan nilai sinyal sepanjang waktu.

- Sumbu Waktu:Jelas. Berjalan secara horizontal di bagian atas diagram.

- Elemen Kunci:Mesin keadaan, rentang nilai, transisi sinyal, dan batas waktu.

- Paling Cocok Untuk:Menentukan batasan latensi, analisis jitter, dan jendela validitas keadaan.

Dalam logika waktu nyata, diagram waktu menjawab pertanyaan: “Apakah ini terjadi cukup cepat, dan selama berapa lama?”Ini sangat penting ketika sistem harus merespons input sensor dalam waktu 5 milidetik atau mempertahankan tegangan sinyal di atas ambang batas selama durasi tertentu.

Komponen Kunci dari Diagram Waktu

Menguasai diagram ini membutuhkan perhatian terhadap mekanisme temporalnya:

- Skala Waktu:Sumbu horizontal mewakili waktu. Dapat bersifat absolut (waktu jam) atau relatif (waktu yang telah berlalu).

- Batasan Status:Batasan horizontal menunjukkan status suatu objek (misalnya, Aktif, Tidur, Kesalahan). Panjang batasan mewakili durasi.

- Rentang Nilai:Alih-alih pesan diskret, seringkali Anda melihat rentang nilai (misalnya, Tegangan: 0V hingga 5V). Ini sangat penting untuk sistem fisik.

- Transisi Sinyal:Garis vertikal yang melintasi batasan status menunjukkan perubahan nilai atau status.

- Kendala:Kotak teks atau anotasi dapat menentukan batas waktu keras (misalnya,

<batas waktu>).

🆚 Perbedaan Utama: Perbandingan Teknis

Untuk membuat keputusan yang tepat, kita harus melihat perbedaan struktural dan semantik antara dua notasi ini. Tabel berikut menjelaskan perbedaan yang relevan terhadap desain sistem waktu nyata.

| Fitur | Diagram Urutan | Diagram Waktu |

|---|---|---|

| Representasi Waktu | Urutan logis (Atas ke Bawah) | Durasi fisik (Sumbu Horizontal) |

| Fokus Utama | Aliran interaksi dan kontrol | Evolusi status dan nilai sinyal |

| Pesan vs. Status | Berfokus pada pengiriman pesan | Berfokus pada perubahan status dan nilai |

| Kongurensi | Menunjukkan garis hidup paralel dengan jelas | Menunjukkan aktivitas paralel seiring waktu |

| Batas Waktu | Disiratkan melalui urutan pesan | Jelas melalui skala waktu dan kendala |

| Kompleksitas | Beban kognitif tinggi untuk rantai panjang | Beberapa beban kognitif untuk banyak sinyal |

🛠️ Kapan Menggunakan Diagram Urutan untuk Logika Waktu Nyata

Meskipun diagram waktu unggul dalam presisi temporal, diagram urutan tetap menjadi dasar pemodelan interaksi. Anda sebaiknya memprioritaskan diagram urutan ketika:

- Definisi Protokol: Anda sedang mendefinisikan protokol komunikasi (misalnya, MQTT, handshake TCP/IP). Urutan paket SYN, ACK, dan FIN lebih penting daripada penundaan milidetik yang tepat.

- Penanganan Kesalahan: Anda perlu memvisualisasikan bagaimana sistem bereaksi terhadap kegagalan. Bagaimana kontroler mencoba ulang permintaan? Bagaimana ia memberi tahu pengguna? Diagram urutan menangani logika bercabang (fragmen alt/opt) dengan lebih baik.

- Integrasi Komponen: Anda sedang memetakan interaksi antara modul perangkat lunak yang berbeda. Siapa yang memanggil siapa, dan data apa yang dikirim?

- Logika Algoritma: Kompleksitas inti terletak pada pohon keputusan, bukan pada waktu eksekusi. Jika logikanya adalah

if (x > 5) maka lakukan_y, diagram urutan menangkap alur ini dengan jelas. - Kejadian Asinkron:Sistem waktu nyata sering mengandalkan interupsi. Diagram urutan sangat baik untuk menunjukkan terjadinya interupsi saat loop utama sedang berjalan, selama Anda menggunakan fragmen gabungan.

Adegan Contoh: Sistem rem otomatis menerima masukan dari sensor. Diagram urutan akan menunjukkan sensor mengirim data ke kontroler, kontroler memproses masukan, lalu mengirim perintah ke aktuator rem. Ini memetakan ketergantungan logis.

🕒 Kapan Menggunakan Diagram Waktu untuk Logika Waktu Nyata

Diagram waktu menjadi wajib ketika waktu itu sendiri merupakan variabel dalam logika. Anda sebaiknya beralih ke notasi ini ketika:

- Kadaluarsa Keras Ada: Jika suatu tugas harus selesai dalam waktu 10ms, atau sistem akan gagal, diagram waktu memvisualisasikan jendela tersebut. Anda dapat secara eksplisit menggambar garis vertikal yang menandai batas waktu.

- Stabilitas Sinyal Penting: Dalam sistem tertanam, sinyal sering kali perlu tetap tinggi selama durasi tertentu agar dapat dikenali. Diagram waktu menunjukkan persyaratan lebar pulsa.

- Analisis Jitter: Jika sistem harus menangani penundaan variabel (jitter), diagram waktu dapat menunjukkan rentang waktu kedatangan yang mungkin untuk suatu pesan.

- Persaingan Sumber Daya: Ketika dua proses bersaing untuk inti CPU, diagram waktu dapat menunjukkan celah penjadwalan dan bagaimana satu tugas menghalangi yang lain.

- Transisi Mesin Status Jika suatu perangkat harus menunggu dalam status ‘Pemanasan’ selama 5 detik sebelum memasuki mode ‘Aktif’, maka durasi tersebut merupakan batasan kritis. Diagram waktu membuat hal ini menjadi jelas.

Skenario Contoh:Sebuah sensor suhu mengirim data setiap 100ms. Kontroler harus memproses data ini sebelum pembacaan berikutnya tiba. Diagram waktu menunjukkan tumpang tindih (atau ketiadaannya) antara interval pembacaan dan durasi pemrosesan.

🔍 Penjelasan Mendalam: Menangani Konkurensi dan Sinkronisasi

Logika waktu nyata jarang bersifat linier. Konkurensi adalah hal yang biasa. Kedua jenis diagram menangani hal ini secara berbeda, dan memahami perbedaan halus ini sangat penting untuk arsitektur.

Konkurensi dalam Diagram Urutan

Diagram urutan menggunakan garis hidup paralel untuk menunjukkan konkurensi. Jika dua objek aktif secara bersamaan, batang aktivasi mereka berjalan berdampingan. Namun, hal ini tidak menjamin eksekusi bersamaan dalam waktu. Hanya menjamin interlacing logis.

- Keterbatasan:Anda tidak dapat dengan mudah menunjukkan bahwa Proses A harus selesai sebelum Proses B dimulai, terlepas dari urutan, jika keduanya berada pada thread yang berbeda.

- Praktik Terbaik: Gunakan

parfragmen untuk menandai blok eksekusi paralel. Ini menjelaskan bahwa sistem mengharapkan beberapa thread atau proses berjalan secara bersamaan.

Konkurensi dalam Diagram Waktu

Diagram waktu menangani konkurensi secara spasial. Karena waktu mengalir secara horizontal, Anda dapat menumpuk beberapa garis hidup dan melihat secara tepat di mana mereka tumpang tindih dalam waktu.

- Keunggulan:Anda dapat melihat apakah loop ‘Busy Wait’ benar-benar memblokir tugas lain. Anda dapat memvisualisasikan jeda antara suatu tugas dimulai dan tugas lain berakhir.

- Keterbatasan:Mereka dapat menjadi kusut dengan cepat jika Anda memiliki banyak thread konkuren. Kebisingan visual meningkat seiring bertambahnya jumlah sinyal.

🧩 Mengintegrasikan Kedua Diagram

Dalam rekayasa yang kuat, Anda jarang memilih satu dan membuang yang lain. Strategi dokumentasi yang paling efektif mengintegrasikan keduanya. Mereka memainkan peran saling melengkapi dalam siklus desain.

- Desain Tingkat Tinggi: Mulai dengan Diagram Urutanuntuk mendefinisikan arsitektur, alur pesan, dan batas komponen. Ini menetapkan kontrak logis.

- Spesifikasi Tingkat Rendah:Haluskan jalur kritis dengan Diagram Waktu. Setelah logika ditentukan, terapkan batasan temporal pada bagian-bagian kritis. Ini menentukan kontrak kinerja.

- Verifikasi: Selama pengujian, gunakan diagram waktu untuk memverifikasi latensi. Gunakan diagram urutan untuk memverifikasi bahwa pesan yang benar telah ditukar dalam urutan yang benar.

⚠️ Kesalahan Umum yang Harus Dihindari

Bahkan arsitek berpengalaman membuat kesalahan saat memodelkan sistem waktu nyata. Tetap waspada terhadap kesalahan umum ini.

- Mengasumsikan Urutan Menunjukkan Durasi: Kesalahan umum adalah melihat diagram urutan dan mengasumsikan jarak vertikal antar pesan mewakili waktu. Ini tidak benar. Hal ini menyebabkan asumsi latensi yang salah.

- Mengabaikan Status Idle: Dalam diagram waktu, gagal merepresentasikan status ‘Idle’ atau ‘Sleep’ dapat menyembunyikan masalah konsumsi daya. Pastikan batang status Anda mencakup seluruh siklus hidup.

- Terlalu Banyak Menggunakan Fragmen Gabungan: Dalam diagram urutan, terlalu banyak bersarang

altatauoptblok membuat diagram menjadi tidak dapat dibaca. Pisahkan logika kompleks menjadi sub-diagram. - Mencampur Waktu Logis dan Fisik: Jangan mencampur urutan logis (urutan) dengan batasan waktu fisik (waktu) dalam diagram yang sama kecuali diberi label jelas. Pisahkan keduanya untuk menghindari kebingungan.

- Mengabaikan Gangguan Sinyal: Dalam diagram waktu untuk perangkat keras fisik, jangan mengasumsikan transisi sinyal yang sempurna. Tunjukkan margin gangguan atau waktu debounce jika memengaruhi logika.

📝 Praktik Terbaik untuk Dokumentasi

Untuk memastikan diagram Anda menambah nilai daripada menjadi kusut, ikuti panduan ini.

- Penamaan Konsisten: Gunakan konvensi penamaan yang konsisten untuk lifeline dan sinyal. Jika Anda menyebut sinyal ‘ReadSensor’ di satu diagram, jangan menyebutnya ‘GetData’ di diagram lain.

- Fokus pada Jalur Kritis: Jangan mencoba menggambarkan setiap fungsi secara individual. Fokus pada jalur yang melibatkan batasan waktu atau kegagalan kritis. Dokumentasikan jalur normal secara singkat, tetapi jelaskan secara rinci kasus-kasus batas.

- Gunakan Anotasi: Kedua jenis diagram mendukung anotasi. Gunakan anotasi untuk menentukan satuan (ms, µs), toleransi, dan persyaratan khusus. Angka tanpa satuan tidak memiliki makna dalam desain waktu nyata.

- Kontrol Versi: Anggap diagram sebagai kode. Simpan di kontrol versi. Perubahan pada batasan waktu harus direview seperti perubahan kode.

- Ulas dengan Pihak Terkait: Ulas diagram urutan dengan pengembang (logika). Ulas diagram waktu dengan insinyur sistem (kinerja). Pastikan audiens sesuai dengan jenis diagram.

🚀 Pertimbangan Lanjutan: Mesin Status

Sistem waktu nyata sering didorong oleh peristiwa. Ini membawa kita ke persimpangan antara Mesin Status dan diagram UML.

- Diagram Urutan + Mesin Status:Gunakan diagram urutan untuk menunjukkan bagaimana transisi mesin status dipicu oleh pesan eksternal. Tunjukkan pesan yang masuk ke jalur hidup dan perubahan status internal yang terjadi.

- Diagram Waktu + Mesin Status:Gunakan diagram waktu untuk menunjukkan durasi suatu status. Misalnya, status “Timeout” mungkin berlangsung tepat 3 detik. Diagram waktu memvisualisasikan durasi ini relatif terhadap peristiwa lain.

Ketika memodelkan logika bawaan yang kompleks, menggabungkan diagram Mesin Status dengan diagram Waktu sering kali merupakan representasi paling akurat dari perilaku seiring waktu.

📊 Ringkasan Faktor Keputusan

Untuk membantu proses pengambilan keputusan Anda, pertimbangkan daftar periksa ini.

- Apakah perhatian utama adalah urutan operasi? ➝ Gunakan Diagram Urutan.

- Apakah perhatian utama adalah durasi suatu operasi? ➝ Gunakan Diagram Waktu.

- Apakah Anda menentukan antarmuka perangkat lunak? ➝ Gunakan Diagram Urutan.

- Apakah Anda menentukan persyaratan sinyal perangkat keras? ➝ Gunakan Diagram Waktu.

- Apakah logika bergantung pada tenggat waktu? ➝ Gunakan Diagram Waktu.

- Apakah logika bergantung pada protokol pesan? ➝ Gunakan Diagram Urutan.

🔚 Pikiran Akhir

Memilih antara Diagram Waktu UML dan Diagram Urutan bukan tentang preferensi; tetapi tentang kesetiaan terhadap batasan sistem. Diagram urutan memetakan logika interaksi. Diagram waktu memetakan fisika eksekusi.

Di ranah logika waktu nyata, ambiguitas adalah musuh. Dengan memilih alat yang tepat, Anda mengurangi ambiguitas. Anda memberikan kepada tim Anda gambaran jelas yang membedakan antara apa yang dilakukan sistem dan kapan sistem harus melakukannya. Kejelasan ini langsung berubah menjadi sistem yang kuat, andal, dan aman.

Mulai dengan alur. Validasi waktu. Dokumentasikan keduanya. Pendekatan ganda ini menjamin bahwa logika waktu nyata Anda tidak hanya benar secara fungsional tetapi juga benar secara waktu.