设计实时系统需要精确性。当信号必须在特定时间窗口内到达,且状态变化必须可预测时,标准建模方法往往力不从心。你面对的逻辑不仅仅是流动的;它会脉冲、等待并超时。在这种背景下,选择合适的统一建模语言(UML)表示法不仅仅是风格上的选择,而是一个影响系统正确性的关键工程决策。

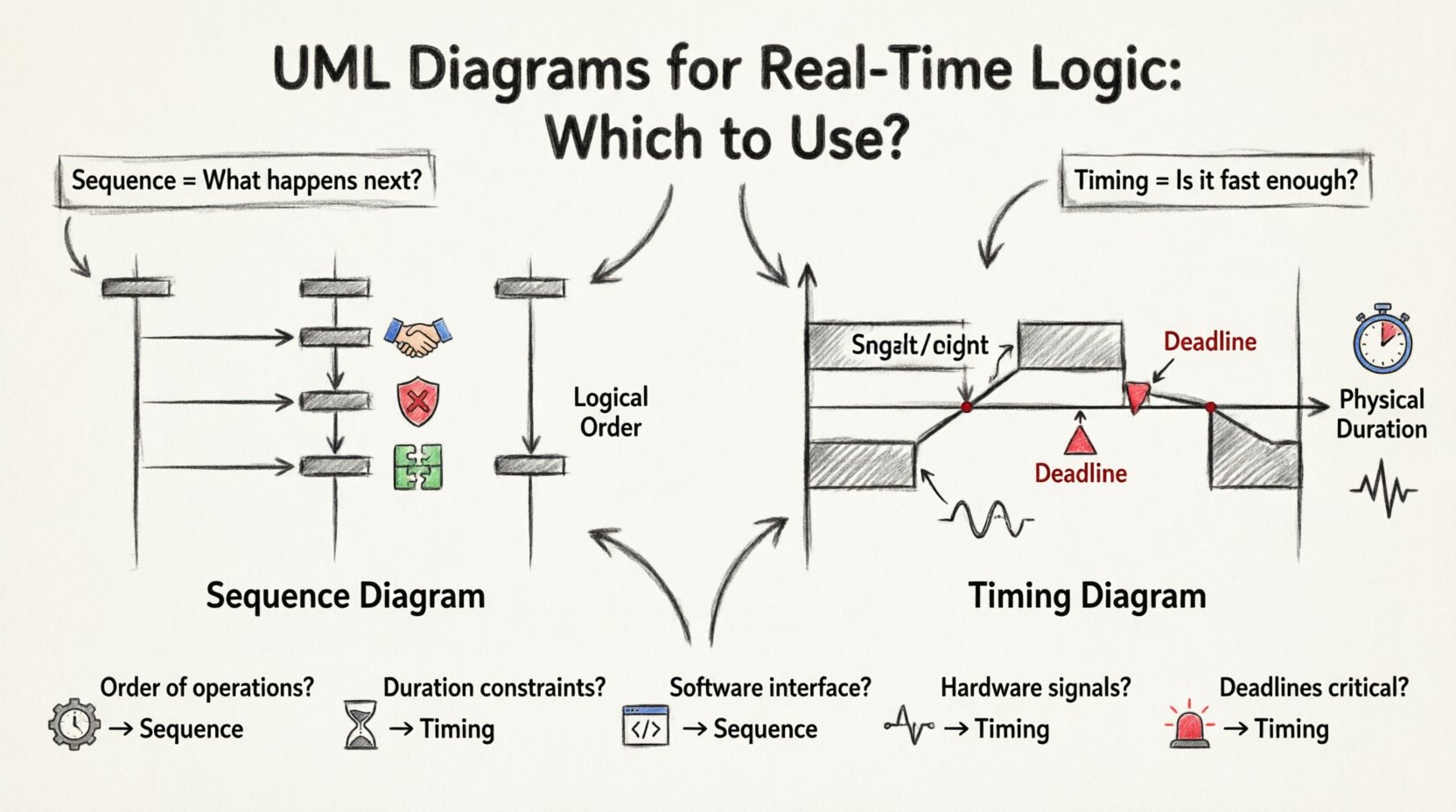

在交互建模讨论中,两种主要的图类型占据主导地位:UML序列图以及UML时序图两者都能可视化行为,但它们捕捉的是系统现实的不同维度。一个关注消息的顺序,另一个则关注对象在时间上的持续时间和状态。

本指南提供深入的技术对比。我们将剖析每种图如何处理同步、延迟和状态约束。最终,你将清楚地了解在实时逻辑架构中,何时应使用时序图,何时应使用序列图。

📡 在实时背景中理解序列图

UML序列图是可视化交互顺序的行业标准。它展示了对象随时间的通信方式,将对象垂直排列,消息水平排列。在实时逻辑背景下,它擅长定义逻辑流程而非物理持续时间.

- 关注点:消息传递与控制流。

- 时间轴:隐式。时间从上到下流动,但时间尺度未定义。

- 关键元素:生命线、激活条、消息(同步/异步)以及返回值。

- 最适合:定义算法、握手协议以及操作的顺序。

在建模实时系统时,序列图回答的问题是:“接下来会发生什么?”它对于调试依赖于执行顺序而非执行速度的竞争条件问题极为宝贵。

序列图的关键组件

要有效使用这一工具,你必须理解其结构术语:

- 生命线:表示类或组件的实例。在实时系统中,这些通常代表传感器、控制器或通信总线。

- 激活条: 显示对象执行操作的时刻。这表示控制权的转移。

- 同步消息: 用实心箭头表示。发送方在继续之前会等待响应。这对于阻塞逻辑至关重要。

- 异步消息: 用空心箭头表示。发送方立即继续执行。这模拟了事件驱动架构中常见的“发送即忘”场景。

- 组合片段: 类似于以下的盒子:

alt,opt,以及loop可以在不使图表杂乱的情况下,对条件逻辑和循环进行建模。

⏱️ 在实时环境中理解时序图

UML时序图常常被忽视,但它却是建模时间关键行为的决定性工具。与抽象时间的序列图不同,时序图将时间视为主要轴线。它展示了对象状态在特定时间轴上的变化过程。

- 关注点: 随时间变化的状态转换和信号值。

- 时间轴: 明确的。沿图表顶部水平延伸。

- 关键元素: 状态机、取值范围、信号转换和截止时间。

- 最适合: 定义延迟约束、抖动分析和状态有效窗口。

在实时逻辑中,时序图回答的问题是:“这是否足够快,持续时间有多长?” 当系统必须在5毫秒内响应传感器输入,或在特定持续时间内保持信号电压高于阈值时,这一点至关重要。

时序图的关键组成部分

掌握此图需要关注其时间机制:

- 时间尺度: 横轴表示时间。它可以是绝对的(时钟时间)或相对的(经过的时间)。

- 状态条: 水平条表示对象的状态(例如:活动、空闲、错误)。条的长度代表持续时间。

- 数值范围: 与离散消息不同,你通常会看到数值范围(例如:电压:0V 到 5V)。这对物理系统至关重要。

- 信号转换: 穿过状态条的垂直线表示值或状态的变化。

- 约束: 文本框或注释可用于指定硬性截止时间(例如,

<截止时间>).

🆚 核心差异:一项技术对比

为了做出明智的决策,我们必须考察这两种表示法之间的结构和语义差异。下表概述了与实时系统设计相关的区别。

| 特性 | 序列图 | 时序图 |

|---|---|---|

| 时间表示 | 逻辑顺序(从上到下) | 物理持续时间(水平轴) |

| 主要关注点 | 交互流程与控制 | 状态演变与信号值 |

| 消息与状态 | 关注消息传递 | 关注状态变化和值 |

| 并发性 | 清晰地显示并行生命线 | 显示随时间推移的并行活动 |

| 截止时间 | 通过消息顺序隐含 | 通过时间尺度和约束显式表示 |

| 复杂性 | 长链路带来的高认知负荷 | 大量信号带来的高认知负荷 |

🛠️ 何时在实时逻辑中使用序列图

虽然时序图在时间精度方面表现优异,但序列图仍然是交互建模的基石。当出现以下情况时,应优先使用序列图:

- 协议定义: 你正在定义一个通信协议(例如,MQTT、TCP/IP 握手)。SYN、ACK 和 FIN 数据包的顺序比精确到毫秒的延迟更为重要。

- 错误处理: 你需要可视化系统对故障的响应方式。控制器如何重试请求?它如何通知用户?序列图能更好地处理分支逻辑(alt/opt 片段)。

- 组件集成: 你正在映射不同软件模块之间的交互。谁调用谁,传递了哪些数据?

- 算法逻辑: 核心复杂性在于决策树,而非执行时间。如果逻辑是

if (x > 5) then do_y,那么序列图能清晰地捕捉这一流程。 - 异步事件: 实时系统通常依赖中断。只要使用组合片段,序列图就非常适合展示主循环运行时发生中断的情况。

示例场景: 一个自动刹车系统接收到传感器输入。序列图将展示传感器向控制器发送数据,控制器处理输入,然后向刹车执行器发送命令的过程。它清晰地映射了逻辑依赖关系。

🕒 何时在实时逻辑中使用时序图

当时间本身成为逻辑中的变量时,时序图就变得必不可少。当出现以下情况时,应切换到这种表示法:

- 存在硬性截止时间: 如果任务必须在10毫秒内完成,否则系统将失败,时序图可以直观展示这个时间窗口。你可以明确画出一条垂直线来标记截止时间。

- 信号稳定性很重要: 在嵌入式系统中,信号通常需要保持高电平一段时间才能被识别。时序图可以展示脉冲宽度的要求。

- 抖动分析: 如果系统必须处理可变延迟(抖动),时序图可以展示消息可能到达时间的范围。

- 资源竞争: 当两个进程竞争一个CPU核心时,时序图可以展示调度间隙,以及一个任务如何阻塞另一个任务。

- 状态机转换 如果设备必须在进入“激活”模式前在“预热”状态下等待5秒,则持续时间是关键约束。时序图明确展示了这一点。

示例场景: 温度传感器每100毫秒发送一次数据。控制器必须在下一次读取到达前处理完这些数据。时序图展示了读取间隔与处理时长之间的重叠(或无重叠)情况。

🔍 深入探讨:并发与同步的处理

实时逻辑很少是线性的。并发是常态。两种图表类型对此的处理方式不同,理解其中的细微差别对架构设计至关重要。

序列图中的并发

序列图使用并行的生命线来表示并发。如果两个对象同时处于活动状态,它们的激活条将并排运行。然而,这并不保证在时间上同时执行,仅保证逻辑上的交错。

- 局限性: 如果两个进程位于不同的线程上,你很难直观地表明进程A必须在进程B开始前完成,无论它们的执行顺序如何。

- 最佳实践: 使用

par用 par 片段来表示并行执行块。这明确了系统期望多个线程或进程并发运行。

时序图中的并发

时序图以空间方式处理并发。由于时间水平流动,你可以堆叠多个生命线,精确查看它们在时间上的重叠位置。

- 优势: 你可以判断“忙等待”循环是否真的阻塞了其他任务。你可以直观地看到一个任务开始与另一个任务结束之间的时间间隔。

- 局限性: 如果存在大量并发线程,它们会迅速变得杂乱。随着信号数量的增加,视觉干扰也随之增加。

🧩 两种图表的整合

在稳健的工程实践中,你很少会选择一种而抛弃另一种。最有效的文档策略是整合两者。它们在设计生命周期中发挥互补作用。

- 高层设计: 从 序列图 开始使用序列图来定义架构、消息流和组件边界。这设定了逻辑契约。

- 低层规范: 使用 时序图 对关键路径进行细化。逻辑确定后,对关键部分施加时间约束。这定义了性能契约。

- 验证: 在测试期间,使用时序图来验证延迟。使用顺序图来验证是否按正确顺序交换了正确的消息。

⚠️ 需要避免的常见陷阱

即使是经验丰富的架构师在建模实时系统时也会犯错。务必警惕这些常见错误。

- 错误地认为顺序意味着持续时间: 一个常见错误是查看顺序图并认为消息之间的垂直距离代表时间。事实并非如此。这会导致对延迟的错误假设。

- 忽略空闲状态: 在时序图中,未能表示“空闲”或“睡眠”状态可能会隐藏功耗问题。确保你的状态条覆盖整个生命周期。

- 过度使用组合片段: 在顺序图中,嵌套过多的

alt或opt块会使图表难以阅读。将复杂逻辑拆分为子图。 - 逻辑时间与物理时间混用: 除非明确标注,否则不要在同一张图中混用逻辑顺序(顺序)和物理时间约束(时序)。应保持它们的区分,以避免混淆。

- 忽略信号噪声: 在物理硬件的时序图中,不要假设信号转换是完美的。如果噪声或去抖时间影响逻辑,请明确标示噪声裕量或去抖时间。

📝 文档编写的最佳实践

为确保你的图表增加价值而非造成杂乱,请遵循以下指南。

- 命名一致性: 为生命线和信号使用一致的命名规范。如果在一个图中将信号称为“ReadSensor”,在另一个图中就不应称为“GetData”。

- 聚焦关键路径: 不要试图绘制每一个函数。聚焦于涉及时序约束或关键故障的路径。简要记录正常流程,但详细说明边缘情况。

- 使用注释: 两种图表类型都支持注释。使用它们来定义单位(ms、µs)、容差和特定需求。在实时设计中,没有单位的数字毫无意义。

- 版本控制: 将图表视为代码。将其存储在版本控制系统中。对时序约束的任何更改都应像代码更改一样经过审查。

- 与利益相关者共同评审: 与开发人员(逻辑)共同评审顺序图,与系统工程师(性能)共同评审时序图。确保受众与图表类型相匹配。

🚀 高级考虑:状态机

实时系统通常是事件驱动的。这使我们进入了状态机与UML图的交汇点。

- 序列图 + 状态机: 使用序列图来展示状态机转换如何由外部消息触发。展示消息进入生命线,以及内部状态变化的发生。

- 时序图 + 状态机: 使用时序图来展示一个状态的持续时间。例如,“超时”状态可能恰好持续3秒。时序图将此持续时间与其他事件进行可视化对比。

在建模复杂的嵌入式逻辑时,将状态机图与时序图结合,通常是描述随时间变化行为的最准确方式。

📊 决策因素总结

为了帮助您做出决策,可以参考此检查清单。

- 主要关注点是操作的顺序吗? ➝ 使用序列图。

- 主要关注点是操作的持续时间吗? ➝ 使用时序图。

- 您正在定义一个软件接口吗? ➝ 使用序列图。

- 您正在定义一个硬件信号需求吗? ➝ 使用时序图。

- 逻辑是否依赖于截止时间? ➝ 使用时序图。

- 逻辑是否依赖于消息协议? ➝ 使用序列图。

🔚 最后思考

在UML时序图和序列图之间进行选择,并非出于偏好,而是为了忠实于系统的约束。序列图映射交互逻辑,时序图映射执行的物理特性。

在实时逻辑领域,模糊性是敌人。通过选择合适的工具,您可以减少模糊性。您为团队提供了一份清晰的蓝图,能够区分系统做什么以及必须在何时完成。这种清晰性直接转化为稳健、可靠且安全的系统。

从流程开始。验证时序。两者都进行记录。这种双重方法确保您的实时逻辑不仅功能正确,而且时序合理。