Diseñar sistemas en tiempo real requiere precisión. Cuando las señales deben llegar dentro de ventanas específicas, y los cambios de estado deben ocurrir de forma predecible, la modelización estándar a menudo resulta insuficiente. Estás manejando una lógica que no solo fluye; late, espera y expira. En este contexto, elegir la notación adecuada del Lenguaje Unificado de Modelado (UML) no es simplemente una elección estilística. Es una decisión de ingeniería crítica que afecta la corrección del sistema.

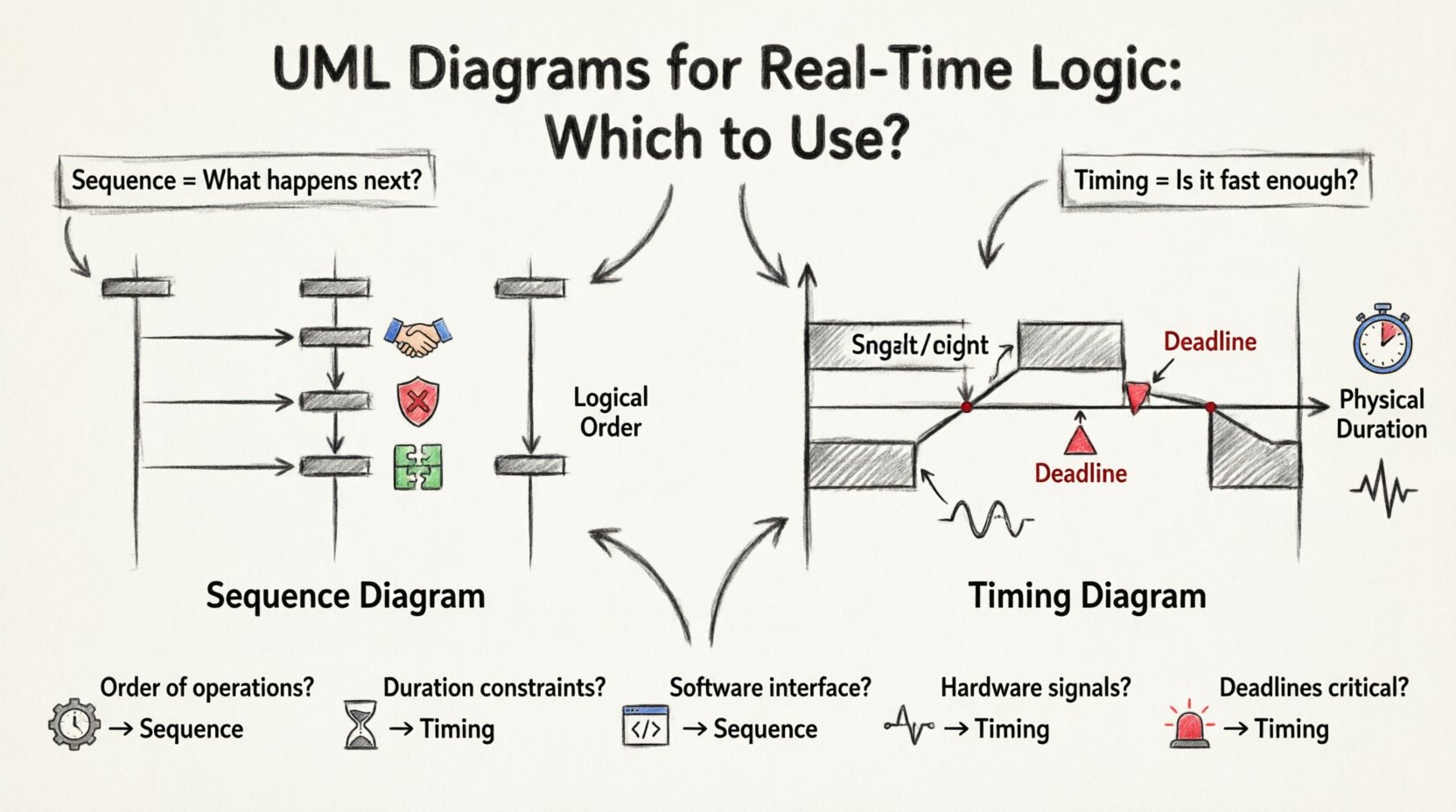

Dos tipos principales de diagramas dominan los debates sobre el modelado de interacción: el Diagrama de secuencia de UML y el Diagrama de temporización de UML. Ambos visualizan el comportamiento, pero capturan dimensiones diferentes de la realidad del sistema. Uno se centra en el orden de los mensajes; el otro se centra en la duración y el estado de los objetos a lo largo del tiempo.

Esta guía ofrece una comparación técnica profunda. Analizaremos cómo cada diagrama maneja la sincronización, la latencia y las restricciones de estado. Al final, comprenderás exactamente cuándo utilizar un diagrama de temporización frente a un diagrama de secuencia en tu arquitectura de lógica en tiempo real.

📡 Comprendiendo el diagrama de secuencia en contexto de tiempo real

El diagrama de secuencia de UML es el estándar de la industria para visualizar el orden de interacción. Muestra cómo los objetos se comunican con el tiempo, organizando los objetos verticalmente y los mensajes horizontalmente. En el contexto de la lógica en tiempo real, destaca al definir el flujo lógico más que el duração física.

- Enfoque:Transmisión de mensajes y flujo de control.

- Eje del tiempo:Implícito. El tiempo fluye de arriba hacia abajo, pero la escala no está definida.

- Elementos clave:Líneas de vida, barras de activación, mensajes (síncronos/asíncronos) y valores de retorno.

- Ideal para:Definir el algoritmo, los protocolos de intercambio de señales y la secuencia de operaciones.

Al modelar un sistema en tiempo real, el diagrama de secuencia responde a la pregunta: “¿Qué sucede a continuación?”Es invaluable para depurar condiciones de carrera que dependen del orden de ejecución más que de la velocidad de ejecución.

Componentes clave de un diagrama de secuencia

Para utilizar esta herramienta de forma efectiva, debes comprender su vocabulario estructural:

- Líneas de vida:Representan instancias de clases o componentes. En sistemas en tiempo real, estas a menudo representan sensores, controladores o buses de comunicación.

- Barras de activación: Muestra cuándo un objeto está realizando una acción. Esto indica una transferencia de control.

- Mensajes síncronos: Representados por flechas sólidas. El remitente espera una respuesta antes de continuar. Esto es crítico para la lógica de bloqueo.

- Mensajes asíncronos: Representados por flechas abiertas. El remitente continúa inmediatamente. Esto modela escenarios de envío y olvido comunes en arquitecturas basadas en eventos.

- Fragmentos combinados:Cajas como

alt,opt, yloople permiten modelar lógica condicional e iteraciones sin ensuciar el diagrama.

⏱️ Comprender el diagrama de temporización en contexto en tiempo real

El diagrama de temporización de UML a menudo se pasa por alto, pero es la herramienta definitiva para modelar comportamientos críticos en el tiempo. A diferencia del diagrama de secuencia, que abstrae el tiempo, el diagrama de temporización trata al tiempo como un eje principal. Muestra cómo cambia el estado de un objeto a lo largo de una línea de tiempo específica.

- Enfoque:Cambios de estado y valores de señal con el tiempo.

- Eje del tiempo: Explícito. Corre horizontalmente en la parte superior del diagrama.

- Elementos clave:Máquinas de estado, rangos de valores, transiciones de señal y plazos.

- Ideal para:Definir restricciones de latencia, análisis de jitter y ventanas de validez de estado.

En la lógica en tiempo real, el diagrama de temporización responde a la pregunta:¿Esto está ocurriendo lo suficientemente rápido, y durante cuánto tiempo? Es esencial cuando el sistema debe responder a una entrada de sensor dentro de 5 milisegundos o mantener un voltaje de señal por encima de un umbral durante una duración específica.

Componentes clave de un diagrama de temporización

Dominar este diagrama requiere atención a sus mecánicas temporales:

- Escala de tiempo: El eje horizontal representa el tiempo. Puede ser absoluto (tiempo de reloj) o relativo (tiempo transcurrido).

- Barras de estado:Las barras horizontales indican el estado de un objeto (por ejemplo, Activo, Inactivo, Error). La longitud de la barra representa la duración.

- Rangos de valores:En lugar de mensajes discretos, a menudo se ven rangos de valores (por ejemplo, Voltaje: 0V a 5V). Esto es crucial para los sistemas físicos.

- Transiciones de señal:Las líneas verticales que cruzan las barras de estado indican un cambio en el valor o el estado.

- Restricciones:Los cuadros de texto o anotaciones pueden especificar plazos estrictos (por ejemplo,

<plazo>).

🆚 Diferencias fundamentales: Una comparación técnica

Para tomar una decisión informada, debemos examinar las diferencias estructurales y semánticas entre estas dos notaciones. La siguiente tabla describe las diferencias relevantes para el diseño de sistemas en tiempo real.

| Característica | Diagrama de secuencia | Diagrama de temporización |

|---|---|---|

| Representación del tiempo | Orden lógico (de arriba hacia abajo) | Duración física (eje horizontal) |

| Enfoque principal | Flujo de interacción y control | Evolución del estado y valores de señal |

| Mensaje frente a estado | Se enfoca en el paso de mensajes | Se enfoca en los cambios de estado y valores |

| Concurrencia | Muestra claramente las líneas de vida paralelas | Muestra actividades paralelas a lo largo del tiempo |

| Plazos | Implicado a través del orden de los mensajes | Explícito mediante escala de tiempo y restricciones |

| Complejidad | Alto esfuerzo cognitivo para cadenas largas | Alto esfuerzo cognitivo para muchas señales |

🛠️ Cuándo usar un diagrama de secuencia para lógica en tiempo real

Mientras que los diagramas de tiempo destacan en precisión temporal, los diagramas de secuencia siguen siendo la base de la modelización de interacciones. Deberías priorizar el diagrama de secuencia cuando:

- Definición de protocolo: Estás definiendo un protocolo de comunicación (por ejemplo, MQTT, handshake de TCP/IP). El orden de los paquetes SYN, ACK y FIN es más importante que el retraso exacto en milisegundos.

- Manejo de errores: Necesitas visualizar cómo responde el sistema ante fallas. ¿Cómo reintentará el controlador una solicitud? ¿Cómo notificará al usuario? Los diagramas de secuencia manejan mejor la lógica de ramificación (fragmentos alt/opt).

- Integración de componentes: Estás mapeando la interacción entre módulos de software distintos. ¿Quién llama a quién, y qué datos se pasan?

- Lógica de algoritmo: La complejidad principal reside en el árbol de decisiones, no en el tiempo de ejecución. Si la lógica es

si (x > 5) entonces hacer_y, un diagrama de secuencia captura este flujo claramente. - Eventos asíncronos:Los sistemas en tiempo real dependen a menudo de interrupciones. Los diagramas de secuencia son excelentes para mostrar una interrupción ocurriendo mientras se ejecuta un bucle principal, siempre que utilices fragmentos combinados.

Escenario de ejemplo: Un sistema de frenado automático recibe una entrada del sensor. El diagrama de secuencia mostraría al sensor enviando datos al controlador, el controlador procesando la entrada y luego enviando una orden al actuador de freno. Representa la dependencia lógica.

🕒 Cuándo usar un diagrama de tiempo para lógica en tiempo real

El diagrama de tiempo se vuelve obligatorio cuando el tiempo en sí mismo es una variable en la lógica. Deberías cambiar a esta notación cuando:

- Existen plazos estrictos: Si una tarea debe completarse en menos de 10 ms, o el sistema falla, un diagrama de tiempo visualiza la ventana. Puedes dibujar explícitamente una línea vertical que marque el plazo.

- La estabilidad de la señal importa: En los sistemas embebidos, las señales a menudo deben permanecer en alto durante una duración específica para ser reconocidas. Un diagrama de tiempo muestra los requisitos de ancho de pulso.

- Análisis de jitter: Si el sistema debe manejar retrasos variables (jitter), un diagrama de tiempo puede mostrar el rango de tiempos posibles de llegada de un mensaje.

- Contención de recursos: Cuando dos procesos compiten por un núcleo de CPU, un diagrama de tiempo puede mostrar los espacios de programación y cómo una tarea bloquea a la otra.

- Transiciones de máquina de estados Si un dispositivo debe esperar en un estado de «Arranque» durante 5 segundos antes de entrar en modo «Activo», la duración es la restricción crítica. Un diagrama de tiempo hace esto explícito.

Escenario de ejemplo: Un sensor de temperatura envía datos cada 100 ms. El controlador debe procesar estos datos antes de que llegue la siguiente lectura. Un diagrama de tiempo muestra la superposición (o ausencia de ella) entre el intervalo de lectura y la duración del procesamiento.

🔍 Análisis profundo: Manejo de concurrencia y sincronización

La lógica en tiempo real rara vez es lineal. La concurrencia es la norma. Ambos tipos de diagramas manejan esto de manera diferente, y comprender la sutileza es vital para la arquitectura.

Concurrencia en diagramas de secuencia

Los diagramas de secuencia utilizan líneas de vida paralelas para mostrar concurrencia. Si dos objetos están activos simultáneamente, sus barras de activación corren lado a lado. Sin embargo, esto no garantiza una ejecución simultánea en el tiempo. Solo garantiza un solapamiento lógico.

- Limitación: No puedes mostrar fácilmente que el proceso A debe finalizar antes de que comience el proceso B, independientemente del orden, si están en hilos diferentes.

- Mejor práctica: Usa

parfragmentos para denotar bloques de ejecución paralela. Esto aclara que el sistema espera que múltiples hilos o procesos se ejecuten de forma concurrente.

Concurrencia en diagramas de tiempo

Los diagramas de tiempo manejan la concurrencia de forma espacial. Debido a que el tiempo fluye horizontalmente, puedes apilar múltiples líneas de vida y ver exactamente dónde se solapan en el tiempo.

- Ventaja: Puedes ver si un bucle de «espera ocupada» realmente bloquea otras tareas. Puedes visualizar el intervalo entre el inicio de una tarea y el final de otra.

- Limitación: Pueden volverse confusos rápidamente si tienes muchos hilos concurrentes. El ruido visual aumenta a medida que aumenta el número de señales.

🧩 Integración de ambos diagramas

En la ingeniería robusta, rara vez eliges uno y descartas el otro. La estrategia de documentación más efectiva integra ambos. Desempeñan roles complementarios en el ciclo de vida del diseño.

- Diseño de alto nivel: Comienza con Diagramas de secuencia para definir la arquitectura, el flujo de mensajes y los límites de los componentes. Esto establece el contrato lógico.

- Especificación de bajo nivel: Refina las rutas críticas con Diagramas de tiempo. Una vez definida la lógica, aplica restricciones temporales a las secciones críticas. Esto define el contrato de rendimiento.

- Verificación: Durante las pruebas, utilice el diagrama de temporización para verificar la latencia. Utilice el diagrama de secuencia para verificar que los mensajes correctos se intercambiaron en el orden correcto.

⚠️ Errores comunes que deben evitarse

Incluso arquitectos con experiencia cometen errores al modelar sistemas en tiempo real. Sé vigilante ante estos errores comunes.

- Asumir que la secuencia implica duración:Un error común es observar un diagrama de secuencia y asumir que la distancia vertical entre los mensajes representa el tiempo. No es así. Esto conduce a suposiciones incorrectas sobre la latencia.

- Ignorar los estados de inactividad:En los diagramas de temporización, no representar el estado de “Inactivo” o “Sueño” puede ocultar problemas de consumo de energía. Asegúrate de que tus barras de estado cubran todo el ciclo de vida.

- Sobrecargar los fragmentos combinados:En los diagramas de secuencia, anidar demasiados

altooptbloques hace que el diagrama sea ilegible. Divida la lógica compleja en subdiagramas. - Mezclar tiempo lógico y físico:No mezcles el orden lógico (secuencia) con las restricciones de tiempo físico (temporización) en el mismo diagrama a menos que esté claramente etiquetado. Mantén ambos separados para evitar confusiones.

- Descuidar el ruido de la señal:En los diagramas de temporización para hardware físico, no asumas transiciones de señal perfectas. Indica los márgenes de ruido o los tiempos de antirrebote si afectan a la lógica.

📝 Mejores prácticas para la documentación

Para asegurarte de que tus diagramas aporten valor en lugar de crear confusión, sigue estas directrices.

- Nombres coherentes:Utiliza convenciones de nombres coherentes para las líneas de vida y las señales. Si llamas a una señal “LeerSensor” en un diagrama, no la llames “ObtenerDatos” en otro.

- Enfócate en las rutas críticas:No intentes diagramar cada función individual. Enfócate en las rutas que implican restricciones de tiempo o fallos críticos. Documenta brevemente el camino normal, pero detalla los casos extremos.

- Utiliza anotaciones:Ambos tipos de diagramas admiten anotaciones. Úsalas para definir unidades (ms, µs), tolerancias y requisitos específicos. Un número sin unidad carece de significado en el diseño en tiempo real.

- Control de versiones:Trata los diagramas como código. Guárdalos en control de versiones. Los cambios en las restricciones de temporización deben revisarse como cualquier cambio de código.

- Revisa con los interesados:Revisa los diagramas de secuencia con desarrolladores (lógica). Revisa los diagramas de temporización con ingenieros de sistemas (rendimiento). Asegúrate de que la audiencia coincida con el tipo de diagrama.

🚀 Consideraciones avanzadas: Máquinas de estado

Los sistemas en tiempo real suelen ser impulsados por eventos. Esto nos lleva a la intersección entre máquinas de estado y diagramas UML.

- Diagramas de secuencia + Máquinas de estado:Utilice diagramas de secuencia para mostrar cómo una transición de máquina de estado es desencadenada por un mensaje externo. Muestre cómo el mensaje entra en la línea de vida y cómo ocurre el cambio de estado interno.

- Diagramas de tiempo + Máquinas de estado:Utilice diagramas de tiempo para mostrar la duración de un estado. Por ejemplo, un estado de “Tiempo de espera” podría durar exactamente 3 segundos. El diagrama de tiempo visualiza esta duración en relación con otros eventos.

Al modelar lógica embebida compleja, combinar un diagrama de máquina de estado con un diagrama de tiempo suele ser la representación más precisa del comportamiento a lo largo del tiempo.

📊 Resumen de los factores de decisión

Para ayudarle en su proceso de toma de decisiones, considere esta lista de verificación.

- ¿Es la preocupación principal el orden de las operaciones? ➝ Utilice el diagrama de secuencia.

- ¿Es la preocupación principal la duración de una operación? ➝ Utilice el diagrama de tiempo.

- ¿Está definiendo una interfaz de software? ➝ Utilice el diagrama de secuencia.

- ¿Está definiendo un requisito de señal de hardware? ➝ Utilice el diagrama de tiempo.

- ¿Depende la lógica de plazos? ➝ Utilice el diagrama de tiempo.

- ¿Depende la lógica de protocolos de mensajes? ➝ Utilice el diagrama de secuencia.

🔚 Reflexiones finales

Elegir entre un diagrama de tiempo UML y un diagrama de secuencia no se trata de preferencia; se trata de fidelidad a las restricciones del sistema. Los diagramas de secuencia representan la lógica de la interacción. Los diagramas de tiempo representan la física de la ejecución.

En el ámbito de la lógica en tiempo real, la ambigüedad es el enemigo. Al elegir la herramienta adecuada, reduce la ambigüedad. Proporciona a su equipo un plano claro que distingue entre lo que el sistema hace y cuándo debe hacerlo. Esta claridad se traduce directamente en sistemas robustos, confiables y seguros.

Comience con el flujo. Valide el tiempo. Documente ambos. Este enfoque dual garantiza que su lógica en tiempo real no solo sea funcionalmente correcta, sino también temporalmente sólida.