Projetar sistemas em tempo real exige precisão. Quando os sinais devem chegar dentro de janelas específicas e as mudanças de estado devem ocorrer de forma previsível, a modelagem padrão frequentemente falha. Você está lidando com uma lógica que não apenas flui; ela pulsa, espera e expira. Nesse cenário, escolher a notação correta da Linguagem de Modelagem Unificada (UML) não é meramente uma escolha estilística. É uma decisão de engenharia crítica que afeta a correção do sistema.

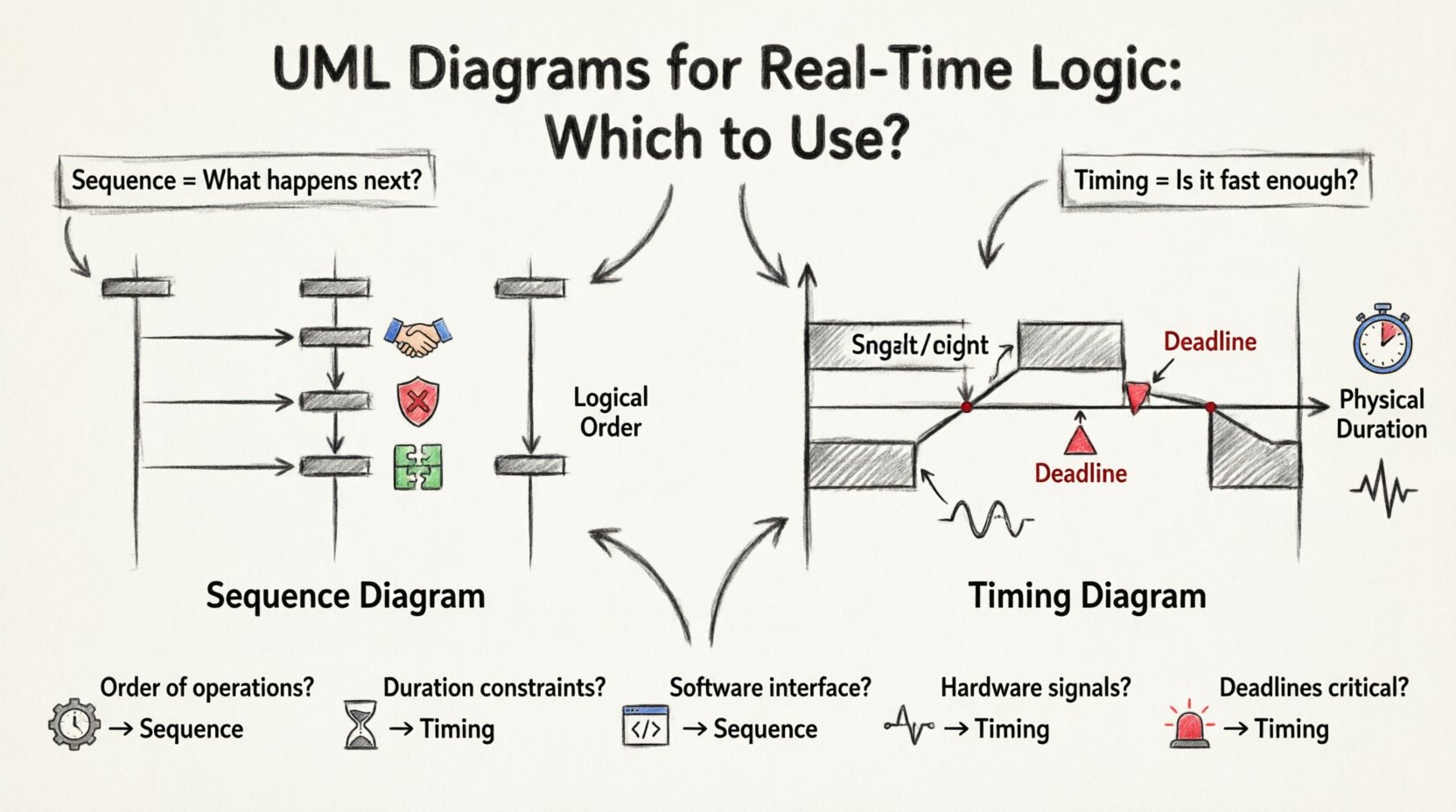

Dois tipos principais de diagramas dominam as discussões sobre modelagem de interação: o Diagrama de Sequência UML e o Diagrama de Tempo UML. Ambos visualizam o comportamento, mas capturam dimensões diferentes da realidade do sistema. Um foca na ordem das mensagens; o outro foca na duração e no estado dos objetos ao longo do tempo.

Este guia fornece uma comparação técnica aprofundada. Analisaremos como cada diagrama lida com sincronização, latência e restrições de estado. No final, você entenderá exatamente quando usar um diagrama de tempo em vez de um diagrama de sequência na sua arquitetura de lógica em tempo real.

📡 Compreendendo o Diagrama de Sequência no Contexto de Tempo Real

O Diagrama de Sequência UML é o padrão da indústria para visualizar a ordem de interação. Ele mapeia como os objetos se comunicam ao longo do tempo, organizando os objetos verticalmente e as mensagens horizontalmente. No contexto de lógica em tempo real, ele se destaca na definição do fluxo lógico em vez do duração física.

- Foco:Passagem de mensagens e fluxo de controle.

- Eixo do Tempo:Implícito. O tempo flui de cima para baixo, mas a escala não é definida.

- Elementos Principais:Linhas de vida, barras de ativação, mensagens (síncronas/assíncronas) e valores de retorno.

- Melhor para:Definir o algoritmo, os protocolos de handshake e a sequência de operações.

Ao modelar um sistema em tempo real, o diagrama de sequência responde à pergunta: “O que acontece em seguida?”É inestimável para depurar condições de corrida que dependem da ordem de execução, e não da velocidade de execução.

Componentes Principais de um Diagrama de Sequência

Para usar esta ferramenta de forma eficaz, você deve entender seu vocabulário estrutural:

- Linhas de vida:Representam instâncias de classes ou componentes. Em sistemas em tempo real, esses frequentemente representam sensores, controladores ou barramentos de comunicação.

- Barras de Ativação: Mostra quando um objeto está realizando uma ação. Isso indica a transferência de controle.

- Mensagens Síncronas: Representadas por setas sólidas. O remetente espera pela resposta antes de prosseguir. Isso é crítico para lógica de bloqueio.

- Mensagens Assíncronas: Representadas por setas abertas. O remetente continua imediatamente. Isso modela cenários de disparo e esquecimento comuns em arquiteturas orientadas a eventos.

- Fragmentos Combinados: Caixas como

alt,opt, elooppermitem modelar lógica condicional e iterações sem poluir o diagrama.

⏱️ Compreendendo o Diagrama de Tempo no Contexto em Tempo Real

O Diagrama de Tempo UML é frequentemente ignorado, mas é a ferramenta definitiva para modelar comportamentos críticos no tempo. Diferentemente do diagrama de sequência, que abstrai o tempo, o diagrama de tempo trata o tempo como um eixo principal. Ele mostra como o estado de um objeto muda ao longo de uma linha do tempo específica.

- Foco: Mudanças de estado e valores de sinal ao longo do tempo.

- Eixo do Tempo: Explícito. Corre horizontalmente na parte superior do diagrama.

- Elementos Principais: Máquinas de estado, intervalos de valores, transições de sinal e prazos.

- Melhor para: Definir restrições de latência, análise de jitter e janelas de validade de estado.

Na lógica em tempo real, o diagrama de tempo responde à pergunta: “Isso está acontecendo rápido o suficiente, e por quanto tempo?” É essencial quando o sistema deve responder a uma entrada de sensor em menos de 5 milissegundos ou manter a tensão de um sinal acima de um limiar por uma duração específica.

Componentes Principais de um Diagrama de Tempo

Dominar este diagrama exige atenção à sua mecânica temporal:

- Escala de Tempo: O eixo horizontal representa o tempo. Pode ser absoluto (tempo de relógio) ou relativo (tempo decorrido).

- Barras de Estado:Barras horizontais indicam o estado de um objeto (por exemplo, Ativo, Ocioso, Erro). O comprimento da barra representa a duração.

- Faixas de Valores:Em vez de mensagens discretas, você frequentemente vê faixas de valores (por exemplo, Tensão: 0V a 5V). Isso é crucial para sistemas físicos.

- Transições de Sinal:Linhas verticais que cruzam as barras de estado indicam uma mudança no valor ou no estado.

- Restrições:Caixas de texto ou anotações podem especificar prazos rígidos (por exemplo,

<prazo>).

🆚 Diferenças Principais: Uma Comparação Técnica

Para tomar uma decisão informada, devemos analisar as diferenças estruturais e semânticas entre essas duas notações. A tabela a seguir apresenta as distinções relevantes para o design de sistemas em tempo real.

| Funcionalidade | Diagrama de Sequência | Diagrama de Temporização |

|---|---|---|

| Representação do Tempo | Ordem lógica (de cima para baixo) | Duração física (eixo horizontal) |

| Foco Principal | Fluxo de interação e controle | Evolução do estado e valores de sinal |

| Mensagem vs. Estado | Foca na passagem de mensagens | Foca nas mudanças de estado e valores |

| Concorrência | Mostra claramente linhas de vida paralelas | Mostra atividades paralelas ao longo do tempo |

| Prazos | Implícito pela ordem das mensagens | Explícito por meio da escala de tempo e restrições |

| Complexidade | Alto esforço cognitivo para cadeias longas | Alto esforço cognitivo para muitos sinais |

🛠️ Quando usar um diagrama de sequência para lógica em tempo real

Enquanto os diagramas de tempo se destacam na precisão temporal, os diagramas de sequência permanecem a base da modelagem de interações. Você deve priorizar o diagrama de sequência quando:

- Definição de protocolo: Você está definindo um protocolo de comunicação (por exemplo, MQTT, handshake TCP/IP). A ordem dos pacotes SYN, ACK e FIN é mais importante do que o atraso exato em milissegundos.

- Tratamento de erros: Você precisa visualizar como o sistema reage a falhas. Como o controlador repete uma solicitação? Como ele notifica o usuário? Os diagramas de sequência lidam melhor com a lógica de ramificação (fragmentos alt/opt).

- Integração de componentes: Você está mapeando a interação entre módulos de software distintos. Quem chama quem, e quais dados são passados?

- Lógica de algoritmo: A complexidade central reside na árvore de decisões, e não no tempo de execução. Se a lógica for

se (x > 5) então faça_y, um diagrama de sequência captura esse fluxo claramente. - Eventos assíncronos: Sistemas em tempo real muitas vezes dependem de interrupções. Os diagramas de sequência são excelentes para mostrar uma interrupção ocorrendo enquanto um loop principal está em execução, desde que você use fragmentos combinados.

Cenário de exemplo: Um sistema de freio automático recebe uma entrada do sensor. O diagrama de sequência mostraria o sensor enviando dados para o controlador, o controlador processando a entrada e, em seguida, enviando um comando para o atuador de freio. Ele mapeia a dependência lógica.

🕒 Quando usar um diagrama de tempo para lógica em tempo real

O diagrama de tempo torna-se obrigatório quando o tempo em si é uma variável na lógica. Você deve mudar para esta notação quando:

- Prazos rígidos existem: Se uma tarefa deve ser concluída em até 10ms, ou o sistema falhará, um diagrama de tempo visualiza a janela. Você pode desenhar explicitamente uma linha vertical marcando o prazo.

- A estabilidade do sinal importa: Em sistemas embarcados, os sinais muitas vezes precisam permanecer em nível alto por uma duração específica para serem reconhecidos. Um diagrama de tempo mostra os requisitos de largura de pulso.

- Análise de jitter: Se o sistema precisar lidar com atrasos variáveis (jitter), um diagrama de tempo pode mostrar a faixa de tempos possíveis de chegada de uma mensagem.

- Contenção de recursos: Quando dois processos competem por um núcleo da CPU, um diagrama de tempo pode mostrar as lacunas de escalonamento e como uma tarefa bloqueia a outra.

- Transições de máquina de estadosSe um dispositivo precisar esperar no estado de “Aquecimento” por 5 segundos antes de entrar no modo “Ativo”, a duração é a restrição crítica. Um diagrama de tempo torna isso explícito.

Cenário de Exemplo:Um sensor de temperatura envia dados a cada 100ms. O controlador deve processar esses dados antes que a próxima leitura chegue. Um diagrama de tempo mostra a sobreposição (ou ausência dela) entre o intervalo de leitura e a duração do processamento.

🔍 Aprofundamento: Tratamento de Concorrência e Sincronização

A lógica em tempo real raramente é linear. A concorrência é a regra. Ambos os tipos de diagrama lidam com isso de maneiras diferentes, e compreender as nuances é vital para a arquitetura.

Concorrência em Diagramas de Sequência

Diagramas de sequência usam linhas de vida paralelas para mostrar concorrência. Se dois objetos estiverem ativos simultaneamente, suas barras de ativação correm lado a lado. No entanto, isso não garante execução simultânea no tempo. Apenas garante um intercalamento lógico.

- Limitação:Você não consegue mostrar facilmente que o Processo A deve terminar antes do início do Processo B, independentemente da ordem, se eles estiverem em threads diferentes.

- Melhor Prática:Use

parfragmentos para indicar blocos de execução paralela. Isso esclarece que o sistema espera que múltiplas threads ou processos sejam executados simultaneamente.

Concorrência em Diagramas de Tempo

Diagramas de tempo lidam com concorrência de forma espacial. Como o tempo flui horizontalmente, você pode empilhar múltiplas linhas de vida e ver exatamente onde elas se sobrepõem no tempo.

- Vantagem:Você pode ver se um loop de “Espera Ocupada” realmente bloqueia outras tarefas. Você pode visualizar a lacuna entre o início de uma tarefa e o fim de outra.

- Limitação:Eles podem ficar rapidamente confusos se você tiver muitas threads concorrentes. O ruído visual aumenta conforme o número de sinais cresce.

🧩 Integração de Ambos os Diagramas

Na engenharia robusta, você raramente escolhe um e descarta o outro. A estratégia de documentação mais eficaz integra ambos. Eles desempenham papéis complementares no ciclo de vida do projeto.

- Projeto de Alto Nível:Comece com Diagramas de Sequênciapara definir a arquitetura, o fluxo de mensagens e os limites dos componentes. Isso estabelece o contrato lógico.

- Especificação de Baixo Nível:Aprimore os caminhos críticos com Diagramas de Tempo. Uma vez que a lógica for definida, aplique restrições temporais às seções críticas. Isso define o contrato de desempenho.

- Verificação: Durante os testes, use o diagrama de tempo para verificar a latência. Use o diagrama de sequência para verificar que as mensagens corretas foram trocadas na ordem correta.

⚠️ Armadilhas Comuns a Evitar

Mesmo arquitetos experientes cometem erros ao modelar sistemas em tempo real. Esteja atento a esses erros comuns.

- Assumindo que a Sequência Implica Duração: Um erro comum é olhar para um diagrama de sequência e assumir que a distância vertical entre as mensagens representa tempo. Isso não é verdade. Isso leva a suposições incorretas sobre latência.

- Ignorando Estados Ociosos: Nos diagramas de tempo, a falha em representar o estado “Ocioso” ou “Sono” pode ocultar problemas de consumo de energia. Certifique-se de que suas barras de estado cubram todo o ciclo de vida.

- Sobreuso de Fragmentos Combinados: Nos diagramas de sequência, aninhar muitos demais

altouoptblocos torna o diagrama ilegível. Divida a lógica complexa em subdiagramas. - Misturando Tempo Lógico e Físico: Não misture a ordem lógica (sequência) com restrições de tempo físico (tempo) no mesmo diagrama, a menos que esteja claramente rotulado. Mantenha-os distintos para evitar confusão.

- Descuidando-se com o Ruído do Sinal: Nos diagramas de tempo para hardware físico, não assuma transições perfeitas de sinal. Indique margens de ruído ou tempos de amortecimento se afetarem a lógica.

📝 Melhores Práticas para Documentação

Para garantir que seus diagramas adicionem valor em vez de causar confusão, siga estas diretrizes.

- Nomenclatura Consistente: Use convenções de nomenclatura consistentes para linhas de vida e sinais. Se você chamar um sinal de “ReadSensor” em um diagrama, não o chame de “GetData” em outro.

- Foque nos Caminhos Críticos: Não tente diagramar cada função individualmente. Foque nos caminhos que envolvem restrições de tempo ou falhas críticas. Documente o caminho feliz brevemente, mas detalhe os casos extremos.

- Use Anotações: Ambos os tipos de diagrama suportam anotações. Use-as para definir unidades (ms, µs), tolerâncias e requisitos específicos. Um número sem unidade é sem sentido no design em tempo real.

- Controle de Versão: Trate os diagramas como código. Armazene-os em controle de versão. Alterações nas restrições de tempo devem ser revisadas da mesma forma que alterações de código.

- Revisão com Stakeholders: Revise diagramas de sequência com desenvolvedores (lógica). Revise diagramas de tempo com engenheiros de sistema (desempenho). Certifique-se de que o público-alvo corresponda ao tipo de diagrama.

🚀 Considerações Avançadas: Máquinas de Estados

Sistemas em tempo real são frequentemente impulsionados por eventos. Isso nos leva à interseção entre Máquinas de Estados e diagramas UML.

- Diagramas de Sequência + Máquinas de Estados:Use diagramas de sequência para mostrar como uma transição de máquina de estados é acionada por uma mensagem externa. Mostre a mensagem entrando na linha de vida e a mudança de estado interna ocorrendo.

- Diagramas de Tempo + Máquinas de Estados:Use diagramas de tempo para mostrar a duração de um estado. Por exemplo, um estado de “Tempo Esgotado” pode durar exatamente 3 segundos. O diagrama de tempo visualiza essa duração em relação a outros eventos.

Ao modelar lógica embarcada complexa, combinar um diagrama de Máquina de Estados com um diagrama de Tempo é frequentemente a representação mais precisa do comportamento ao longo do tempo.

📊 Resumo dos Fatores de Decisão

Para auxiliar no seu processo de tomada de decisão, considere esta lista de verificação.

- A preocupação principal é a ordem das operações? ➝ Use o Diagrama de Sequência.

- A preocupação principal é a duração de uma operação? ➝ Use o Diagrama de Tempo.

- Você está definindo uma interface de software? ➝ Use o Diagrama de Sequência.

- Você está definindo um requisito de sinal de hardware? ➝ Use o Diagrama de Tempo.

- A lógica depende de prazos? ➝ Use o Diagrama de Tempo.

- A lógica depende de protocolos de mensagens? ➝ Use o Diagrama de Sequência.

🔚 Pensamentos Finais

Escolher entre um Diagrama de Tempo UML e um Diagrama de Sequência não se trata de preferência; trata-se de fidelidade às restrições do sistema. Diagramas de sequência mapeiam a lógica da interação. Diagramas de tempo mapeiam a física da execução.

No domínio da lógica em tempo real, a ambiguidade é o inimigo. Ao escolher a ferramenta certa, você reduz a ambiguidade. Você fornece à sua equipe um plano claro que distingue o que o sistema faz e quando deve fazê-lo. Essa clareza se traduz diretamente em sistemas robustos, confiáveis e seguros.

Comece com o fluxo. Valide o tempo. Documente ambos. Essa abordagem dual garante que sua lógica em tempo real não seja apenas funcionalmente correta, mas também temporalmente sólida.