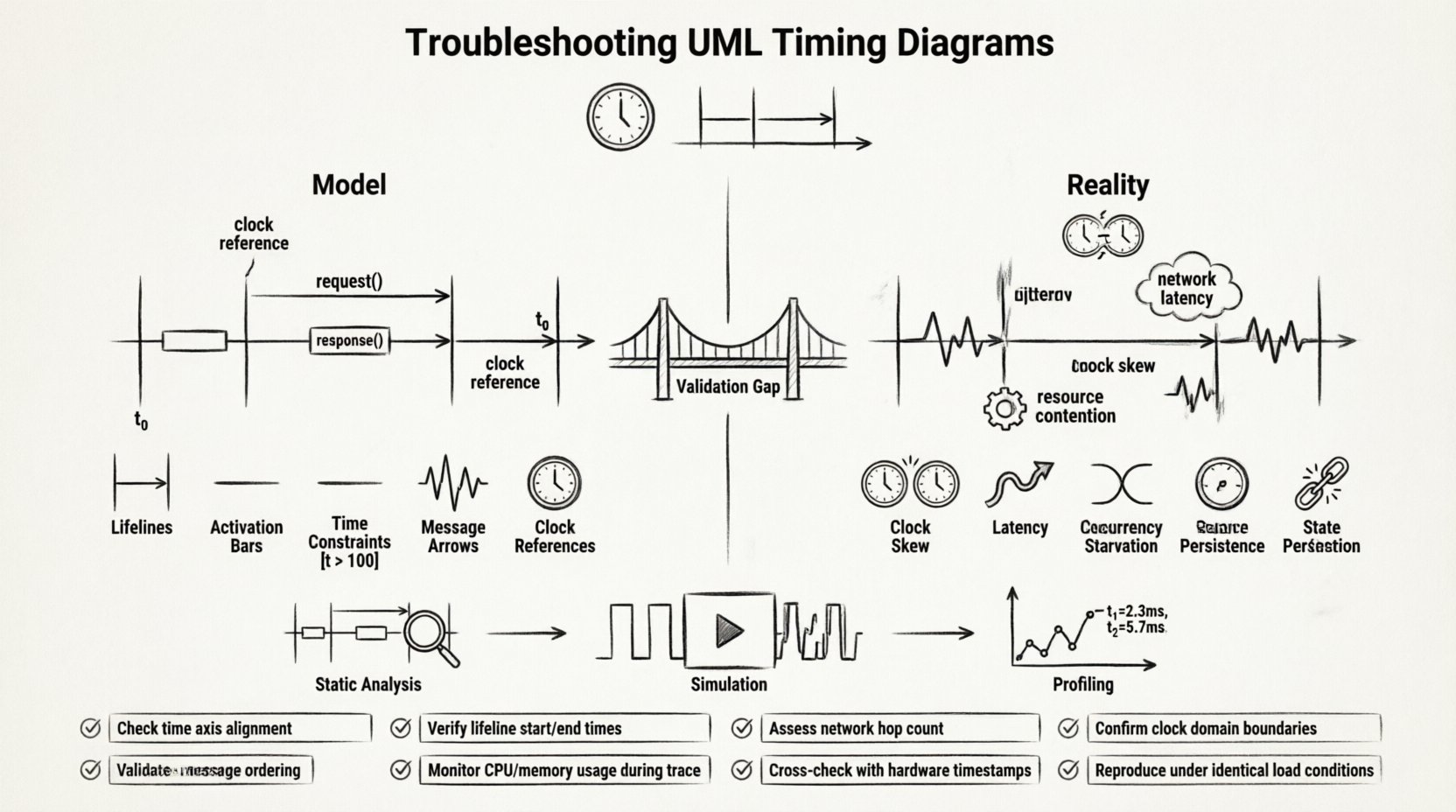

Gdy różnica między modelem projektowym a rzeczywistym wykonaniem systemu się zwiększa, zespoły inżynierskie napotykają krytyczne wyzwania. Jest to szczególnie prawdziwe dlaDiagramy czasowe UML, które są szkicem interakcji krytycznych pod względem czasu. Te diagramy pokazują, jak obiekty zachowują się w czasie, określając dokładne ograniczenia dotyczące przybycia wiadomości i zmian stanu. Jednak podczas implementacji często pojawiają się rozbieżności. Kod zachowuje się inaczej niż przewiduje model. Ta rozbieżność może prowadzić do warunków wyścigu, przekroczenia terminów i niestabilności systemu. Zrozumienie sposobu rozwiązywania tych rozbieżności jest kluczowe dla utrzymania integralności systemu.

Ten przewodnik bada mechanizmy identyfikowania i rozwiązywania anomalii czasowych. Przeanalizujemy elementy strukturalne modeli czasowych, typowe przyczyny odchyleń zachowania oraz systematyczne metody weryfikacji. Poprzez dopasowanie Twoichograniczeń czasowychdo rzeczywistości zapewnisz, że system działa niezawodnie pod obciążeniem. Zaczniemy od zdefiniowania podstawowych składników oraz miejsc, z których błędy zwykle pochodzą.

🛑 Przepaść między abstrakcją a wykonaniem

Diagramy czasowe UML to abstrakcyjne reprezentacje. Uproszczają skomplikowane rzeczywistości fizyczne na potrzeby logiki wizualnej. Model zakłada idealne warunki: zerową opóźnienie sieciowe, deterministyczne cykle zegara i natychmiastową dostępność zasobów. W rzeczywistości rzadko spełnia się te założenia. Gdy przechodzisz z fazyfazy projektowaniado fazywdrażania, środowisko wprowadza szum.

- Zmienność sprzętu: Różne procesory wykonują instrukcje z różną prędkością.

- Zmienność sieciowa (jitter): Czasy dostarczania pakietów ulegają wahaniom w systemach rozproszonych.

- Konkurencja o zasoby: Współdzielona pamięć lub rdzenie CPU powodują opóźnienia, które nie zostały przewidziane w izolacji.

Gdy Twojezachowanie systemu nie zgadza się z modelem, często dlatego, że model nie uwzględnił tych czynników środowiskowych. Rozwiązywanie problemów wymaga zmiany od weryfikacji teoretycznej do weryfikacji empirycznej. Musisz traktować diagram nie jako statyczny dokument, ale jako żywe założenie, które wymaga ciągłego testowania.

🔍 Zrozumienie architektury diagramu czasowego

Zanim naprawisz błędy, musisz zrozumieć elementy, z których składa się diagram czasowy. Te diagramy różnią się od diagramów sekwencji, ponieważ naciskają mocno na oś czasu. Oś pozioma reprezentuje czas, a oś pionowa reprezentujelinie życiaobiektów lub procesów uczestniczących w interakcji.

1. Linie życia i osie czasu

Linie życia reprezentują jednostki uczestniczące w interakcji. W kontekście czasowym każda linia życia musi mieć zdefiniowany zegar lub odniesienie czasowe. Jeśli dwie linie życia działają na różnych zegarach, pojawiają się problemy synchronizacji. Musisz zapewnić spójność jednostek czasu na całym diagramie. Mieszanie milisekund z cyklami zegara bez konwersji prowadzi do błędów obliczeniowych.

2. Paski aktywacji

Paski aktywacji wskazują, kiedy obiekt aktywnie wykonuje działanie. W diagramach czasowych długość tych pasków jest krytyczna. Jeśli model pokazuje działanie trwające 5ms, a sprzęt potrzebuje 10ms, system zawodzi. Musisz zweryfikować długość każdej aktywacji pod kątem rzeczywistego czasu wykonania odpowiadającego bloku kodu.

3. Warunki i strażnicy

Warunki na osi czasu określają, kiedy przejście jest dozwolone. Często wyrażane są jako wyrażenia typu [t > 100]. Jeśli model zakłada, że warunek jest spełniony w t=100, ale system osiąga go w t=105, kolejne zdarzenia są opóźnione. To opóźnienie może się kumulować, wpływając na zależne procesy.

4. Komunikaty i sygnały

Komunikaty są wyzwalaczami, które przenoszą system z jednego stanu do drugiego. W diagramach czasowych czas przybycia komunikatu jest jawny. Usuwanie usterek często wymaga porównania rzeczywistego czasu przybycia z zaplanowanym czasem. Jeśli komunikaty przychodzą w niepoprawnej kolejności, logika modelu jest nieważna.

⚠️ Najczęstsze źródła rozbieżności zachowania

Identyfikacja przyczyny pierwotnej rozbieżności czasowej to pierwszy krok w usuwaniu usterek. Istnieją konkretne kategorie błędów, które często występują. Poniżej znajduje się analiza najbardziej typowych źródeł.

| Kategoria | Opis | Wpływ |

|---|---|---|

| Zniekształcenie zegara | Różnica między źródłami zegarów różnych komponentów. | Niesynchronizacja procesów równoległych. |

| Założenia dotyczące opóźnienia | Zakładanie, że opóźnienie sieciowe lub szynowe wynosi zero lub jest stałe. | Pominięte terminy i błędy przekroczenia czasu oczekiwania. |

| Problemy z współbieżnością | Wiele wątków uzyskujących dostęp do współdzielonych zasobów jednocześnie. | Zawieszenia lub warunki wyścigu. |

| Zaprawa zasobów | Niewystarczająca ilość CPU lub pamięci dostępna dla zadania. | Opóźniona realizacja pasków aktywacji. |

| Trwałość stanu | Stan nie jest poprawnie zapisywany między przedziałami czasowymi. | Niepoprawne przejścia stanów po ponownym uruchomieniu. |

Przejście między domenami zegarowymi

Jednym z najczęściej występujących problemów w modelowaniu sprzętu i oprogramowania niskiego poziomu jest przejście między domenami zegarowymi. Jeśli Twój system używa wielu zegarów, diagramy czasowe muszą jawnie modelować punkty synchronizacji. Jeśli model zakłada jeden zegar, ale implementacja używa oddzielnych domen, ograniczenia czasowe stają się bez sensu. Musisz uwzględnić opóźnienie wprowadzane przez synchronizatory.

Kolejność wiadomości

Diagramy czasowe często sugerują ściśle określoną kolejność zdarzeń. W rzeczywistości pakiety sieciowe lub komunikaty międzyprocesowe mogą dotrzeć w innej kolejności. Jeśli Twój model zakłada, że wiadomość A przychodzi przed wiadomością B, ale system najpierw otrzymuje B, przepływ logiki się rozrywa. Jest to częste w systemach asynchronicznych, gdziegwarancje dostarczenia nie są wymuszane.

Niedeterministyczne opóźnienia

Niektóre zachowania systemu są w istocie niedeterministyczne. Zbieranie śmieci, wymiana pamięci wirtualnej i algorytmy planowania wprowadzają zróżnicowanie. Jeśli Twój diagram czasowy używa stałych wartości czasu dla tych procesów, model zawiedzie podczas testów obciążeniowych. Zamiast stałych wartości należy używać zakresów lub czasów najgorszego przypadku (WCET).

🛠️ Metodyki weryfikacji i walidacji

Gdy już zidentyfikujesz potencjalne źródła błędów, potrzebujesz metodyki weryfikacji modelu względem systemu. Walidacja nie jest jednorazowym zadaniem; jest ciągłym procesem w całym cyklu rozwoju oprogramowania.

1. Analiza statyczna modelu

Zanim uruchomisz jakikolwiek kod, przeanalizuj diagram czasowy pod kątem spójności logicznej. Sprawdź obecność zakleszczeń, pętli nieskończonych lub nieosiągalnych stanów. Upewnij się, że wszystkie ograniczenia czasowe są matematycznie możliwe. Jeśli zadanie wymaga 10ms, a okres wynosi 5ms, model jest nieprawidłowy niezależnie od jakości kodu.

- Sprawdź łańcuchy zależności: Upewnij się, że żadne zadanie nie zależy od samego siebie w tym samym oknie czasowym.

- Zweryfikuj przestrzeganie terminów: Potwierdź, że suma czasów wykonania nie przekracza terminu.

- Zanalizuj wykorzystanie zasobów: Upewnij się, że zadania współbieżne nie przekraczają dostępnych zasobów.

2. Symulacja i emulacja

Symulacja pozwala uruchomić model w kontrolowanym środowisku. Możesz wstrzykiwać konkretne opóźnienia lub błędy, aby zobaczyć, jak system na nie reaguje. Pomaga to izolować problemy czasowe bez wpływu na środowisko produkcyjne. Używaj symulacji do testowania przypadków brzegowych, które trudno jest odtworzyć w czasie rzeczywistym.

- Wstrzykuj opóźnienia: Dodaj sztuczne opóźnienia do wiadomości, aby przetestować odporność.

- Testy obciążeniowe: Uruchom system w maksymalnym obciążeniu, aby obserwować degradację czasu.

- Wstrzykiwanie błędów: Symuluj utratę lub uszkodzenie wiadomości, aby sprawdzić czas odzyskania.

3. Profilowanie i instrumentacja

Instrumentacja kodu za pomocą zegarów i dzienników zapewnia dane z rzeczywistego świata. Porównaj zarejestrowane znaczniki czasu z przewidywaniami modelu. Ten podejście oparte na danych ujawnia, gdzie model odchyla się od rzeczywistości. Szukaj wzorców w odchyleniach. Czy są one spójne? Czy są przypadkowe? Czy występują w określonych warunkach?

- Śledź wykonanie: Zapisz czas rozpoczęcia i zakończenia każdego paska aktywacji.

- Monitoruj przychód wiadomości: Zapisz dokładny znacznik czasu każdego przychodzącego sygnału.

- Skoreluj zdarzenia: Przypisz wpisy dziennika do konkretnych elementów na diagramie czasowym.

🔄 Wyrównanie z diagramami sekwencji i stanów

Diagram czasowy nie istnieje samodzielnie. Jest częścią większego zestawu UML. Niezgodności często pojawiają się, gdy diagram czasowy koliduje z innymi diagramami. Na przykład,Diagram sekwencji może pokazywać przepływ logiczny, aleDiagram czasowy pokazuje naruszenie czasowe.

Spójność między diagramami

Upewnij się, że kolejność zdarzeń na diagramie czasowym odpowiada przepływowi logicznemu na diagramie sekwencji. Jeśli diagram sekwencji pokazuje punkt decyzyjny, diagram czasowy musi uwzględniać czas potrzebny na ocenę tej decyzji. Różnice między diagramami często wskazują na nieporozumienie w logice systemu.

Integracja maszyny stanów

Diagramy stanów definiują stany, w których może się znajdować obiekt. Diagramy czasowe definiują, jak długo obiekt pozostaje w tych stanach. Jeśli diagram czasowy sugeruje zmianę stanu, której maszyna stanów nie obsługuje, występuje konflikt. Musisz zsynchronizować przejścia stanów z ograniczeniami czasowymi.

Wyrównanie z przypadkami użycia

Na końcu upewnij się, że wymagania czasowe wspierają przypadki użycia. Jeśli przypadek użycia wymaga czasu odpowiedzi 200ms, diagram czasowy musi odzwierciedlać to ograniczenie. Jeśli model pozwala na 500ms, system nie spełni oczekiwań użytkownika. Wyrównaj ograniczenia czasowe z wymaganiami funkcjonalnymi.

📊 Lista kontrolna diagnostyczna dla anomalii czasowych

Podczas rozwiązywania problemów używaj zorganizowanej listy kontrolnej, aby upewnić się, że nie pominiesz żadnego kroku. Ta lista obejmuje kluczowe obszary, w których typowo ukrywają się błędy czasowe.

- ✓ Sprawdź synchronizację zegarów: Czy wszystkie komponenty używają tej samej referencji czasowej?

- ✓ Sprawdź kolejność wiadomości: Czy wiadomości przychodzą w oczekiwanej kolejności?

- ✓ Weryfikuj czasy wykonania: Czy rzeczywiste czasy wykonania odpowiadają przewidywaniom modelu?

- ✓ Sprawdź konkurencję zasobów: Czy jest wystarczająco dużo pamięci CPU lub pamięci operacyjnej dla zaplanowanych zadań?

- ✓ Przejrzyj przejścia stanów: Czy zmiany stanów odbywają się w dozwolonym oknie czasowym?

- ✓ Testuj przypadki krawędziowe: Jak system zachowuje się na granicach ograniczeń czasowych?

- ✓ Analizuj obciążenie sieci: Czy wysokie obciążenie sieci wpływa na czasy dostarczania wiadomości?

- ✓ Potwierdź terminy końcowe: Czy wszystkie kluczowe terminy końcowe są spełnione podczas maksymalnej obciążenia?

🛡️ Strategie długoterminowej konserwacji

Nawet po rozwiązaniu początkowych rozbieżności modele czasowe wymagają konserwacji. Systemy się rozwijają, tak samo jak ich wymagania. Diagram czasowy, który był poprawny wczoraj, może być dziś przestarzały.

Kontrola wersji dla modeli

Traktuj swoje diagramy jak kod. Przechowuj je w systemach kontroli wersji. Pozwala to śledzić zmiany w czasie i cofnąć się do wcześniejszych wersji, jeśli nowa zmiana spowoduje problemy z czasem. Dokumentuj każdą zmianę w ograniczeniach czasowych, aby zachować jasny historii.

Automatyzowane testy regresyjne

Wprowadź automatyczne testy weryfikujące ograniczenia czasowe. Jeśli zmiana kodu spowoduje naruszenie ograniczeń czasowych, test powinien zakończyć się niepowodzeniem. Zapobiega to regresji i zapewnia, że system pozostaje zgodny z modelem. Zintegruj te testy z pipeline’em ciągłej integracji.

Regularne audyty

Zaplanuj regularne audyty swoich diagramów czasowych. Przejrzyj je pod kątem najnowszego zachowania systemu. Aktualizuj model, aby odzwierciedlał wszelkie zmiany w sprzęcie, sieci lub architekturze oprogramowania. Trzymaj model jak najbardziej zbliżony do rzeczywistości.

🎯 Wnioski: Most między modelem a rzeczywistością

Rozwiązywanie problemówDiagramy czasowe UML to ćwiczenie precyzji i staranności. Wymaga głębokiego zrozumienia zarówno abstrakcyjnego modelu, jak i konkretnego systemu. Systematycznie weryfikując ograniczenia, analizując rozbieżności i utrzymując zgodność z innymi diagramami, możesz zapewnić, że system zachowuje się zgodnie z oczekiwaniami.

Pamiętaj, że celem nie jest doskonałość, ale przewidywalność. Gdy twój model i rzeczywistość są zsynchronizowane, budujesz zaufanie. Tworzysz systemy, które są niezawodne, wydajne i odpornościowe. Użyj strategii przedstawionych tutaj, aby diagnozować problemy, doskonalić modele i dostarczać oprogramowanie wysokiej jakości. Droga do zsynchronizowanego systemu wiedzie przez staranną analizę i ciągłe weryfikowanie.

Kluczowe wnioski

- Weryfikuj wcześnie: Sprawdź ograniczenia czasowe w fazie projektowania.

- Mierz często: Używaj profilowania do porównania modelu z rzeczywistością.

- Dokumentuj zmiany: Trzymaj swój model aktualny wraz z ewolucją systemu.

- Testuj przypadki graniczne: Zapewnij odporność pod obciążeniem i zmiennością.

Śledząc te praktyki, przekształcasz diagramy czasowe z statycznych rysunków w dynamiczne narzędzia sukcesu inżynierskiego. Różnica między działającym systemem a zawalającym się często tkwi w szczegółach czasu. Zwróć na nie uwagę, a twój system będzie działał niezawodnie.