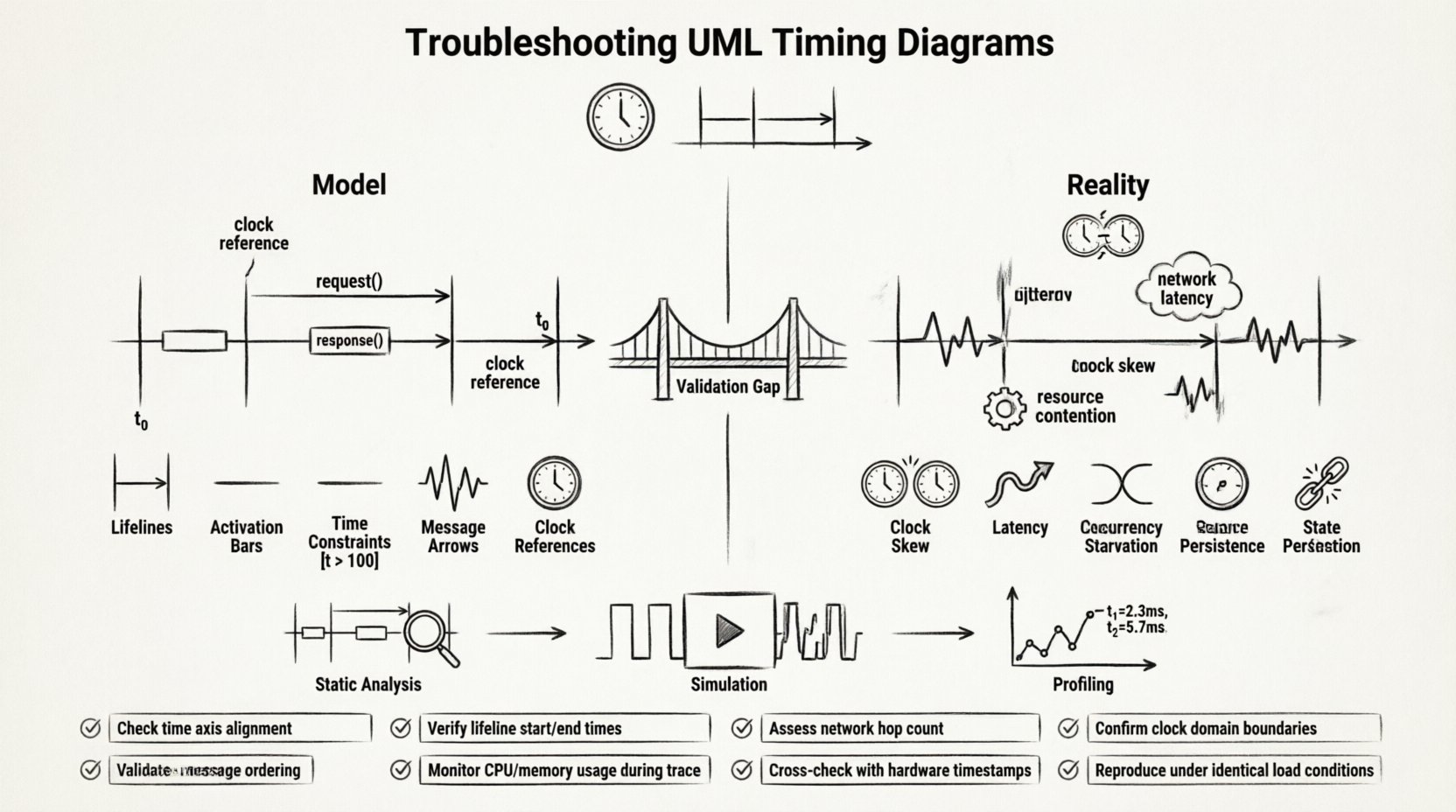

Cuando el abismo entre un modelo de diseño y la ejecución real del sistema se amplía, los equipos de ingeniería enfrentan desafíos críticos. Esto es particularmente cierto paraDiagramas de tiempo UML, que sirven como plano directriz para interacciones críticas en el tiempo. Estos diagramas muestran cómo se comportan los objetos con el paso del tiempo, especificando restricciones exactas sobre la llegada de mensajes y los cambios de estado. Sin embargo, a menudo surgen discrepancias durante la implementación. El código se comporta de forma diferente a como predice el modelo. Esta divergencia puede provocar condiciones de carrera, plazos perdidos y inestabilidad del sistema. Comprender cómo solucionar estas discrepancias es esencial para mantener la integridad del sistema.

Esta guía explora la mecánica de identificar y resolver anomalías de tiempo. Examinaremos los elementos estructurales de los modelos de tiempo, las causas comunes del desvío de comportamiento y métodos sistemáticos de validación. Al alinear tusrestricciones de tiempocon la realidad, aseguras que el sistema funcione de forma confiable bajo carga. Comencemos definiendo los componentes principales y dónde suelen originarse los errores.

🛑 La brecha entre la abstracción y la ejecución

Los diagramas de tiempo UML son representaciones abstractas. Simplifican realidades físicas complejas en lógica visual. Un modelo asume condiciones ideales: latencia de red cero, ciclos de reloj deterministas y disponibilidad inmediata de recursos. La realidad rara vez cumple con estas suposiciones. Cuando pasas de lafase de diseñoa lafase de despliegue, el entorno introduce ruido.

- Variabilidad del hardware:Los procesadores diferentes ejecutan instrucciones a velocidades variables.

- Jitter de red:Los tiempos de entrega de paquetes fluctúan en sistemas distribuidos.

- Contención de recursos:La memoria compartida o núcleos de CPU causan retrasos no previstos en aislamiento.

Cuando tucomportamiento del sistema no coincide con el modelo, a menudo es porque el modelo no tuvo en cuenta estos factores ambientales. Solucionar problemas requiere un cambio de la validación teórica a la verificación empírica. Debes tratar el diagrama no como un documento estático, sino como una hipótesis viva que necesita pruebas constantes.

🔍 Comprender la arquitectura del diagrama de tiempo

Antes de corregir errores, debes comprender los elementos que constituyen un diagrama de tiempo. Estos diagramas se diferencian de los diagramas de secuencia al poner un énfasis fuerte en el eje temporal. El eje horizontal representa el tiempo, mientras que el eje vertical representa laslíneas de vidade los objetos o procesos participantes.

1. Líneas de vida y ejes de tiempo

Las líneas de vida representan las entidades involucradas en la interacción. En un contexto de tiempo, cada línea de vida debe tener un reloj o referencia de tiempo definida. Si dos líneas de vida operan con relojes diferentes, surgen problemas de sincronización. Debes asegurarte de que las unidades de tiempo sean coherentes en todo el diagrama. Mezclar milisegundos con ciclos de reloj sin conversión conduce a errores de cálculo.

2. Barras de activación

Las barras de activación indican cuándo un objeto está realizando activamente una acción. En los diagramas de tiempo, la duración de estas barras es crítica. Si el modelo muestra una acción que dura 5 ms, pero el hardware tarda 10 ms, el sistema falla. Debes verificar la duración de cada activación contra el tiempo real de ejecución del bloque de código correspondiente.

3. Condiciones y guardas

Las condiciones en el eje del tiempo definen cuándo se permite una transición. A menudo se expresan como expresiones como[t > 100]. Si el modelo asume que una condición se cumple en t=100, pero el sistema la alcanza en t=105, los eventos posteriores se retrasan. Este retraso puede propagarse, afectando a procesos dependientes.

4. Mensajes y señales

Los mensajes son los desencadenantes que mueven al sistema de un estado a otro. En los diagramas de tiempo, la hora de llegada de un mensaje es explícita. El diagnóstico de fallos a menudo implica medir la hora real de llegada frente a la hora programada. Si los mensajes llegan fuera de orden, la lógica del modelo es inválida.

⚠️ Fuentes comunes de desajuste de comportamiento

Identificar la causa raíz de una discrepancia de tiempo es el primer paso en el diagnóstico de fallos. Hay categorías específicas de errores que ocurren con frecuencia. A continuación se presenta un desglose de las fuentes más comunes.

| Categoría | Descripción | Impacto |

|---|---|---|

| Ajuste de reloj | Discrepancia entre las fuentes de reloj de diferentes componentes. | Desincronización de procesos paralelos. |

| Suposiciones de latencia | Suponer que la latencia de red o del bus es cero o constante. | Faltas de plazos y errores de tiempo de espera. |

| Problemas de concurrencia | Varios hilos accediendo a recursos compartidos simultáneamente. | Bloqueos o condiciones de carrera. |

| Privación de recursos | CPU o memoria insuficientes disponibles para la tarea. | Ejecución retrasada de las barras de activación. |

| Persistencia de estado | El estado no se guarda correctamente entre los intervalos de tiempo. | Transiciones de estado incorrectas al reiniciar. |

Cruce de dominios de reloj

Una de las incidencias más frecuentes en el modelado de hardware y software de bajo nivel escruce de dominios de reloj. Si su sistema utiliza múltiples relojes, los diagramas de tiempo deben modelar explícitamente los puntos de sincronización. Si el modelo asume un solo reloj, pero la implementación utiliza dominios separados, las restricciones de tiempo se vuelven sin sentido. Debe tener en cuenta la latencia introducida por los sincronizadores.

Orden de los mensajes

Los diagramas de temporización a menudo implican un orden estricto de eventos. En la realidad, los paquetes de red o los mensajes entre procesos pueden llegar fuera de orden. Si su modelo asume que el mensaje A llega antes que el mensaje B, pero el sistema recibe primero el B, el flujo lógico se interrumpe. Esto es común en sistemas asíncronos dondegarantías de entrega no se aplican.

Retardos no deterministas

Algunos comportamientos del sistema son inherentemente no deterministas. La recolección de basura, el intercambio de memoria virtual y los algoritmos de planificación introducen variabilidad. Si su diagrama de temporización utiliza valores de tiempo fijos para estos procesos, el modelo fallará durante las pruebas de estrés. Debe utilizar rangos o tiempos de ejecución peor caso (WCET) en lugar de valores fijos.

🛠️ Metodologías para la validación y verificación

Una vez que haya identificado fuentes potenciales de error, necesita un método para validar el modelo frente al sistema. La validación no es una tarea única; es un proceso continuo a lo largo de todo el ciclo de vida del desarrollo.

1. Análisis estático del modelo

Antes de ejecutar cualquier código, analice el diagrama de temporización en busca de consistencia lógica. Verifique la presencia de bloqueos, bucles infinitos o estados inaccesibles. Asegúrese de que todas las restricciones de tiempo sean matemáticamente factibles. Si una tarea requiere 10 ms pero el período es de 5 ms, el modelo es inválido independientemente de la calidad del código.

- Verifique las cadenas de dependencia: Asegúrese de que ninguna tarea dependa de sí misma dentro del mismo intervalo de tiempo.

- Verifique el cumplimiento de los plazos: Confirme que la suma de los tiempos de ejecución no exceda el plazo.

- Analice el uso de recursos: Asegúrese de que las tareas concurrentes no excedan los recursos disponibles.

2. Simulación y emulación

La simulación le permite ejecutar el modelo en un entorno controlado. Puede inyectar retardos o fallos específicos para ver cómo responde el sistema. Esto ayuda a aislar problemas de temporización sin afectar el entorno de producción. Utilice la simulación para probar casos límite que son difíciles de reproducir en tiempo real.

- Inyecte latencia: Agregue retardos artificiales a los mensajes para probar la robustez.

- Pruebas de estrés: Ejecute el sistema a carga máxima para observar la degradación del tiempo.

- Inyección de fallos: Simule la pérdida o corrupción de mensajes para verificar el tiempo de recuperación.

3. Perfilado e instrumentación

Instrumentar el código con temporizadores y registros proporciona datos del mundo real. Compare los marcos de tiempo registrados con las predicciones del modelo. Este enfoque basado en datos revela dónde el modelo se desvía de la realidad. Busque patrones en la desviación. ¿Es consistente? ¿Es aleatorio? ¿Ocurrirá bajo condiciones específicas?

- Rastree la ejecución: Registre el tiempo de inicio y finalización de cada barra de activación.

- Monitoree la llegada de mensajes: Registre la marca de tiempo exacta de cada señal entrante.

- Correlacionar eventos:Mapear entradas de registro hacia elementos específicos en el diagrama de temporización.

🔄 Alineación con diagramas de secuencia y de estado

Un diagrama de temporización no existe de forma aislada. Forma parte de un conjunto más amplio de UML. A menudo surgen inconsistencias cuando el diagrama de temporización entra en conflicto con otros diagramas. Por ejemplo, unDiagrama de secuencia podría mostrar un flujo lógico, pero elDiagrama de temporizaciónmuestra una violación de temporización.

Consistencia entre diagramas

Asegúrese de que la secuencia de eventos en el diagrama de temporización coincida con el flujo lógico en el diagrama de secuencia. Si el diagrama de secuencia muestra un punto de decisión, el diagrama de temporización debe tener en cuenta el tiempo necesario para evaluar dicha decisión. Las discrepancias entre diagramas indican a menudo una mala comprensión de la lógica del sistema.

Integración con máquina de estados

Los diagramas de estado definen los estados en los que puede encontrarse un objeto. Los diagramas de temporización definen cuánto tiempo permanece el objeto en esos estados. Si el diagrama de temporización implica un cambio de estado que la máquina de estados no admite, se produce un conflicto. Debe sincronizar las transiciones de estado con las restricciones de temporización.

Alineación con casos de uso

Por último, asegúrese de que los requisitos de temporización respalden los casos de uso. Si un caso de uso requiere un tiempo de respuesta de 200 ms, el diagrama de temporización debe reflejar esta restricción. Si el modelo permite 500 ms, el sistema no cumplirá las expectativas del usuario. Alinee las restricciones de temporización con los requisitos funcionales.

📊 Lista de verificación diagnóstica para anomalías de temporización

Al realizar el diagnóstico, utilice una lista de verificación estructurada para asegurarse de que no se omitan pasos. Esta lista cubre las áreas críticas donde normalmente se ocultan los errores de temporización.

- ✓ Verificar la sincronización del reloj:¿Todos los componentes utilizan la misma referencia de tiempo?

- ✓ Comprobar el orden de los mensajes:¿Los mensajes llegan en el orden esperado?

- ✓ Validar tiempos de ejecución:¿Los tiempos reales de ejecución coinciden con las predicciones del modelo?

- ✓ Inspeccionar la contención de recursos:¿Hay suficiente CPU o memoria para las tareas programadas?

- ✓ Revisar las transiciones de estado:¿Las transiciones de estado ocurren dentro de la ventana de tiempo permitida?

- ✓ Probar casos límite:¿Cómo se comporta el sistema en los límites de las restricciones de temporización?

- ✓ Analizar la carga de red:¿La alta carga afecta los tiempos de entrega de mensajes?

- ✓ Confirmar fechas límite:¿Se cumplen todas las fechas límite críticas bajo carga máxima?

🛡️ Estrategias de mantenimiento a largo plazo

Aunque hayas resuelto las discrepancias iniciales, los modelos de tiempo requieren mantenimiento. Los sistemas evolucionan, al igual que sus requisitos. Un diagrama de tiempo que era preciso ayer puede ser obsoleto hoy.

Control de versiones para modelos

Trata tus diagramas como código. Guárdalos en sistemas de control de versiones. Esto te permite rastrear los cambios con el tiempo y volver a versiones anteriores si un nuevo cambio introduce problemas de tiempo. Documenta cada cambio en las restricciones de tiempo para mantener un historial claro.

Pruebas automatizadas de regresión

Implementa pruebas automatizadas que verifiquen las restricciones de tiempo. Si un cambio de código causa una violación de tiempo, la prueba debe fallar. Esto evita la regresión y asegura que el sistema permanezca conforme al modelo. Integra estas pruebas en tu pipeline de integración continua.

Auditorías regulares

Programa auditorías regulares de tus diagramas de tiempo. Revísalos contra el comportamiento más reciente del sistema. Actualiza el modelo para reflejar cualquier cambio en el hardware, red o arquitectura de software. Mantén el modelo lo más cercano a la realidad posible.

🎯 Conclusión: Cerrando la brecha entre el modelo y la realidad

Solución de problemasDiagramas de tiempo UMLes un ejercicio de precisión y diligencia. Requiere una comprensión profunda tanto del modelo abstracto como del sistema concreto. Al validar sistemáticamente las restricciones, analizar las discrepancias y mantener la alineación con otros diagramas, puedes asegurarte de que tu sistema funcione según lo previsto.

Recuerda que el objetivo no es la perfección, sino la previsibilidad. Cuando tu modelo y la realidad están alineados, generas confianza. Creas sistemas que son confiables, eficientes y robustos. Utiliza las estrategias descritas aquí para diagnosticar problemas, perfeccionar tus modelos y entregar software de alta calidad. El camino hacia un sistema sincronizado está pavimentado con un análisis cuidadoso y una verificación continua.

Puntos clave

- Valida temprano:Verifica las restricciones de tiempo durante la fase de diseño.

- Mide con frecuencia:Utiliza la depuración para comparar el modelo con la realidad.

- Documenta los cambios:Mantén tu modelo actualizado con la evolución del sistema.

- Prueba casos extremos:Asegura la robustez bajo estrés y variación.

Al seguir estas prácticas, transformas tus diagramas de tiempo de dibujos estáticos en herramientas dinámicas para el éxito de la ingeniería. La diferencia entre un sistema que funciona y uno que falla a menudo reside en los detalles del tiempo. Presta atención a ellos, y tu sistema funcionará de forma confiable.