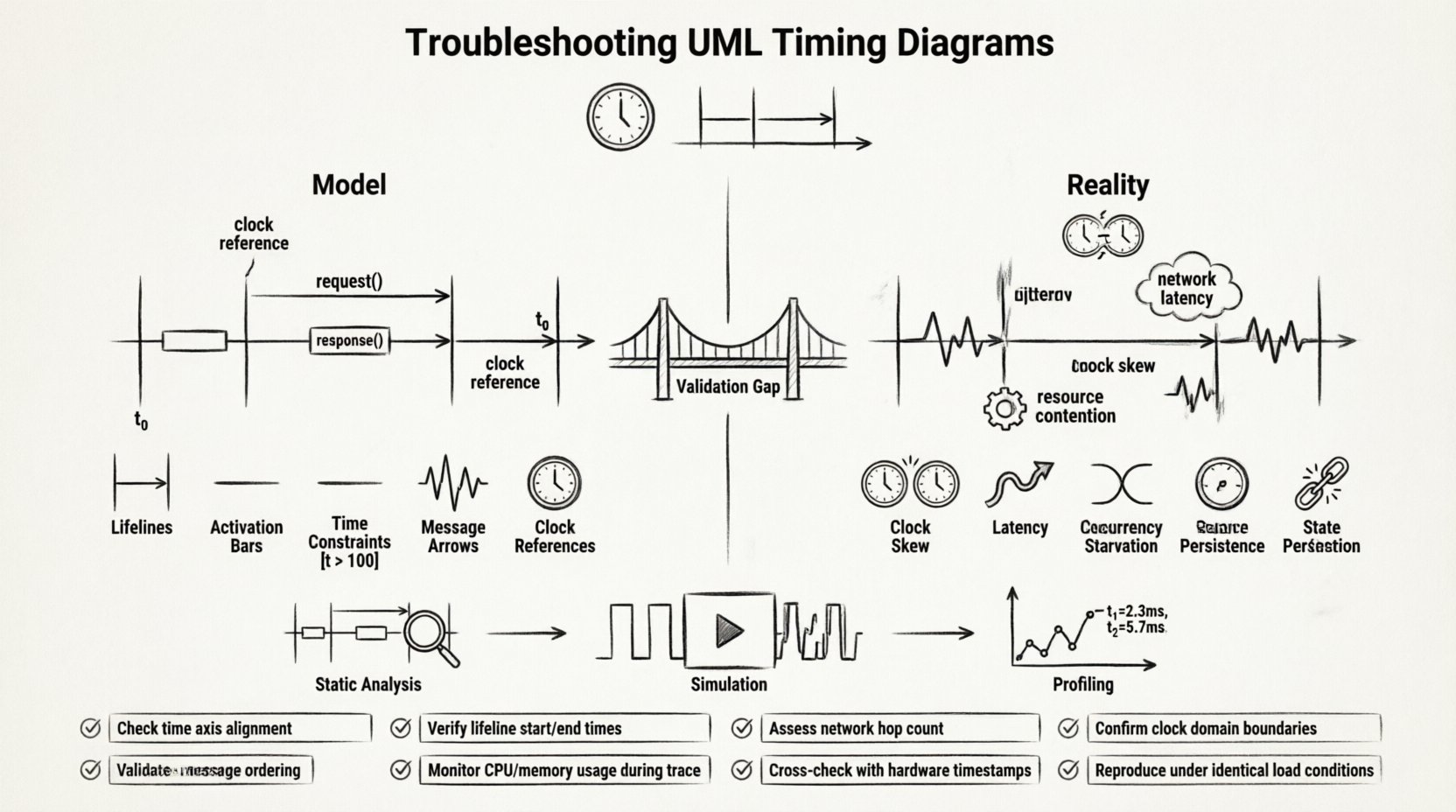

Lorsque l’écart entre un modèle de conception et l’exécution réelle du système s’agrandit, les équipes d’ingénierie font face à des défis critiques. C’est particulièrement vrai pourles diagrammes de timing UML, qui servent de plan directeur pour les interactions critiques dans le temps. Ces diagrammes montrent comment les objets se comportent au fil du temps, en précisant des contraintes exactes sur l’arrivée des messages et les changements d’état. Cependant, des écarts apparaissent souvent lors de l’implémentation. Le code se comporte différemment de ce que prédit le modèle. Ce décalage peut entraîner des conditions de course, des délais manqués et une instabilité du système. Comprendre comment dépanner ces incohérences est essentiel pour maintenir l’intégrité du système.

Ce guide explore les mécanismes pour identifier et résoudre les anomalies de temporisation. Nous examinerons les éléments structurels des modèles de temporisation, les causes courantes du décalage comportemental, et les méthodes systématiques de validation. En alignant voscontraintes de temporisationavec la réalité, vous vous assurez que le système fonctionne de manière fiable sous charge. Commençons par définir les composants fondamentaux et les origines habituelles des erreurs.

🛑 L’écart entre l’abstraction et l’exécution

Les diagrammes de timing UML sont des représentations abstraites. Ils simplifient des réalités physiques complexes en logique visuelle. Un modèle suppose des conditions idéales : latence réseau nulle, cycles d’horloge déterministes et disponibilité immédiate des ressources. La réalité adhère rarement à ces hypothèses. Lorsque vous passez de la phasede conceptionà la phasede déploiement, l’environnement introduit du bruit.

- Variabilité du matériel :Les processeurs différents exécutent les instructions à des vitesses variables.

- Jitter réseau :Les délais de livraison des paquets fluctuent dans les systèmes distribués.

- Contestation des ressources :La mémoire partagée ou les cœurs du processeur causent des délais non prévus en isolation.

Lorsque votrecomportement du système ne correspond pas au modèle, cela est souvent dû au fait que le modèle n’a pas pris en compte ces facteurs environnementaux. Le dépannage exige un changement de validation théorique vers une vérification empirique. Vous devez considérer le diagramme non pas comme un document statique, mais comme une hypothèse vivante qui nécessite un test constant.

🔍 Comprendre l’architecture du diagramme de timing

Avant de corriger les erreurs, vous devez comprendre les éléments qui constituent un diagramme de timing. Ces diagrammes se distinguent des diagrammes de séquence en mettant un accent particulier sur l’axe temporel. L’axe horizontal représente le temps, tandis que l’axe vertical représente leslignes de viedes objets ou processus participants.

1. Lignes de vie et axes du temps

Les lignes de vie représentent les entités impliquées dans l’interaction. Dans un contexte de temporisation, chaque ligne de vie doit avoir une horloge ou une référence temporelle définie. Si deux lignes de vie fonctionnent avec des horloges différentes, des problèmes de synchronisation apparaissent. Vous devez vous assurer que les unités de temps sont cohérentes sur l’ensemble du diagramme. Mélanger des millisecondes avec des cycles d’horloge sans conversion entraîne des erreurs de calcul.

2. Barres d’activation

Les barres d’activation indiquent quand un objet effectue activement une action. Dans les diagrammes de timing, la durée de ces barres est critique. Si le modèle indique qu’une action dure 5 ms, mais que le matériel en prend 10 ms, le système échoue. Vous devez vérifier la durée de chaque activation par rapport au temps d’exécution réel du bloc de code correspondant.

3. Conditions et gardes

Les conditions sur l’axe du temps définissent quand une transition est autorisée. Elles sont souvent exprimées sous forme d’expressions telles que [t > 100]. Si le modèle suppose qu’une condition est remplie à t=100, mais que le système l’atteint à t=105, les événements suivants sont retardés. Ce retard peut se propager, affectant les processus dépendants.

4. Messages et signaux

Les messages sont les déclencheurs qui transforment le système d’un état à un autre. Dans les diagrammes de temporisation, l’heure d’arrivée d’un message est explicite. Le dépannage consiste souvent à mesurer l’heure d’arrivée réelle par rapport à l’heure prévue. Si les messages arrivent dans le désordre, la logique du modèle devient invalide.

⚠️ Sources courantes de désynchronisation comportementale

Identifier la cause fondamentale d’un écart de temporisation est la première étape du dépannage. Il existe des catégories spécifiques d’erreurs qui se produisent fréquemment. Ci-dessous se trouve une analyse des sources les plus courantes.

| Catégorie | Description | Impact |

|---|---|---|

| Désynchronisation d’horloge | Écart entre les sources d’horloge de différents composants. | Désynchronisation des processus parallèles. |

| Hypothèses sur la latence | Supposer que la latence du réseau ou du bus est nulle ou constante. | Dépassement des délais et erreurs de temporisation. |

| Problèmes de concurrence | Plusieurs threads accédant simultanément à des ressources partagées. | Bloquages ou conditions de course. |

| Pénurie de ressources | CPU ou mémoire insuffisants disponibles pour la tâche. | Retard dans l’exécution des barres d’activation. |

| Persistance d’état | État non sauvegardé correctement entre les intervalles de temporisation. | Transitions d’état incorrectes au redémarrage. |

Croisement de domaine d’horloge

L’un des problèmes les plus fréquents dans la modélisation matérielle et logicielle de bas niveau est croisement de domaine d’horloge. Si votre système utilise plusieurs horloges, les diagrammes de temporisation doivent modéliser explicitement les points de synchronisation. Si le modèle suppose une seule horloge, mais que l’implémentation utilise des domaines distincts, les contraintes de temporisation deviennent sans sens. Vous devez tenir compte de la latence introduite par les synchronisateurs.

Ordre des messages

Les diagrammes de temporisation impliquent souvent un ordre strict des événements. En réalité, les paquets réseau ou les messages inter-processus peuvent arriver hors ordre. Si votre modèle suppose que le message A arrive avant le message B, mais que le système reçoit d’abord B, le flux logique se rompt. Cela est fréquent dans les systèmes asynchrones oùgaranties de livraison ne sont pas appliquées.

Délais non déterministes

Certains comportements de système sont intrinsèquement non déterministes. La collecte des déchets, l’échange de mémoire virtuelle et les algorithmes de planification introduisent une variabilité. Si votre diagramme de temporisation utilise des valeurs de temps fixes pour ces processus, le modèle échouera lors des tests de charge. Vous devez utiliser des plages ou des temps d’exécution pire cas (WCET) au lieu de valeurs fixes.

🛠️ Méthodologies de validation et de vérification

Une fois que vous avez identifié les sources potentielles d’erreur, vous avez besoin d’une méthode pour valider le modèle par rapport au système. La validation n’est pas une tâche ponctuelle ; c’est un processus continu tout au long du cycle de développement.

1. Analyse statique du modèle

Avant d’exécuter tout code, analysez le diagramme de temporisation pour vérifier sa cohérence logique. Vérifiez les blocages, les boucles infinies ou les états inaccessibles. Assurez-vous que toutes les contraintes de temps sont mathématiquement réalisables. Si une tâche nécessite 10 ms mais que la période est de 5 ms, le modèle est invalide, quelle que soit la qualité du code.

- Vérifiez les chaînes de dépendances : Assurez-vous qu’aucune tâche ne dépend d’elle-même dans la même fenêtre de temps.

- Vérifiez le respect des délais : Confirmez que la somme des temps d’exécution ne dépasse pas le délai.

- Analysez l’utilisation des ressources : Assurez-vous que les tâches concurrentes n’excèdent pas les ressources disponibles.

2. Simulation et émulation

La simulation vous permet d’exécuter le modèle dans un environnement contrôlé. Vous pouvez injecter des délais ou des pannes spécifiques pour observer la réaction du système. Cela permet d’isoler les problèmes de temporisation sans affecter l’environnement de production. Utilisez la simulation pour tester des cas limites difficiles à reproduire en temps réel.

- Injection de latence : Ajoutez des délais artificiels aux messages pour tester la robustesse.

- Tests de charge : Exécutez le système à charge maximale pour observer la dégradation du temporisation.

- Injection de pannes : Simulez la perte ou la corruption de messages pour vérifier le timing de récupération.

3. Profilage et instrumentation

Instrumenter le code avec des chronomètres et des journaux fournit des données du monde réel. Comparez les horodatages enregistrés aux prédictions du modèle. Cette approche fondée sur les données révèle où le modèle s’écarte de la réalité. Recherchez des motifs dans cet écart. Est-il constant ? Aléatoire ? Se produit-il dans des conditions spécifiques ?

- Suivi de l’exécution : Enregistrez l’heure de début et de fin de chaque barre d’activation.

- Surveillez l’arrivée des messages : Enregistrez l’horodatage exact de chaque signal entrant.

- Corréler les événements :Mapper les entrées de journalisation vers des éléments spécifiques du diagramme de temporisation.

🔄 Alignement avec les diagrammes de séquence et d’état

Un diagramme de temporisation n’existe pas en isolation. Il fait partie d’un ensemble plus large de diagrammes UML. Des incohérences apparaissent souvent lorsque le diagramme de temporisation entre en conflit avec d’autres diagrammes. Par exemple, un Diagramme de séquence pourrait montrer un flux logique, mais le Diagramme de temporisation montre une violation de temporisation.

Conformité entre les diagrammes

Assurez-vous que la séquence des événements dans le diagramme de temporisation correspond au flux logique du diagramme de séquence. Si le diagramme de séquence montre un point de décision, le diagramme de temporisation doit tenir compte du temps nécessaire pour évaluer cette décision. Les écarts entre les diagrammes indiquent souvent une mauvaise compréhension de la logique du système.

Intégration de la machine à états

Les diagrammes d’état définissent les états qu’un objet peut occuper. Les diagrammes de temporisation définissent la durée pendant laquelle l’objet reste dans ces états. Si le diagramme de temporisation implique un changement d’état que la machine à états ne supporte pas, un conflit survient. Vous devez synchroniser les transitions d’état avec les contraintes de temporisation.

Alignement avec les cas d’utilisation

Enfin, assurez-vous que les exigences de temporisation soutiennent les cas d’utilisation. Si un cas d’utilisation exige un temps de réponse de 200 ms, le diagramme de temporisation doit refléter cette contrainte. Si le modèle autorise 500 ms, le système ne répondra pas aux attentes des utilisateurs. Alignez les contraintes de temporisation avec les exigences fonctionnelles.

📊 Liste de contrôle diagnostique pour les anomalies de temporisation

Lors du dépannage, utilisez une liste de contrôle structurée pour vous assurer de ne rien omettre. Cette liste couvre les zones critiques où les erreurs de temporisation se cachent souvent.

- ✓ Vérifier la synchronisation de l’horloge :Tous les composants utilisent-ils la même référence temporelle ?

- ✓ Vérifier l’ordre des messages :Les messages arrivent-ils dans l’ordre attendu ?

- ✓ Valider les temps d’exécution :Les temps réels d’exécution correspondent-ils aux prédictions du modèle ?

- ✓ Examiner la contention des ressources :Y a-t-il assez de CPU ou de mémoire pour les tâches planifiées ?

- ✓ Revoir les transitions d’état :Les changements d’état ont-ils lieu dans la fenêtre de temps autorisée ?

- ✓ Tester les cas limites :Comment le système se comporte-t-il aux limites des contraintes de temporisation ?

- ✓ Analyser la charge du réseau :Une forte charge affecte-t-elle les délais de livraison des messages ?

- ✓ Confirmer les délais : Tous les délais critiques sont-ils respectés sous charge maximale ?

🛡️ Stratégies de maintenance à long terme

Même après avoir résolu les écarts initiaux, les modèles de temporisation nécessitent une maintenance. Les systèmes évoluent, tout comme leurs exigences. Un diagramme de temporisation qui était précis hier peut être obsolète aujourd’hui.

Contrôle de version pour les modèles

Traitez vos diagrammes comme du code. Stockez-les dans des systèmes de contrôle de version. Cela vous permet de suivre les modifications dans le temps et de revenir à des versions antérieures si une nouvelle modification introduit des problèmes de temporisation. Documentez chaque modification des contraintes de temporisation pour conserver un historique clair.

Tests de régression automatisés

Mettez en œuvre des tests automatisés qui vérifient les contraintes de temporisation. Si un changement de code provoque une violation de temporisation, le test doit échouer. Cela évite la régression et garantit que le système reste conforme au modèle. Intégrez ces tests à votre pipeline d’intégration continue.

Audits réguliers

Programmez des audits réguliers de vos diagrammes de temporisation. Revoyez-les à la lumière du comportement le plus récent du système. Mettez à jour le modèle pour refléter tout changement dans l’architecture matérielle, réseau ou logicielle. Gardez le modèle aussi proche de la réalité que possible.

🎯 Conclusion : Comblage de l’écart entre modèle et réalité

DépannageDiagrammes de temporisation UML est un exercice de précision et de diligence. Il exige une compréhension approfondie à la fois du modèle abstrait et du système concret. En validant systématiquement les contraintes, en analysant les écarts et en maintenant l’alignement avec les autres diagrammes, vous pouvez garantir que votre système se comporte comme prévu.

Souvenez-vous que l’objectif n’est pas la perfection, mais la prévisibilité. Lorsque votre modèle et la réalité sont alignés, vous instaurez la confiance. Vous créez des systèmes fiables, efficaces et robustes. Utilisez les stratégies décrites ici pour diagnostiquer les problèmes, affiner vos modèles et livrer un logiciel de haute qualité. Le chemin vers un système synchronisé est pavé d’analyses soigneuses et de vérifications continues.

Points clés

- Validez tôt : Vérifiez les contraintes de temporisation pendant la phase de conception.

- Mesurez souvent : Utilisez le profilage pour comparer le modèle à la réalité.

- Documentez les modifications : Maintenez votre modèle à jour avec l’évolution du système.

- Testez les cas limites : Assurez la robustesse sous charge et variations.

En suivant ces pratiques, vous transformez vos diagrammes de temporisation, passant de dessins statiques à des outils dynamiques pour réussir l’ingénierie. La différence entre un système fonctionnel et un système défaillant réside souvent dans les détails du temps. Prêtez-y attention, et votre système fonctionnera de manière fiable.