Merancang sistem real-time yang tangguh membutuhkan pemahaman yang tepat mengenai hubungan temporal antar komponen. Meskipun diagram urutan menggambarkan alur logis pesan, mereka sering kali gagal ketika batasan waktu menjadi kritis. Di sinilah Diagram Waktu UML menjadi sangat penting bagi arsitek sistem. Ini memberikan pandangan khusus tentang bagaimana objek berinteraksi seiring waktu, dengan fokus pada perubahan status dan batasan waktu.

Dalam panduan ini, kita mengeksplorasi mekanisme pemodelan penanganan interupsi dan pemicu asinkron dalam notasi ini. Konsep-konsep ini sangat penting untuk sistem tertanam, aplikasi kritis keselamatan, dan arsitektur terdistribusi di mana latensi dan konkurensi menentukan keberhasilan.

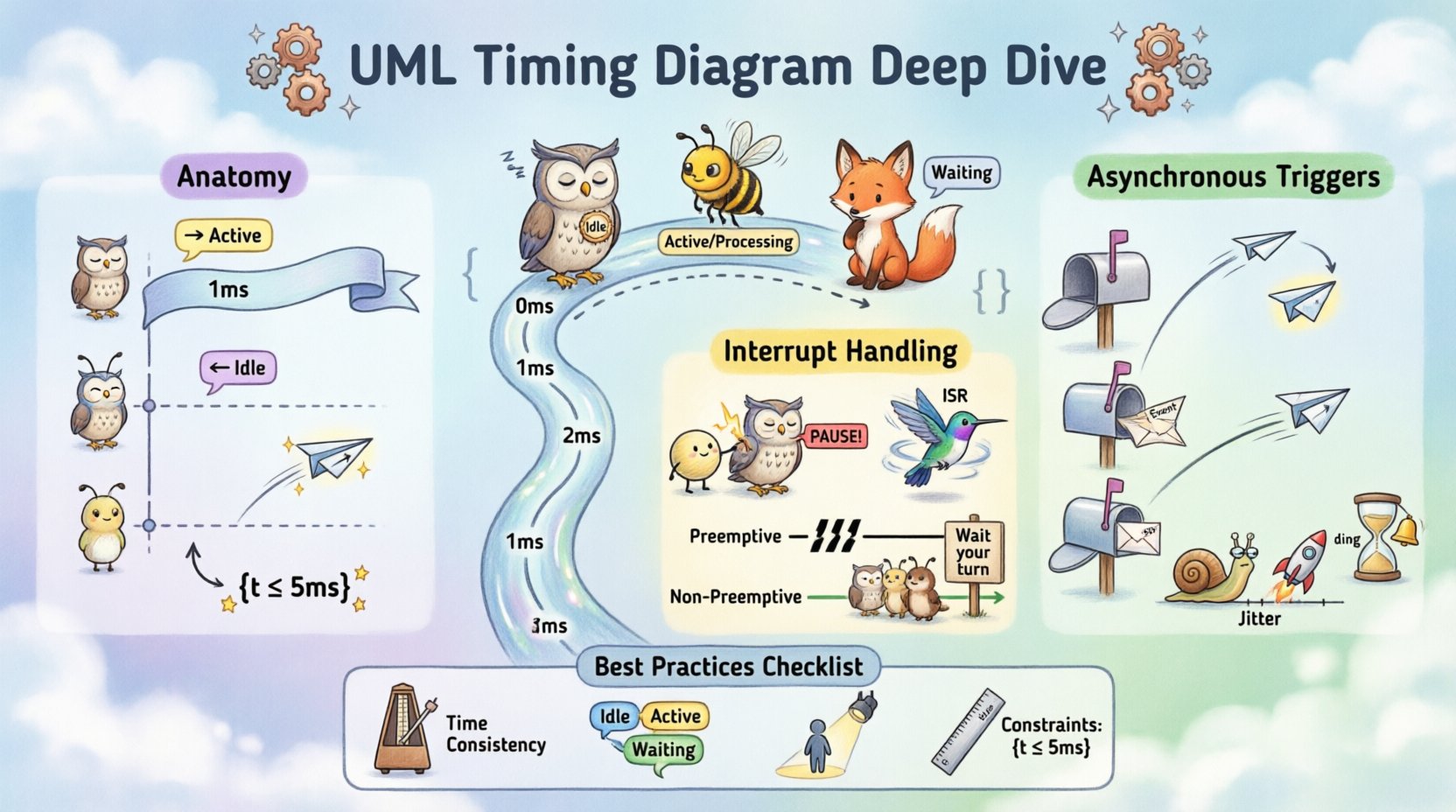

🔍 Anatomi Diagram Waktu

Sebelum memasuki interaksi kompleks seperti interupsi, sangat penting untuk memahami elemen-elemen dasar. Diagram waktu menggambarkan perilaku objek atau garis hidup selama durasi tertentu.

- Garis Hidup:Garis vertikal yang mewakili keberadaan suatu objek atau komponen. Waktu bergerak ke bawah.

- Sumbu Waktu:Sumbu horizontal yang mewakili timeline, sering diberi tanda satuan seperti milidetik atau siklus jam.

- Spesifikasi Status:Area persegi panjang sepanjang garis hidup yang menunjukkan status objek pada waktu tertentu (misalnya, Aktif, Tidak Aktif, Tidur).

- Pesan:Panah yang melintasi garis hidup yang menunjukkan transmisi sinyal atau pemanggilan metode.

- Kendala:Teks yang dikelilingi kurung kurawal

{...}yang menentukan persyaratan waktu atau kondisi.

Berbeda dengan diagram UML lainnya, diagram waktu secara eksplisit bersifat temporal. Ini tidak hanya menunjukkan *apa* yang terjadi, tetapi *kapan* hal itu terjadi relatif terhadap peristiwa lain.

⚙️ Pemodelan Penanganan Interupsi

Interupsi adalah sinyal eksternal yang secara sementara menghentikan alur eksekusi normal untuk menangani peristiwa berprioritas tinggi. Dalam diagram waktu, merepresentasikannya memerlukan perbedaan yang jelas antara tugas yang dihentikan dan rutin layanan interupsi.

1. Jenis-Jenis Interupsi

Memahami sifat interupsi sangat penting untuk pemodelan yang akurat. Secara umum, kita mengkategorikannya menjadi dua jenis utama:

- Interupsi Perangkat Keras:Dipicu oleh peristiwa fisik (misalnya, sinyal sensor, kedatangan paket jaringan).

- Interupsi Perangkat Lunak:Dipicu oleh peristiwa internal (misalnya, pembagian dengan nol, waktu timer habis).

2. Representasi Visual

Untuk menggambarkan interupsi, diagram harus menunjukkan penghentian proses saat ini. Hal ini dicapai melalui petunjuk visual khusus:

- Bilah Aktivasi:Bilah proses saat ini dihentikan oleh lonjakan atau perpindahan ke bilah aktivasi yang berbeda yang mewakili handler interupsi.

- Tingkat Prioritas:Label yang menunjukkan thread atau proses mana yang menguasai CPU pada setiap saat.

- Titik Kembali:Indikasi yang jelas tentang di mana eksekusi dilanjutkan setelah interupsi ditangani.

3. Preemptif vs. Non-Preemptif

Diagram waktu membantu menjelaskan strategi penjadwalan. Dalam sistem preemptif, diagram menunjukkan pemutusan tajam pada tugas dengan prioritas rendah. Dalam sistem non-preemptif, permintaan interupsi disimpan dalam antrian hingga tugas saat ini secara sukarela menyerahkan kendali.

| Fitur | Interupsi Preemptif | Interupsi Non-Preemptif |

|---|---|---|

| Waktu Tanggapan | Segera | Ditunda hingga menyerah kendali |

| Pergantian Konteks | Diperlukan | Tidak selalu diperlukan |

| Kompleksitas Diagram | Tinggi (Banyak aktivasi) | Lebih Rendah (Satu aktivasi) |

| Kasus Penggunaan | Lingkaran kontrol waktu nyata | Pemrosesan batch |

📡 Pemicu dan Sinyal Asinkron

Pemicu asinkron terjadi ketika pengirim tidak menunggu penerima siap. Ini umum terjadi dalam arsitektur berbasis peristiwa. Diagram waktu adalah alat ideal untuk memvisualisasikan latensi antara pemicu dan respons.

1. Sifat Asinkron

Dalam pemanggilan sinkron, pemanggil menunggu nilai kembali. Dalam pemicu asinkron, pemanggil mengirim sinyal dan melanjutkan. Diagram ini mencerminkan hal ini dengan menunjukkan panah pesan berakhir tanpa panah kembali segera.

- Fire-and-Forget: Pesan dikirim, dan pengirim melanjutkan segera.

- Antrian Peristiwa: Penerima memproses peristiwa kemudian, yang dapat ditampilkan sebagai penundaan pada batang aktivasi penerima.

- Callback: Pesan berikutnya kembali ke pengirim setelah tugas asinkron selesai.

2. Pemodelan Latensi

Salah satu alasan utama menggunakan diagram waktu adalah untuk menganalisis latensi. Saat memodelkan pemicu asinkron, perhatian khusus harus diberikan pada selisih waktu antara pembentukan peristiwa dan eksekusi handler.

- Jitter:Variabilitas dalam waktu yang dibutuhkan untuk memproses pemicu.

- Throughput:Volume peristiwa asinkron yang dapat ditangani sistem dalam jangka waktu tertentu.

- Timeout: Jika respons tidak diterima dalam waktu yang ditentukan, diagram harus menunjukkan status timeout.

🔄 Menggabungkan Interupsi dan Pemicu Asinkron

Sistem yang kompleks sering melibatkan kedua mekanisme secara bersamaan. Interupsi perangkat keras mungkin memicu peristiwa perangkat lunak, yang kemudian menambahkan tugas asinkron ke antrian. Memodelkan interaksi ini membutuhkan penyusunan lapisan lifeline dengan hati-hati.

1. Tumpukan Interupsi

Ketika terjadi interupsi selama operasi asinkron, diagram waktu harus menunjukkan penyisipan bersarang. Tugas asinkron saat ini dijeda, handler interupsi dijalankan, dan kemudian tugas asal dilanjutkan.

Skenario ini menyoroti kemungkinan kondisi persaingan. Jika dua interupsi terjadi secara berurutan, diagram membantu memverifikasi apakah sistem memiliki kapasitas untuk menangani kedalaman tumpukan tanpa overflow.

2. Ketersinambungan dan Sumber Daya Bersama

Pemicu asinkron sering mengakses sumber daya bersama. Jika interupsi mengubah sumber daya saat tugas asinkron sedang membacanya, korupsi data dapat terjadi. Diagram waktu dapat menggambarkan waktu pengambilan dan pelepasan kunci.

- Pemblokiran: Tunjukkan durasi sumber daya dipegang.

- Blokir: Tunjukkan kapan tugas menunggu kunci.

- Inversi Prioritas: Gambarkan skenario di mana tugas berprioritas rendah memegang kunci yang dibutuhkan oleh interupsi berprioritas tinggi.

🛠 Praktik Terbaik untuk Diagram Waktu

Membuat diagram waktu yang efektif membutuhkan disiplin. Kejelasan lebih penting daripada detail yang terlalu lengkap dalam setiap kasus.

- Konsistensi Skala Waktu: Pastikan sumbu waktu konsisten di seluruh diagram. Memperbesar bagian tertentu diperbolehkan, tetapi konteks global sangat penting.

- Kesadaran Status:Gunakan warna atau arsiran yang berbeda untuk status yang berbeda (misalnya, Idle, Processing, Menunggu).

- Lifeline Minimal:Jangan sertakan setiap objek dalam sistem. Fokus hanya pada objek yang terlibat dalam hubungan waktu yang sedang dianalisis.

- Notasi Kendala:Gunakan

{t <= 5ms}sintaks untuk mendefinisikan batas waktu keras secara jelas.

⚠️ Kesalahan Umum dan Solusinya

Bahkan modeler berpengalaman membuat kesalahan saat menerjemahkan logika temporal ke dalam diagram. Berikut ini adalah masalah umum dan cara mengatasinya.

| Kesalahan | Dampak | Solusi |

|---|---|---|

| Mengabaikan Latensi | Sistem gagal memenuhi batas waktu | Sertakan penundaan transmisi dalam panah pesan |

| Lifeline yang Tumpang Tindih | Kerancuan pada urutan eksekusi | Gunakan penyelarasan vertikal secara ketat; hindari persilangan panah sebisa mungkin |

| Kendala yang Tidak Jelas | Keraguan dalam persyaratan | Gunakan nilai numerik yang spesifik (misalnya, 200ns alih-alih cepat) |

| Interupsi yang Hilang | Latensi tersembunyi dalam jalur kritis | Gambar secara eksplisit rutin layanan interupsi sebagai batang aktivasi terpisah |

🧪 Verifikasi dan Validasi

Setelah diagram waktu dibuat, diagram tersebut berfungsi sebagai dasar untuk verifikasi. Insinyur dapat membandingkan perilaku yang dimodelkan dengan log sistem aktual.

- Pelacakan:Peta elemen diagram ke fungsi kode. Verifikasi bahwa batasan waktu dalam diagram sesuai dengan implementasi kode.

- Simulasi:Gunakan diagram untuk mensimulasikan skenario terburuk. Apa yang terjadi jika frekuensi interupsi menjadi dua kali lipat?

- Pengujian:Hasilkan kasus uji berdasarkan jendela waktu yang ditentukan dalam diagram. Pastikan sistem berperilaku dengan benar dalam toleransi yang ditentukan.

🧠 Pertimbangan Lanjutan

Untuk sistem yang sangat kompleks, diagram waktu standar mungkin memerlukan perluasan. Pertimbangkan teknik pemodelan lanjutan berikut ini.

1. Diagram Waktu Hierarkis

Ketika suatu subsistem memiliki perilaku waktu yang kompleks sendiri, kelilingi dengan diagram bawah. Diagram induk menunjukkan subsistem sebagai satu garis hidup tunggal dengan ringkasan perilaku waktu-nya. Ini mengurangi kekacauan sambil tetap mempertahankan detail.

2. Arsitektur Berbasis Waktu

Dalam sistem berbasis waktu, tindakan terjadi pada siklus jam tertentu terlepas dari peristiwa. Diagram harus menunjukkan kisi ketat atau sinyal jam yang berjalan sejajar dengan garis hidup untuk menunjukkan momen-momen sinkron ini.

3. Energi dan Waktu

Pada perangkat yang menggunakan baterai, waktu secara langsung memengaruhi konsumsi daya. Tugas yang berjalan lebih lama mengonsumsi lebih banyak energi. Menambahkan sumbu konsumsi daya atau anotasi pada diagram waktu dapat membantu mengoptimalkan efisiensi energi sekaligus kinerja.

📝 Ringkasan Konsep Kunci

Untuk merangkum poin-poin penting dari pembahasan mendalam ini:

- Diagram Waktuadalah standar untuk memvisualisasikan perilaku temporal dalam UML.

- Interupsimemerlukan batang aktivasi yang berbeda untuk menunjukkan preempsi dan pergantian konteks.

- Pemicu Asinkronharus mempertimbangkan latensi dan mekanisme antrian.

- Batasanharus eksplisit dan numerik untuk menghindari ambiguitas.

- Kongurensimasalah seperti kondisi persaingan paling baik diidentifikasi oleh tumpang tindih garis hidup.

Dengan mematuhi prinsip pemodelan ini, arsitek sistem dapat membuat gambaran jelas untuk perilaku waktu nyata. Ini mengurangi risiko cacat yang berkaitan dengan waktu selama tahap implementasi. Upaya yang diinvestasikan dalam diagram waktu yang akurat akan terbayar selama integrasi sistem dan debugging.

🚀 Bergerak Maju

Menerapkan diagram ini adalah proses iteratif. Mulailah dengan batasan waktu tingkat tinggi dan sempurnakan seiring matangnya desain. Kolaborasi antara insinyur perangkat lunak dan desainer perangkat keras sangat penting, karena waktu sering melibatkan kedua bidang tersebut. Diagram ini berfungsi sebagai bahasa bersama antara kelompok-kelompok tersebut.

Ingatlah bahwa diagram adalah dokumen yang hidup. Seiring sistem berkembang, diagram waktu harus diperbarui untuk mencerminkan kebutuhan baru atau perubahan perangkat keras. Ini memastikan bahwa dokumentasi tetap menjadi referensi yang valid untuk pemeliharaan dan pemecahan masalah di masa depan.

Pemodelan yang efektif terhadap interupsi dan pemicu asinkron memastikan bahwa sistem Anda tidak hanya benar secara fungsional, tetapi juga kuat secara temporal. Ini adalah dasar dari arsitektur perangkat lunak real-time yang dapat diandalkan.