Memahami perilaku temporal sangat penting saat merancang sistem di mana milidetik menjadi hal yang menentukan. Dalam bidang rekayasa embedded dan pemrosesan konkuren, representasi statis interaksi objek sering kali gagal menangkap nuansa kecepatan eksekusi dan batas waktu. Di sinilah diagram waktu UML menjadi aset yang tak tergantikan. Diagram ini menyediakan mekanisme visual yang tepat untuk menganalisis perubahan status dan pertukaran pesan seiring waktu.

Panduan ini mengeksplorasi mekanisme, sintaks, dan penerapan praktis diagram waktu. Panduan ini dirancang untuk para pengembang yang membutuhkan kejelasan mengenai latensi, jitter, dan transisi status tanpa bergantung pada klaim pemasaran yang berlebihan. Kami akan membahas bagaimana membuat diagram ini, menafsirkan batasan yang kompleks, serta memanfaatkannya untuk verifikasi sistem kritis terhadap keselamatan.

🔍 Apa itu Diagram Waktu?

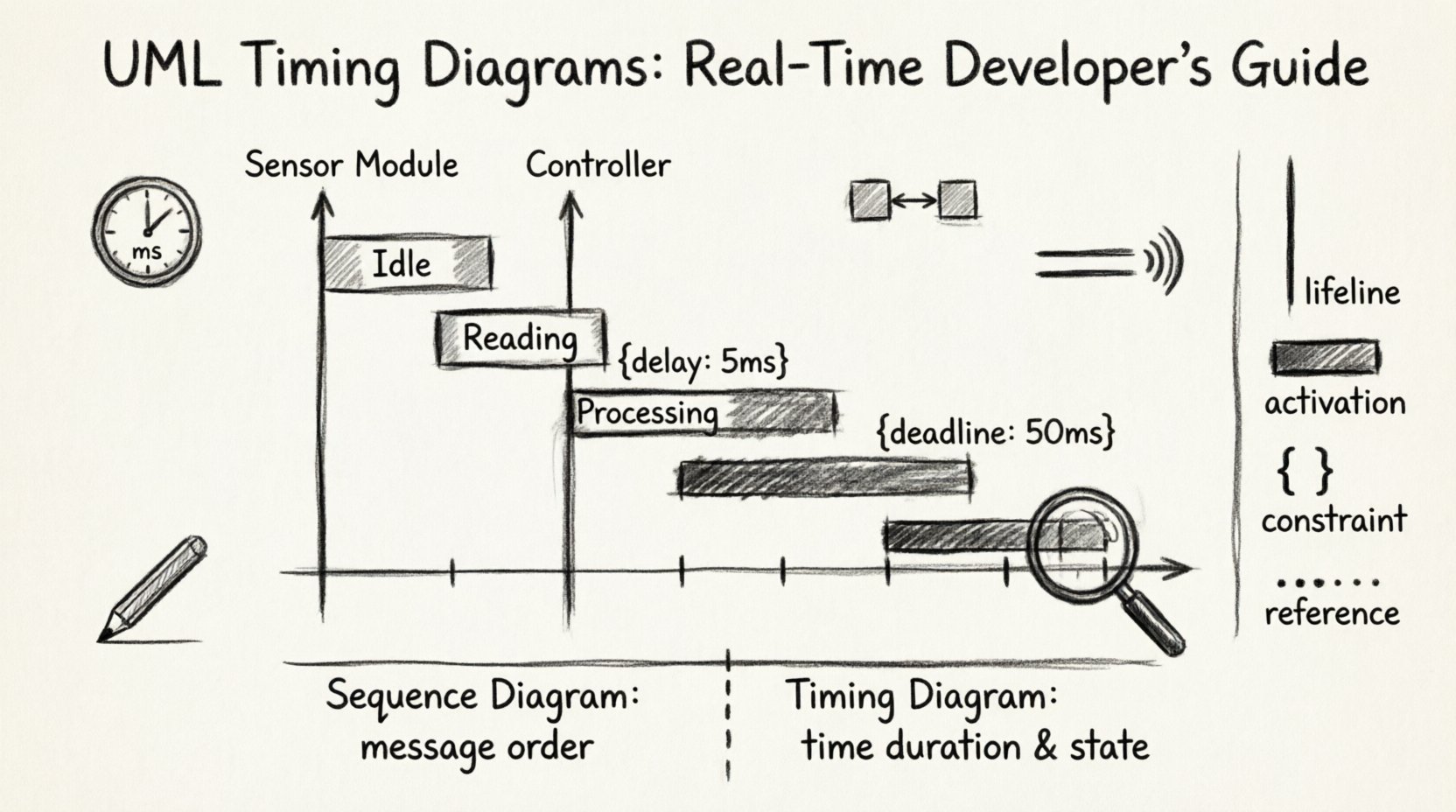

Diagram waktu adalah bentuk khusus dari diagram interaksi dalam Bahasa Pemodelan Terpadu (UML). Berbeda dengan diagram urutan yang fokus pada urutan logis pesan, diagram waktu menekankan hubungan temporal yang tepat antar peristiwa. Diagram ini memetakan status objek atau lifeline terhadap sumbu waktu.

- Presisi Temporal: Mereka memungkinkan penentuan waktu absolut (misalnya, 50ms) atau waktu relatif (misalnya, 10 unit setelah peristiwa A).

- Visibilitas Status: Mereka secara eksplisit menunjukkan berapa lama suatu objek tetap berada dalam status tertentu.

- Kongurensi: Mereka menggambarkan bagaimana beberapa proses beroperasi secara bersamaan tanpa benturan.

Bagi pengembang sistem real-time, perbedaan ini sangat penting. Suatu sistem mungkin berfungsi secara logis dengan benar tetapi gagal karena melewatkan batas waktu. Diagram waktu membantu memvisualisasikan kegagalan ini sebelum kode ditulis.

🧩 Komponen Utama dan Sintaks

Untuk menggunakan teknik pemodelan ini secara efektif, seseorang harus memahami blok bangunan dasarnya. Setiap diagram terdiri dari sistem koordinat yang didefinisikan oleh waktu dan status.

1. Lifeline

Lifeline mewakili keberadaan suatu objek, proses, atau thread dalam periode waktu tertentu. Mereka digambarkan sebagai garis vertikal.

- Sumbu Vertikal: Mewakili entitas atau komponen yang berbeda.

- Sumbu Horizontal: Mewakili perkembangan waktu.

- Batas Aktivitas:Persegi panjang yang ditempatkan pada lifeline menunjukkan kapan suatu objek sedang secara aktif melakukan operasi atau berada dalam status tertentu.

2. Kotak Status

Kotak status adalah wilayah persegi panjang sepanjang lifeline yang menunjukkan kondisi objek. Transisi dari satu status ke status lainnya ditandai dengan garis batas.

- Status Terisi: Menunjukkan objek sedang memproses atau menahan sumber daya.

- Status Idle: Menunjukkan objek sedang menunggu atau tidak aktif.

- Penandaan:Status harus diberi nama dengan jelas (misalnya, “Memproses, Menunggu, Diblokir).

3. Kendala Sumbu Waktu

Waktu tidak selalu linier dalam sistem waktu nyata. Kendala dapat menentukan batas untuk kejadian.

- Kendala Penundaan: Menentukan waktu minimum sebelum suatu kejadian dapat terjadi.

- Kendala Batas Waktu: Menentukan waktu maksimum yang diizinkan untuk penyelesaian suatu kejadian.

- Periodisitas: Menentukan kejadian berulang pada interval tetap.

⏱️ Memvisualisasikan Perubahan Status

Nilai utama dari diagram waktu terletak pada kemampuannya untuk menggambarkan transisi status. Dalam diagram urutan, Anda melihat bahwa pesan A dikirim sebelum pesan B. Dalam diagram waktu, Anda melihat bahwa sistem berada dalam Status X selama 10 milidetik sebelum beralih ke Status Y.

Pertimbangkan loop pembacaan sensor. Sistem berputar melalui Idle, Membaca, dan Memproses.

- Idle: CPU menunggu pemicu. Durasi bersifat variabel.

- Membaca: Perangkat keras sedang aktif. Durasi ditentukan oleh spesifikasi perangkat keras.

- Memproses: Algoritma sedang berjalan. Durasi tergantung pada ukuran data.

Dengan memetakan durasi ini, seorang pengembang dapat mengidentifikasi bottleneck. Jika Memproses status melebihi batas waktu untuk siklus berikutnya Idle siklus, sistem berisiko kehilangan data.

🔒 Kendala dan Ekspresi Waktu

Sistem waktu nyata sering membutuhkan kepatuhan ketat terhadap batas waktu. UML memungkinkan notasi kendala ini menggunakan label teks atau ekspresi khusus yang terlampir pada elemen diagram.

1. Waktu Absolut

Menggunakan waktu absolut menetapkan diagram pada titik awal tertentu. Misalnya, suatu peristiwa harus terjadi pada waktu t=100ms.

- Kasus penggunaan: Sinkronisasi dengan sumber jam eksternal.

- Manfaat: Memastikan koordinasi di seluruh komponen terdistribusi.

2. Waktu Relatif

Waktu relatif mendefinisikan interval berdasarkan peristiwa sebelumnya. Misalnya, ‘Peristiwa B terjadi 50ms setelah Peristiwa A’.

- Kasus penggunaan: Menangani latensi interupsi.

- Manfaat: Mengabstraksikan diagram dari waktu mulai tertentu, fokus pada aliran.

3. Ketidaksamaan

Kendala dapat dinyatakan sebagai ketidaksamaan, seperti t < 50ms. Ini menunjukkan batas waktu keras.

- Batas Waktu Keras: Gagal memenuhi ini mengakibatkan kegagalan sistem.

- Batas Waktu Lunak: Kinerja menurun jika terlewat, tetapi sistem tetap berjalan.

🔄 Konesi dan Paralelisme

Perangkat lunak modern jarang berjalan pada satu thread. Diagram waktu sangat unggul dalam menunjukkan jalur eksekusi paralel. Ketika terdapat beberapa lifeline, kemajuan horizontal mereka menunjukkan aktivitas bersamaan.

1. Interleaving

Interleaving terjadi ketika tugas-tugas berbagi satu prosesor. Diagram menunjukkan potongan waktu eksekusi untuk tugas-tugas yang berbeda.

- Preemptif: Tugas dengan prioritas tinggi mengganggu tugas dengan prioritas rendah.

- Non-Preemptif: Tugas berjalan hingga selesai sebelum beralih.

2. Persaingan Sumber Daya

Ketika dua lifeline membutuhkan sumber daya yang sama, satu harus menunggu. Diagram ini memvisualisasikan waktu tunggu sebagai celah dalam batang aktivasi.

- Penyegelan: Satu lifeline memegang sumber daya sementara yang lain menunggu.

- Kebuntuan: Jika dua lifeline menunggu satu sama lain tanpa akhir, diagram akan menunjukkan keadaan menunggu yang terus-menerus.

⚖️ Diagram Waktu vs. Diagram Urutan

Kedua diagram memodelkan interaksi, tetapi fokusnya berbeda secara signifikan. Mengaburkan keduanya dapat menyebabkan kesalahan desain.

| Fitur | Diagram Urutan | Diagram Waktu |

|---|---|---|

| Fokus Utama | Urutan pesan | Durasi waktu dan keadaan |

| Sumbu Waktu | Implisit (urutan logis) | Jelas (kuantitatif) |

| Representasi Keadaan | Minimal atau tersirat | Rinci dan jelas |

| Kasus Penggunaan | Alur logika, desain protokol | Analisis latensi, penjadwalan |

| Kompleksitas | Tinggi untuk logika yang kompleks | Tinggi untuk presisi waktu |

Pengembang sering menggunakan diagram urutan untuk desain logika awal dan diagram waktu untuk verifikasi real-time berikutnya. Pendekatan dua langkah ini menjamin kebenaran dan kinerja.

🛠️ Pedoman Konstruksi

Membuat diagram yang bermanfaat membutuhkan disiplin. Diagram yang berantakan menyembunyikan data waktu yang seharusnya disampaikan.

1. Tentukan Skala Waktu

Sebelum menggambar, tentukan satuan pengukuran. Apakah milidetik, siklus CPU, atau tick abstrak? Konsistensi sangat penting. Menggabungkan satuan yang berbeda menyebabkan kebingungan.

2. Kelompokkan Kegiatan yang Terkait

Kelompokkan lifeline yang termasuk dalam subsistem yang sama. Gunakan kotak atau bingkai untuk memisahkan modul secara visual. Ini mengurangi beban kognitif.

3. Beri Label Batasan Secara Jelas

Jangan menyembunyikan batasan waktu dalam teks kecil. Tempatkan di dekat batang aktivasi atau panah pesan yang relevan. Gunakan notasi standar seperti{delay: 5ms}.

4. Sederhanakan Kotak Status

Jangan tampilkan setiap mikro-status. Fokus pada status yang memengaruhi waktu. Jika suatu status memiliki durasi yang dapat diabaikan, gabungkan dengan aktivitas di sekitarnya.

5. Validasi dengan Data

Pastikan nilai waktu bukan perkiraan. Nilai tersebut harus diperoleh dari data profiling, spesifikasi perangkat keras, atau analisis waktu eksekusi terburuk (WCET).

🚨 Kesalahan Umum dan Tantangan

Bahkan insinyur berpengalaman menghadapi kesulitan saat memodelkan waktu. Mengenali kesalahan ini sejak dini mencegah pekerjaan ulang.

1. Terlalu Rumit

Mencoba memodelkan seluruh sistem dalam satu diagram adalah kesalahan umum. Satu diagram harus fokus pada interaksi atau subsistem tertentu. Pisahkan sistem yang kompleks menjadi tampilan waktu yang lebih kecil.

2. Mengabaikan Jitter

Jitter adalah variasi dalam latensi. Diagram waktu sering menunjukkan jalur ideal. Namun, sistem nyata memiliki variasi. Pertimbangkan menambahkan rentang (misalnya, 10ms ± 2ms) untuk mewakili jitter.

3. Statis vs. Dinamis

Diagram waktu sering merupakan representasi statis dari perilaku dinamis. Mereka tidak mempertimbangkan pengecualian saat runtime kecuali secara eksplisit dimodelkan. Pastikan diagram Anda mencakup skenario penanganan kesalahan.

4. Keterbatasan Alat

Meskipun banyak alat tersedia, beberapa mengalami kesulitan dengan batasan waktu yang kompleks. Pastikan lingkungan pemodelan mendukung notasi khusus yang Anda butuhkan, seperti batasan bersarang atau sumbu waktu tidak linier.

📊 Referensi: Simbol-Simbol Notasi Umum

Rujuk tabel ini untuk simbol standar yang digunakan dalam diagram waktu.

| Simbol | Makna |

|---|---|

| Garis Vertikal | Lifeline (Objek/Thread) |

| Batas Persegi Panjang pada Garis | Aktivasi atau Status |

| Panah dengan Label | Pesan atau Sinyal |

| Kotak dengan Teks | Deskripsi Status |

| Kurung dengan Teks | Kendala (misalnya, delay, batas waktu) |

| Garis Putus-putus | Referensi atau Tautan |

| Tanda Pada Sumbu Waktu | Penanda Satuan Waktu |

🧠 Penjelajahan Mendalam: Analisis Sistem Real-Time

Bagi pengembang sistem tertanam, diagram waktu lebih dari sekadar gambar; ini adalah kontrak. Diagram ini mendefinisikan perilaku yang diharapkan dari perangkat keras dan perangkat lunak dalam kondisi tertentu.

1. Latensi Interupsi

Interupsi mengganggu alur normal. Diagram waktu membantu menghitung waktu maksimum antara sinyal interupsi dan mulainya rutin layanan interupsi (ISR).

- Pergantian Konteks: Waktu yang dibutuhkan untuk menyimpan register.

- Waktu Pengiriman:Waktu untuk menemukan handler ISR.

- Eksekusi:Waktu untuk menjalankan kode handler.

2. Persaingan Bus

Pada sistem multi-core, bus bersama dapat menjadi hambatan. Diagram ini menunjukkan kapan komponen mengakses bus dan berapa lama mereka menggunakannya.

- Arbitrase:Siapa yang mendapatkan akses terlebih dahulu?

- Status Tunggu:Berapa lama komponen menunggu bus?

3. Manajemen Daya

Diagram waktu juga membantu dalam pemodelan daya. Dengan mengetahui kapan CPU aktif dibandingkan sedang tidak digunakan, insinyur dapat merencanakan status hemat daya.

- Waktu Idle: Jendela di mana daya dapat disimpan.

- Waktu Bangun:Waktu yang dibutuhkan untuk kembali beroperasi penuh.

✅ Praktik Terbaik untuk Pemeliharaan

Diagram adalah dokumen yang hidup. Saat kebutuhan berubah, diagram harus berubah pula.

- Kontrol Versi:Perlakukan diagram seperti kode. Simpan di repositori.

- Pelacakan:Hubungkan elemen diagram dengan kebutuhan. Ini memastikan setiap batasan waktu dapat dipertanggungjawabkan.

- Siklus Tinjauan:Sertakan tinjauan diagram dalam tahap desain. Rekan kerja dapat mengidentifikasi konflik waktu yang mungkin terlewat oleh desainer utama.

- Otomasi:Di mana memungkinkan, hasilkan kasus uji dari diagram untuk memverifikasi perilaku waktu secara otomatis.

📝 Ringkasan Poin Penting

Diagram waktu UML menawarkan metode ketat untuk memvisualisasikan hubungan temporal dalam sistem perangkat lunak dan perangkat keras. Ini menghubungkan celah antara alur logis dan kenyataan fisik.

- Fokus pada Waktu:Gunakan saat durasi penting, bukan hanya urutan.

- Tentukan Batasan:Tandai jatuh tempo dan keterlambatan dengan jelas.

- Visualisasikan Status: Tunjukkan berapa lama objek tetap dalam kondisi tertentu.

- Kelola Keparalelan:Peta jalur eksekusi paralel untuk menemukan titik persaingan.

- Iterasi:Sempurnakan diagram seiring data profil menjadi tersedia.

Dengan mengintegrasikan diagram waktu ke dalam siklus pengembangan, tim dapat mengurangi risiko kegagalan waktu nyata. Pendekatan ini melampaui kebenaran teoritis menuju jaminan kinerja praktis. Ini memastikan sistem berperilaku tidak hanya seperti yang dimaksudkan, tetapi juga dalam batas ketat lingkungan yang diharapkan.

Bagi mereka yang bekerja pada aplikasi kritis keselamatan, seperti kontrol otomotif atau perangkat medis, tingkat detail ini tidak dapat ditawar. Ini memberikan bukti yang diperlukan untuk memvalidasi bahwa sistem akan memenuhi persyaratan temporalnya di bawah semua kondisi yang diharapkan.

Menerapkan praktik ini membutuhkan usaha dan disiplin. Namun, manfaatnya adalah sistem yang dapat diprediksi, handal, dan berkinerja tinggi. Dalam dunia pengembangan waktu nyata, prediktabilitas adalah bentuk keandalan tertinggi.