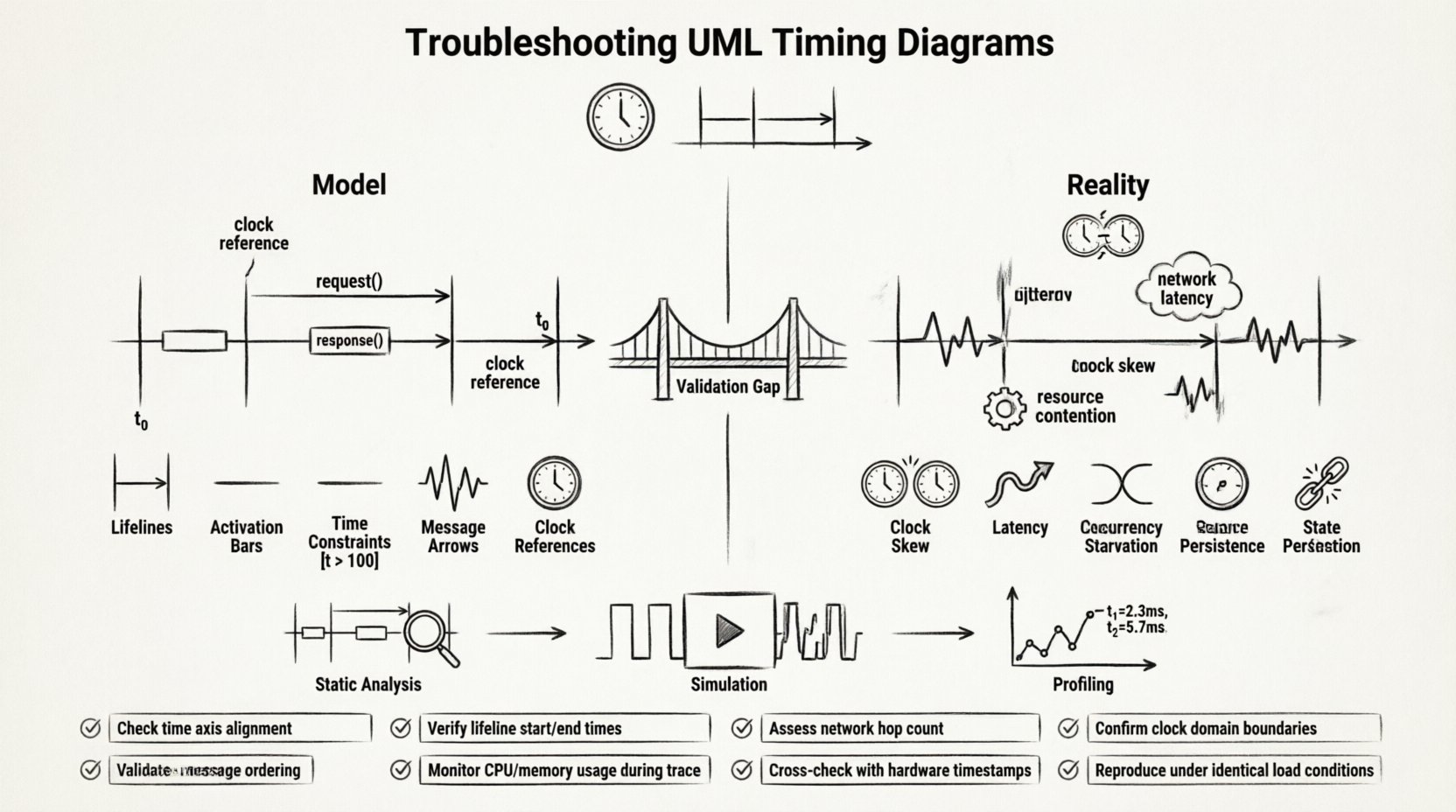

設計モデルと実際のシステム実行との間の乖離が広がると、エンジニアリングチームは重要な課題に直面する。特にUMLタイミング図、時間的に重要な相互作用のための設計図として機能する。これらの図は、オブジェクトが時間とともにどのように振る舞うかを明示し、メッセージの到着や状態変化に厳密な制約を設ける。しかし、実装段階でしばしば不一致が生じる。コードの動作がモデルの予測と異なる。この乖離は、レースコンディションやデッドラインの逸脱、システムの不安定性を引き起こす可能性がある。こうした不一致をトラブルシューティングする方法を理解することは、システムの整合性を維持するために不可欠である。

このガイドでは、タイミング異常を特定・解決するメカニズムについて探求する。タイミングモデルの構造的要素、行動のずれの一般的な原因、検証のための体系的な手法を検討する。あなたのタイミング制約を現実と一致させることで、システムが負荷下でも信頼性を保って動作することを保証できる。まず、コアとなる構成要素を定義し、エラーが通常発生する場所を明らかにしよう。

🛑 抽象化と実行の間のギャップ

UMLタイミング図は抽象的な表現である。複雑な物理的現実を視覚的な論理に簡略化する。モデルは理想的な状態を仮定する:ネットワーク遅延ゼロ、決定論的なクロックサイクル、即時利用可能なリソース。現実の世界では、こうした仮定に従うことはめったにない。設計段階から展開段階へ移行するとき、環境がノイズを導入する。

- ハードウェアのばらつき:異なるプロセッサは、命令を異なる速度で実行する。

- ネットワークジッター:パケットの配送時間は分散システムで変動する。

- リソース競合:共有メモリやCPUコアは、孤立して予測できない遅延を引き起こす。

あなたのシステムの動作がモデルと一致しないその理由は、モデルがこれらの環境要因を考慮できなかったためであることが多い。トラブルシューティングには、理論的検証から実証的検証へのシフトが必要となる。図を静的な文書ではなく、常に検証が必要な動的な仮説として扱わなければならない。

🔍 タイミング図のアーキテクチャの理解

エラーを修正する前に、タイミング図を構成する要素を理解する必要がある。これらの図は、時間軸に重点を置く点で、シーケンス図と異なる。水平軸は時間を表し、垂直軸は参加するオブジェクトやプロセスのライフラインを表す。

1. ライフラインと時間軸

ライフラインは、相互作用に関与するエンティティを表す。タイミングの文脈では、各ライフラインに明確なクロックまたは時間基準が必要である。2つのライフラインが異なるクロックで動作すると、同期の問題が生じる。図全体で時間単位が一貫していることを確認しなければならない。ミリ秒とクロックサイクルを変換せずに混在させると、計算エラーが発生する。

2. アクティベーションバー

アクティベーションバーは、オブジェクトがアクティブに動作している時間を示す。タイミング図では、これらのバーの持続時間が極めて重要である。モデルが5msのアクションを示しているが、ハードウェアが10msかかってしまう場合、システムは失敗する。すべてのアクティベーションの持続時間を、対応するコードブロックの実際の実行時間と照合して確認する必要がある。

3. 条件とガード

時間軸上の条件は、遷移が許可されるタイミングを定義する。これらはしばしば「[t > 100]」のような式で表現される。[t > 100]モデルが t=100 で条件が満たされていると仮定しているが、システムが t=105 に到達した場合、その後のイベントは遅延する。この遅延は連鎖的に発生し、依存するプロセスに影響を与える可能性がある。

4. メッセージとシグナル

メッセージは、システムを一つの状態から別の状態へ移行させるトリガーである。タイミング図では、メッセージの到着時刻が明示されている。トラブルシューティングでは、実際の到着時刻とスケジュールされた時刻を比較することが多い。メッセージが順序通りに到着しない場合、モデルの論理は無効となる。

⚠️ 挙動の不一致の主な原因

タイミングのずれの根本原因を特定することは、トラブルシューティングの第一歩である。頻繁に発生する特定のエラーのカテゴリが存在する。以下に、最も一般的な原因の概要を示す。

| カテゴリ | 説明 | 影響 |

|---|---|---|

| クロックスキュー | 異なるコンポーネント間のクロックソースの差異。 | 並列プロセスの同期のずれ。 |

| レイテンシの仮定 | ネットワークやバスのレイテンシがゼロまたは一定であると仮定すること。 | デッドラインの逸脱やタイムアウトエラー。 |

| 同時実行の問題 | 複数のスレッドが共有リソースを同時にアクセスすること。 | デッドロックやレースコンディション。 |

| リソース枯渇 | タスクに必要なCPUやメモリが不足している。 | アクティベーションバーの実行が遅延する。 |

| 状態の永続性 | タイミング間隔の間に状態が正しく保存されていない。 | 再起動時の不正な状態遷移。 |

クロックドメインクロッシング

ハードウェアおよび低レベルのソフトウェアモデリングにおける最も頻繁な問題の一つはクロックドメインクロッシングである。システムに複数のクロックを使用している場合、タイミング図は同期ポイントを明示的にモデル化しなければならない。モデルが単一のクロックを仮定しているが、実装では別々のドメインを使用している場合、タイミング制約は意味をなさなくなる。同期器によって生じるレイテンシを考慮しなければならない。

メッセージの順序

タイミング図はしばしばイベントの厳密な順序を示唆する。実際には、ネットワークパケットやプロセス間メッセージが順不同で到着することがある。モデルがメッセージAがメッセージBより前に到着すると仮定しているが、システムがBを先に受信した場合、論理フローが破綻する。これは非同期システムでよく見られる現象であり、配信保証が強制されない。

非決定的遅延

一部のシステム動作は本質的に非決定的である。ガベージコレクション、仮想メモリのスワッピング、スケジューリングアルゴリズムは変動性をもたらす。これらのプロセスに固定時間値を使用している場合、ストレステスト時にモデルは失敗する。固定値ではなく、範囲または最悪実行時間(WCET)を使用しなければならない。

🛠️ 検証と検査のための手法

潜在的なエラー源を特定した後は、モデルをシステムに対して検証するための方法が必要となる。検証は一度きりの作業ではなく、開発ライフサイクル全体にわたる継続的なプロセスである。

1. モデルの静的解析

コードを実行する前に、タイミング図の論理的一貫性を解析する。デッドロック、無限ループ、到達不能状態がないか確認する。すべての時間制約が数学的に可能であることを確認する。たとえば、タスクに10msが必要だが周期が5msの場合、コードの品質に関わらずモデルは無効となる。

- 依存関係チェーンの確認:同じ時間窓内で、タスクが自分自身に依存していないことを確認する。

- デッドライン遵守の確認:実行時間の合計がデッドラインを超えないことを確認する。

- リソース使用状況の分析:並行タスクが利用可能なリソースを超えないことを確認する。

2. シミュレーションとエミュレーション

シミュレーションにより、制御された環境でモデルを実行できる。特定の遅延や障害を注入して、システムの反応を確認できる。これにより、本番環境に影響を与えずにタイミング問題を特定できる。リアルタイムでは再現が難しいエッジケースをテストするためにシミュレーションを使用する。

- 遅延の注入:メッセージに人工的な遅延を加え、耐障害性をテストする。

- ストレステスト:システムを最大負荷で実行し、タイミングの劣化を観察する。

- 障害の注入:メッセージの喪失や破損をシミュレートして、回復タイミングを確認する。

3. プロファイリングとインストルメンテーション

タイマーとログをコードに組み込むことで、現実世界のデータが得られる。記録されたタイムスタンプをモデルの予測と比較する。このデータ駆動型のアプローチにより、モデルが現実からどの点でずれているかが明らかになる。ずれのパターンを確認する。一貫しているか?ランダムか?特定の条件下で発生するか?

- 実行のトレース:すべてのアクティベーションバーの開始時刻と終了時刻を記録する。

- メッセージ到着の監視:すべての受信信号の正確なタイムスタンプを記録する。

- イベントを関連付ける:ログエントリをタイミング図内の特定の要素にマッピングする。

🔄 シーケンス図およびステート図との整合性

タイミング図は孤立して存在するものではない。それはより大きなUMLセットの一部である。タイミング図が他の図と矛盾する場合、しばしば一貫性の問題が生じる。例えば、シーケンス図は論理的なフローを示すかもしれないが、タイミング図タイミング図はタイミング違反を示す。

図間の一貫性

タイミング図内のイベントの順序が、シーケンス図内の論理フローと一致していることを確認する。シーケンス図に決定ポイントが示されている場合、タイミング図はその決定を評価するのに要する時間を考慮しなければならない。図の間に差異があることは、システム論理の誤解を示していることが多い。

ステートマシンの統合

ステート図は、オブジェクトが取りうる状態を定義する。タイミング図は、オブジェクトがその状態にどのくらい滞在するかを定義する。タイミング図がステートマシンがサポートしない状態遷移を示している場合、衝突が生じる。状態遷移をタイミング制約と同期させる必要がある。

ユースケースとの整合性

最後に、タイミング要件がユースケースをサポートしていることを確認する。ユースケースで200msの応答時間を要する場合、タイミング図はこの制約を反映しなければならない。モデルが500msを許容している場合、システムはユーザーの期待を満たさない。タイミング制約を機能要件と一致させる。

📊 タイミング異常の診断チェックリスト

トラブルシューティングを行う際は、構造化されたチェックリストを使用して、ステップの漏れがないことを確認する。このリストは、タイミングエラーが通常隠れている重要な領域をカバーしている。

- ✓ クロック同期の確認:すべてのコンポーネントが同じ時間基準を使用しているか?

- ✓ メッセージの順序の確認:メッセージが予想される順序で到着しているか?

- ✓ 実行時間の検証:実際の実行時間はモデルの予測と一致しているか?

- ✓ リソース競合の確認:スケジュールされたタスクに十分なCPUまたはメモリがあるか?

- ✓ 状態遷移の確認:状態変化が許容される時間枠内に発生しているか?

- ✓ 端末ケースのテスト:タイミング制約の境界でシステムはどのように振る舞うか?

- ✓ ネットワーク負荷の分析:高トラフィックがメッセージの配信時間に影響するか?

- ✓ デッドラインの確認: ピーク負荷下でもすべての重要なデッドラインが満たされていますか?

🛡️ 長期的な保守戦略

初期の不一致を解決した後も、タイミングモデルの保守は必要です。システムは進化し、その要件も変化します。昨日正確だったタイミング図は、今日には陳腐化している可能性があります。

モデルのバージョン管理

図をコードとして扱いましょう。バージョン管理システムに保存してください。これにより、時間の経過とともに変更を追跡でき、新しい変更によってタイミングの問題が発生した場合に以前のバージョンに戻すことができます。タイミング制約のすべての変更を記録することで、明確な履歴を維持できます。

自動化されたレグレッションテスト

タイミング制約を検証する自動テストを導入してください。コードの変更によってタイミング違反が発生した場合、テストは失敗すべきです。これによりレグレッションを防ぎ、システムがモデルと整合した状態を維持できます。これらのテストを継続的インテグレーションパイプラインに統合してください。

定期的な監査

タイミング図の定期的な監査をスケジュールしてください。最新のシステム動作と照らし合わせてレビューしてください。ハードウェア、ネットワーク、またはソフトウェアアーキテクチャの変更がある場合は、モデルを更新して反映させましょう。モデルを現実にできるだけ近づけてください。

🎯 結論:モデルと現実の隔たりを埋める

トラブルシューティングUMLタイミング図は正確さと注意深さの習練です。抽象的なモデルと現実のシステムの両方に対する深い理解が求められます。制約を体系的に検証し、不一致を分析し、他の図と整合性を保つことで、システムが意図した通りに動作することを確実にできます。

完璧を目指すのではなく、予測可能性を目指すことを思い出してください。モデルと現実が一致しているとき、信頼が築かれます。信頼性が高く、効率的で、頑強なシステムを構築できます。ここに示した戦略を活用して問題を診断し、モデルを改善し、高品質なソフトウェアを提供しましょう。同期されたシステムへの道は、慎重な分析と継続的な検証の上に築かれます。

主な教訓

- 早期に検証する:設計段階でタイミング制約を確認する。

- 頻繁に測定する:プロファイリングを用いてモデルと現実を比較する。

- 変更を記録する:システムの進化に合わせてモデルを最新の状態に保つ。

- エッジケースをテストする:ストレスや変動下での耐性を確保する。

これらの実践を守ることで、タイミング図を静的な図からエンジニアリングの成功をもたらす動的なツールに変えることができます。動作するシステムと失敗するシステムの違いは、しばしば時間の詳細にあります。それらに注意を払い、あなたのシステムは信頼性を発揮するでしょう。