組み込みシステムおよびリアルタイムコンピューティングの分野において、時間的正確性は単なる好みではなく、必須である。センサデータを扱う際、情報が到着する時刻は、情報そのものと同様に重要であることが多い。レイテンシ、ジッター、処理ウィンドウは、システムが安全に動作するか、悲劇的な失敗を起こすかを決定する。本ガイドでは、UMLタイミング図を用いたセンサデータ処理フローの最適化をテーマに実践的な事例研究を検討する。時間的関係を可視化することで、エンジニアがボトルネックを特定し、ハードウェアコストを増加させることなく性能を向上させる構造的変更を実施できる方法を検討する。

ここでの目的は新しいツールを導入することではなく、モデリングアプローチを洗練させることである。データフローから時間フローへと焦点を移すことで、標準的なシーケンス図がしばしば見逃す隠れた依存関係をチームが発見できる。本ドキュメントでは、一般的なIoTセンサネットワークアーキテクチャに時間制約を適用する際の手法、分析プロセス、および測定可能な成果について詳述する。

📊 組み込みシステムにおける時間的制約の理解

組み込みシステムは厳格なリソース制限の下で動作する。メモリ、処理能力、エネルギーは有限のリソースである。複数のセンサが中央処理ユニットにデータを供給する場合、データ取得の順序とタイミングは複雑になる。ポーリング機構は短時間のイベントを逃す可能性がある。割り込みハンドラは重要なタスクを資源不足に陥らせる。時間の明確なマップがなければ、これらの問題はデプロイまで見えないまま残る。

標準的なフローチャートは「何が起こるかを記述する。シーケンス図は「誰が誰と話すかを記述する。タイミング図は「いつものが互いに対していつ起こるかを記述する。この違いは、信号を処理する機会の期間が物理的な世界によって定義されるセンサネットワークにおいて極めて重要である。

重要な時間的メトリクス

- レイテンシ: センサのトリガーからデータが利用可能になるまでの合計遅延。

- ジッター: 複数のイベント間でのレイテンシのばらつき。

- スループット: 単位時間あたりに処理されるデータ量。

- デッドライン: データが無効になる前にタスクが完了できる最大許容時間。

これらのメトリクスに対処するには、時間を明示的に捉えるモデルが必要である。UMLタイミング図は、この分析のための座標系を提供し、イベントを水平方向の時間軸上に配置できるようにする。

🛠️ UMLタイミング図の構造

このモデリング技法を効果的に活用するには、その構成要素を理解する必要がある。シーケンス図がオブジェクト間の相互作用に注目するのに対し、タイミング図は時間の経過に伴うオブジェクトの状態に注目する。水平軸は時間であり、左から右へと進行する。垂直軸は個別のオブジェクト、ライフライン、または変数を表す。

基本要素

- ライフライン: オブジェクトまたは変数の期間にわたる存在を表す。

- 状態発生: オブジェクトが特定の状態にあることを示す(例:アイドル, アクティブ, スリープ中).

- 条件: 条件が真または偽でなければならない時間間隔。

- イベント: 特定の時間にアクションが発生する(例:割り込み発生).

- 信号: ライフライン間を渡されるメッセージで、タイミングが注釈付き。

センサ処理の図を構築する際、ライフラインは通常、センサハードウェア、割り込みコントローラ、メイン処理スレッド、通信バスを表す。これらの間に正確なタイミング制約を設けることで、データが待機している場所や処理パワーが無駄になっている場所が明らかになる。

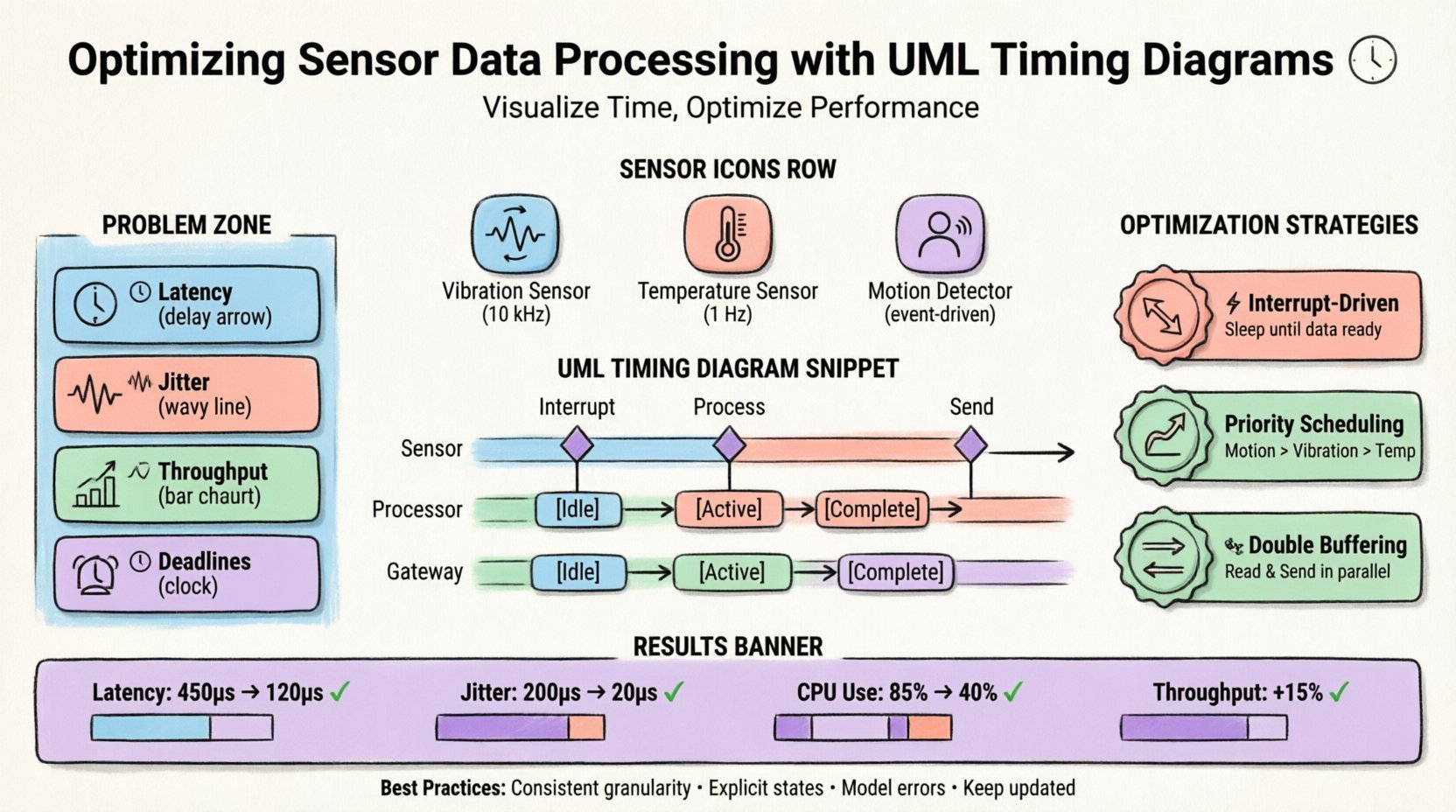

📡 センサネットワークのシナリオ

工業環境に展開された監視システムを検討する。このシステムは3つの異なるデータソースからデータを集約する:

- 振動センサ:機械の健全性を監視するための高頻度サンプリング(10 kHz)。

- 温度センサ:安全限界を監視するための低頻度サンプリング(1 Hz)。

- 運動検出器:セキュリティアラーム用のイベント駆動型トリガー。

これらのセンサは、データを集約しクラウドゲートウェイに送信しなければならないマイコンに接続されている。初期設計では、すべてのセンサを順次チェックする単一のポーリングループを使用していた。実装は簡単だったが、このアプローチは遅延に顕著なばらつきをもたらした。

システムアーキテクチャ概要

| コンポーネント | 役割 | タイミング要件 |

|---|---|---|

| 振動センサ | 高速取得 | 最大100μsの遅延 |

| 温度センサー | 定期的なモニタリング | 最大100msの遅延 |

| 運動検出器 | イベント検出 | 最大500μsの遅延 |

| クラウドゲートウェイ | データ送信 | 最大2秒の遅延 |

課題は共有バスにあった。振動センサーが高速アクセスを要求した際、温度センサーおよび運動センサーは遅延を経験した。初期モデルはバス競合や割り込み優先度を考慮しておらず、重要な状況下でデッドラインを逸脱する結果となった。

🔍 遅延およびジッター問題の特定

最適化の第一歩は、既存のポーリングコードに基づいてベースラインとなるUMLタイミング図を作成することだった。この視覚的表現により、いくつかの重要な非効率が浮き彫りになった。

観察されたボトルネック

- ポーリングのオーバーヘッド:メインループは、新しいデータが準備されていなくても毎秒10,000回振動センサーをチェックしていた。これにより、他のタスクに使用できるCPUサイクルが消費されていた。

- 割り込みブロッキング:運動検出器は割り込みに依存していたが、振動センサーが長時間バスを占有していたため、運動信号の伝達が遅延した。

- データバッファリング:中間データは単一のバッファに格納されていたため、ゲートウェイへの送信とセンサー読み取りが同時に発生した際にボトルネックが生じた。

タイミング図によりジッターが可視化された。運動トリガーと実際の処理の間の時間は、振動サンプリングのフェーズによって200μsから400μsまで変動した。この変動は、即時アラートを必要とするセキュリティシステムにとって受け入れがたいものであった。

視覚的分析

時間軸上にイベントをマッピングすることで、チームは振動サンプリングルーチンがプリエンプティブでないことを特定した。このルーチンはバッファが完全に満たされるまでプロセッサを占有し、運動割り込みが即時に発火することを阻止した。図は、運動検出器の「信号受信」状態と「信号処理」状態の間に明確なギャップがあることを示していた。信号受信 状態と 信号処理 状態の間にある。

🚀 モデリングによる最適化戦略

ボトルネックが特定された後、チームはUMLタイミング図内に直接モデル化されたアーキテクチャ変更を提案した。目的は、高優先度イベントの遅延を低減し、システム全体のジッターを均一化することであった。

戦略1:割り込み駆動型取得

振動センサーをポーリングする代わりに、チームはハードウェアを設定してサンプリングレートで割り込みを発生させた。この変更により、データが利用可能になるまでメインループが待機状態を維持できるようになった。

- 前: CPUは各サイクルごとにステータスレジスタを積極的に確認する。

- 後: CPUはハードウェアが割り込みフラグを立てるまでスリープする。

タイミング図は、繰り返し発生していた”ステータス確認”イベントを削除し、センサークロックと同期した単一の”割り込みトリガー”イベントに置き換えた。

戦略2:優先度ベースのスケジューリング

モーション検出器の遅延を解消するために、チームは割り込み用の優先度キューを導入した。モーション信号は振動データの書き込み操作よりも高い優先度が割り当てられた。

- 優先度1:モーション検出(即時応答)

- 優先度2:振動データ保存(バックグラウンド)

- 優先度3:温度ログ記録(低優先度)

この変更により、モーション検出器が作動した際、振動割り込みハンドラは現在の書き込み操作を一時停止し、直ちに制御を譲ることが保証された。タイミング図は”モーション処理”ライフラインが”振動データ保存”ライフラインと重複しているが、モーションタスクが最初に完了していることを示した。

戦略3:デュアルバッファリング

送信プロセスがセンサー読み取りをブロッキングしないようにするため、デュアルバッファリングシステムが導入された。一方のバッファがセンサーによって満たされている間、もう一方のバッファは送信モジュールによって読み取られていた。

| バッファ状態 | リーダー | ライター |

|---|---|---|

| バッファAが満杯 | 送信モジュール | センサー |

| バッファB満 | センサー | 送信モジュール |

タイミング図は、並行実行を示すように更新された。センサー読み取り および データ送信 ライフライン。これにより、送信バスが占有されていた際に以前観察されていたアイドル時間が解消された。

📈 パフォーマンス向上の測定

タイミングモデルから導かれた変更を実装した後、システムは元の指標に基づいて再評価された。新しいUMLタイミング図が最適化された状態の設計図として機能した。

比較指標

- 平均遅延: 動作検出において、450μsから120μsに低下した。

- ジッター: 分散は200μsから20μsに低下した。

- CPU使用率: スリープモードにより、85%から40%に低下した。

- スループット: 並列処理により15%向上した。

CPU使用率の低下は副次的な利点であった。センサーのギャップ中にプロセッサがスリープできるようにすることで、電力消費が著しく低下した。これによりゲートウェイユニットのバッテリー寿命が延長され、遠隔配置において重要な要因となった。

タイミング図による検証

最終的なUMLタイミング図は検証文書として機能した。新しいアーキテクチャがすべてのデッドライン要件を満たしていることを証明した。以前赤い警告(デッドライン超過)を示していたすべてのイベントが、緑色の受容領域内に整合された。視覚的な確認により、ステークホルダーはシステムの信頼性に自信を持つことができた。

🛡️ タイミング解析のベストプラクティス

タイミング図の成功した実装には、規律と特定のモデリング基準への従従が求められる。以下の実践により、開発ライフサイクル全体を通じて図が正確かつ有用なまま保たれる。

1. 精度の一貫性

図で使用される時間単位が一貫していることを確認する。同じ軸上でミリ秒とマイクロ秒を混在させると誤解を招く可能性がある。モデル全体に共通する基本時間単位を定義する。

2. 明確な状態遷移

状態が既知であると仮定しない。例えば「待機, 実行、そして完了状態変化の曖昧さは、誤ったタイミング計算を引き起こす。

3. エラー処理を含める

エラー回復経路のタイミングをモデル化する。センサーが応答しなかった場合、システムはどのくらい待ってタイムアウトするか?このタイムアウト値は図に明示されるべきである。

4. 実際の状況に合わせて更新する

タイミング図は、実際のコード動作と一致している場合にのみ有効である。実装で割り込み優先度が変更された場合、図は直ちに更新されなければならない。古くなった図は誤った安心感を生む。

⚠️ 避けるべき一般的な落とし穴

経験豊富なエンジニアですら、タイミング図を使用する際に罠にはまることがある。これらの一般的なミスに気づくことで、分析の整合性を保つことができる。

- ジッターを無視する:平均遅延にのみ注目すると、最悪ケースの状況が隠れてしまう。常に最大のばらつきをモデル化するべきである。

- 過度な単純化:異なるハードウェアコンポーネントを表すライフラインを結合すると、競合問題が見えにくくなる。ハードウェア層とソフトウェア層を明確に分けること。

- 割り込み遅延を無視する:CPUがコンテキストを切り替えるのにかかる時間はしばしばゼロではない。このコストを図に含めるべきである。

- 静的モデル化:すべてのシナリオに1つの図を使用する。異なる負荷状態(例:高トラフィック vs. イドリング)には、別々のタイミングモデルが必要になる場合がある。

🔗 他のモデルとの統合

UMLタイミング図は強力であるが、他のモデリング手法と統合されたときに最も効果的である。単独で存在してはならない。

状態機械図との連携

ライフライン内の論理を定義するために状態機械図を使用する。その後、タイミング図が遷移にかかる時間を決定する。この組み合わせにより、論理フローと時間的制約の両方が明確になる。

アクティビティ図との連携

アクティビティ図は制御の流れを示す。タイミング図は時間の流れを示す。これらを併用することで、チームは与えられた時間制約内で論理フローが効率的かどうかを確認できる。

🎯 結論

センサーのデータ処理フローを最適化するには、時間的ダイナミクスに対する深い理解が必要である。標準的なデータフローモデルは、時間という重要な次元を無視しがちである。UMLタイミング図を採用することで、エンジニアリングチームは遅延、ジッター、リソース競合を明確に可視化できる。

事例研究は、ポーリングアーキテクチャから割り込み駆動型で優先度に基づくシステムに移行することで、性能が著しく向上することを示した。タイミング図は文書化のためだけではなく、最適化プロセスを導く設計ツールとしても機能した。チームはコードを書く前にもボトルネックを予測でき、実装後に解決策を検証できた。

タイミングが安全または性能上の制約となるシステムでは、このモデリング手法は不可欠である。抽象的なタイミング要件を具体的な視覚的証拠に変換し、正確なエンジニアリング意思決定を可能にする。センサネットワークがより複雑になり、リアルタイム要件が厳しくなる中で、時間を正確にモデル化する能力は、システムアーキテクトにとっての核心的スキルとして常に重要である。

提示されたベストプラクティスに従い、一般的な落とし穴を避けることで、組織はUMLタイミング図を活用して堅牢で効率的かつ信頼性の高い組み込みシステムを構築できます。正確なモデル化に投資することで、デバッグ時間の短縮、ハードウェアコストの低減、システム信頼性の向上という成果が得られます。