एम्बेडेड सिस्टम और रियल-टाइम कंप्यूटिंग के क्षेत्र में, समय सटीकता केवल एक पसंद नहीं है—यह एक आवश्यकता है। सेंसर डेटा के संबंध में, जानकारी के आने का समय अक्सर जानकारी के समान महत्वपूर्ण होता है। लेटेंसी, जिटर और प्रोसेसिंग विंडो यह तय करते हैं कि कोई सिस्टम सुरक्षित रूप से काम करे या विनाशकारी तरीके से विफल हो जाए। यह मार्गदर्शिका UML टाइमिंग डायग्राम्स का उपयोग करके सेंसर डेटा प्रोसेसिंग फ्लो को अनुकूलित करने पर एक व्यावहारिक केस स्टडी का अध्ययन करती है। हम देखेंगे कि समय संबंधों को दृश्याकृत करने से इंजीनियर बॉटलनेक्स की पहचान कर सकते हैं और ऐसे संरचनात्मक परिवर्तन कर सकते हैं जो कॉस्ट के बिना प्रदर्शन में सुधार करते हैं।

यहाँ लक्ष्य किसी नए उपकरण को लाने का नहीं है, बल्कि मॉडलिंग दृष्टिकोण को बेहतर बनाना है। डेटा फ्लो से समय फ्लो की ओर ध्यान केंद्रित करने से टीमें छिपे हुए निर्भरताओं को उजागर कर सकती हैं जो मानक सीक्वेंस डायग्राम्स अक्सर छोड़ देते हैं। यह दस्तावेज़ एक सामान्य IoT सेंसर नेटवर्क आर्किटेक्चर में समय सीमाओं के लागू करने की विधि, विश्लेषण प्रक्रिया और मापने योग्य परिणामों का वर्णन करता है।

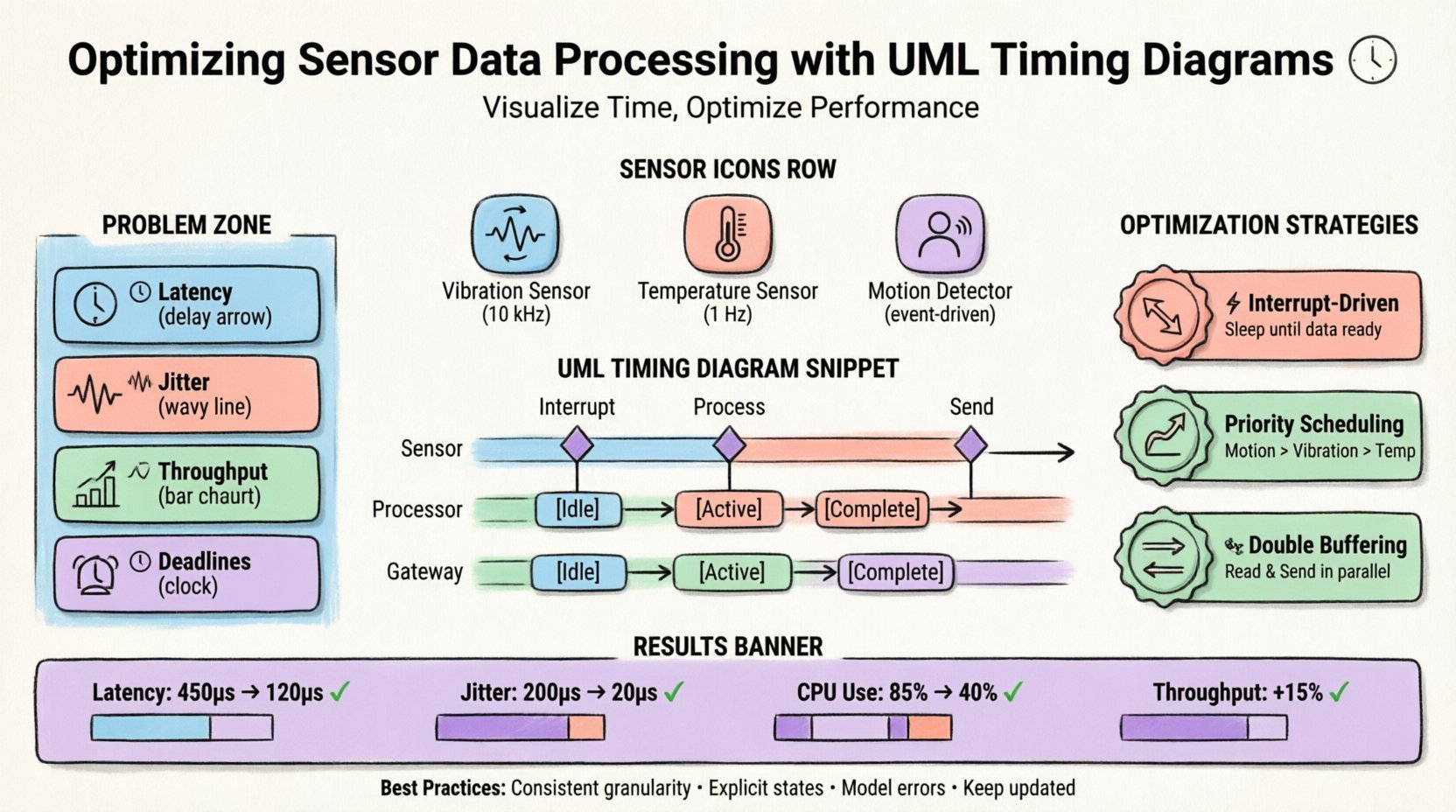

📊 एम्बेडेड सिस्टम में समय सीमाओं को समझना

एम्बेडेड सिस्टम सख्त संसाधन सीमाओं के तहत काम करते हैं। मेमोरी, प्रोसेसिंग पावर और ऊर्जा सीमित संसाधन हैं। जब कई सेंसर एक केंद्रीय प्रोसेसिंग इकाई में डेटा भेजते हैं, तो डेटा प्राप्ति का क्रम और समय जटिल हो जाता है। एक पॉलिंग तंत्र एक छोटे अवधि वाली घटना को छोड़ सकता है। एक इंटरप्ट हैंडलर एक महत्वपूर्ण कार्य को भूखा छोड़ सकता है। समय का स्पष्ट नक्शा न होने पर, इन समस्याओं को डेप्लॉयमेंट तक दिखाई नहीं देता।

मानक फ्लोचार्ट्स वर्णन करते हैं क्याहोता है। सीक्वेंस डायग्राम्स वर्णन करते हैं कौनकिससे बात करता है किससे। टाइमिंग डायग्राम्स वर्णन करते हैं जबचीजें एक दूसरे के संबंध में कब होती हैं। यह अंतर सेंसर नेटवर्क के लिए महत्वपूर्ण है जहाँ किसी सिग्नल को प्रोसेस करने का अवसर का विंडो भौतिक दुनिया द्वारा निर्धारित होता है।

महत्वपूर्ण समय संबंधी मापदंड

- लेटेंसी:सेंसर ट्रिगर से डेटा उपलब्धता तक कुल देरी।

- जिटर:बहुत सारी घटनाओं के बीच लेटेंसी में भिन्नता।

- थ्रूपुट:समय के एक इकाई में प्रोसेस की गई डेटा की मात्रा।

- मुद्रांकन:एक कार्य के पूरा होने के लिए अनुमत अधिकतम समय, जब तक डेटा अमान्य न हो जाए।

इन मापदंडों को संबोधित करने के लिए एक मॉडल की आवश्यकता होती है जो समय को स्पष्ट रूप से पकड़े। UML टाइमिंग डायग्राम इस विश्लेषण के लिए एक निर्देशांक प्रणाली प्रदान करता है, जिससे घटनाओं को क्षैतिज समय अक्ष के साथ स्थापित किया जा सकता है।

🛠️ UML टाइमिंग डायग्राम की रचना

इस मॉडलिंग तकनीक का प्रभावी रूप से उपयोग करने के लिए, इसके घटकों को समझना आवश्यक है। सीक्वेंस डायग्राम के विपरीत जो वस्तु बातचीत पर ध्यान केंद्रित करता है, टाइमिंग डायग्राम वस्तुओं की स्थिति के समय पर ध्यान केंद्रित करता है। क्षैतिज अक्ष समय का प्रतिनिधित्व करता है, बाएं से दाएं बढ़ता है। लंबवत अक्ष अलग-अलग वस्तुओं, लाइफलाइन्स या चर का प्रतिनिधित्व करता है।

मुख्य तत्व

- लाइफलाइन:किसी वस्तु या चर के एक अवधि के दौरान अस्तित्व का प्रतिनिधित्व करता है।

- राज्य घटना: किसी वस्तु के एक विशिष्ट अवस्था में होने का संकेत करता है (उदाहरण के लिए, अनक्रिय, सक्रिय, नींद में).

- स्थिति: एक समय अंतराल जिसमें एक स्थिति सत्य या असत्य होनी चाहिए।

- घटना: एक विशिष्ट समय बिंदु जहाँ कोई क्रिया होती है (उदाहरण के लिए, अंतराप्राप्त उत्पन्न).

- संकेत: जीवन रेखाओं के बीच पारित संदेश, उनके समय के साथ टिप्पणी किए गए।

सेंसर प्रक्रिया के लिए आरेख बनाते समय, जीवन रेखाएँ आमतौर पर सेंसर हार्डवेयर, इंटरपट कंट्रोलर, मुख्य प्रक्रिया धागा और संचार बस का प्रतिनिधित्व करती हैं। इन्हें सटीक समय सीमाओं के साथ जोड़ने से पता चलता है कि डेटा कहाँ प्रतीक्षा कर रहा है और कहाँ प्रक्रिया शक्ति बर्बाद हो रही है।

📡 सेंसर नेटवर्क परिदृश्य

एक औद्योगिक वातावरण में लगाए गए निगरानी प्रणाली को ध्यान में रखें। इस प्रणाली तीन अलग-अलग स्रोतों से डेटा संग्रहित करती है:

- कंपन सेंसर: मशीन के स्वास्थ्य के लिए उच्च आवृत्ति नमूनाकरण (10 किलोहर्ट्ज़)।

- तापमान सेंसर: सुरक्षा सीमाओं के लिए निम्न आवृत्ति नमूनाकरण (1 हर्ट्ज़)।

- गति डिटेक्टर: सुरक्षा चेतावनियों के लिए घटना-आधारित ट्रिगर।

इन सेंसर को एक माइक्रोकंट्रोलर से जोड़ा जाता है जिसे डेटा संग्रहित करना और इसे क्लाउड गेटवे तक स्थानांतरित करना होता है। प्रारंभिक डिज़ाइन में सभी सेंसर को क्रमिक रूप से जांचने के लिए एक ही पॉलिंग लूप का उपयोग किया गया था। हालांकि इसे लागू करना आसान था, लेकिन इस दृष्टिकोण ने लैटेंसी में महत्वपूर्ण भिन्नता लाई।

प्रणाली संरचना समीक्षा

| घटक | भूमिका | समय सीमा |

|---|---|---|

| कंपन सेंसर | उच्च गति अधिग्रहण | अधिकतम 100μs लेटेंसी |

| तापमान सेंसर | आवधिक निगरानी | अधिकतम 100ms लेटेंसी |

| गति डिटेक्टर | घटना निर्धारण | अधिकतम 500μs लेटेंसी |

| बादल गेटवे | डेटा संचरण | अधिकतम 2 सेकंड लेटेंसी |

चुनौती साझा बस में थी। जब कंपन सेंसर उच्च गति पहुँच के लिए अनुरोध करता था, तो तापमान और गति सेंसर को देरी का सामना करना पड़ता था। प्रारंभिक मॉडल ने बस प्रतिस्पर्धा या इंटरपट प्राथमिकता को ध्यान में नहीं रखा, जिसके कारण महत्वपूर्ण परिस्थितियों में डेडलाइन छूट गई।

🔍 लेटेंसी और जिटर समस्याओं की पहचान करना

अनुकूलन का पहला चरण अस्तित्व में मौजूद पॉलिंग कोड पर आधारित एक आधारभूत UML समय आरेख बनाना था। इस दृश्य प्रस्तुतीकरण ने कई महत्वपूर्ण अक्षमताओं को उजागर किया।

निरीक्षित बफ़लेट

- पॉलिंग ओवरहेड: मुख्य लूप प्रति सेकंड 10,000 बार कंपन सेंसर की जांच करता था, भले ही कोई नया डेटा तैयार न हो। इसने CPU साइकिल्स का उपयोग किया जो अन्य कार्यों के लिए उपयोग किए जा सकते थे।

- इंटरपट ब्लॉकिंग: गति डिटेक्टर इंटरपट पर निर्भर था, लेकिन कंपन सेंसर लंबे समय तक बस को धारण करता था, जिससे गति संकेत में देरी हुई।

- डेटा बफरिंग: मध्यवर्ती डेटा एकल बफर में संग्रहीत किया जाता था, जिससे गेटवे को संचरण के समय सेंसर पढ़ने के साथ-साथ एक बफलेट बन गया।

समय आरेख ने जिटर को स्पष्ट कर दिया। गति ट्रिगर और वास्तविक प्रसंस्करण के बीच का समय कंपन नमूनाकरण चरण के आधार पर 200μs से 400μs तक बदलता था। ऐसी भिन्नता सुरक्षा प्रणाली के लिए अस्वीकार्य थी जिसे तुरंत चेतावनी की आवश्यकता होती है।

दृश्य विश्लेषण

समय अक्ष पर घटनाओं के मैपिंग के बाद, टीम ने पाया कि कंपन नमूनाकरण रूटीन अप्रतिस्पर्धी थी। यह प्रोसेसर को पूरे बफर को भरने तक धारण करती रही, जिससे गति इंटरपट के तुरंत फायर होने से रोका गया। आरेख ने गति डिटेक्टर के “संकेत प्राप्त” और “संकेत प्रसंस्कृत” अवस्थाओं के बीच स्पष्ट अंतर दिखाया।संकेत प्राप्त अवस्था और संकेत प्रसंस्कृत अवस्था के लिए गति डिटेक्टर।

🚀 मॉडलिंग के माध्यम से अनुकूलन रणनीतियाँ

बफलेट की पहचान करने के बाद, टीम ने UML समय आरेख के भीतर सीधे मॉडलिंग के माध्यम से संरचनात्मक परिवर्तन प्रस्तावित किए। उद्देश्य उच्च प्राथमिकता वाली घटनाओं के लिए लेटेंसी को कम करना और पूरी प्रणाली में जिटर को चिकना करना था।

रणनीति 1: इंटरप्ट-आधारित अधिग्रहण

कंपन सेंसर की जांच करने के बजाय, टीम ने हार्डवेयर को नमूना लेने की दर पर इंटरप्ट उत्पन्न करने के लिए कॉन्फ़िगर किया। इस परिवर्तन ने मुख्य लूप को डेटा उपलब्ध होने तक अक्रिय रहने की अनुमति दी।

- पहले:CPU हर साइकल में स्थिति रजिस्टर की जांच करता है।

- बाद में:CPU हार्डवेयर द्वारा इंटरप्ट फ्लैग उठाने तक सोता रहता है।

समय आरेख ने इसे दोहराए गए स्थिति जांचें इवेंट को हटाकर उनके स्थान पर एकल इंटरप्ट ट्रिगर इवेंट सेंसर क्लॉक के साथ समायोजित किया गया।

रणनीति 2: प्राथमिकता-आधारित योजना बनाना

गति डिटेक्टर के लेटेंसी को दूर करने के लिए, टीम ने इंटरप्ट्स के लिए प्राथमिकता वाला कतार लागू किया। गति संकेत को कंपन डेटा लेखन कार्य से अधिक प्राथमिकता दी गई।

- प्राथमिकता 1:गति का पता लगाना (तुरंत प्रतिक्रिया)

- प्राथमिकता 2:कंपन डेटा संग्रहण (पृष्ठभूमि)

- प्राथमिकता 3:तापमान लॉगिंग (कम प्राथमिकता)

इस परिवर्तन ने यह सुनिश्चित किया कि जब गति डिटेक्टर चालू होता है, तो कंपन इंटरप्ट हैंडलर अपने वर्तमान लेखन कार्य को रोक देता है और तुरंत नियंत्रण सौंप देता है। समय आरेख ने दिखाया कि गति प्रक्रिया करें लाइफलाइन कंपन संग्रहण के लाइफलाइन के ऊपर आती है, लेकिन गति कार्य पहले पूरा होता है।कंपन संग्रहण करेंलाइफलाइन, लेकिन गति कार्य पहले पूरा होता है।

रणनीति 3: डबल बफरिंग

संचार प्रक्रिया द्वारा सेंसर पठन को रोकने से बचने के लिए डबल बफरिंग प्रणाली लागू की गई। जब एक बफर सेंसर द्वारा भरा जा रहा था, तब दूसरा बफर संचार मॉड्यूल द्वारा पढ़ा जा रहा था।

| बफर स्थिति | पाठक | लेखक |

|---|---|---|

| बफर A पूरा हुआ | संचरण मॉड्यूल | सेंसर |

| बफर बी भरा हुआ | सेंसर | संचरण मॉड्यूल |

समय आरेख में समानांतर कार्यान्वयन को दिखाने के लिए अद्यतन किया गया हैसेंसर पढ़ें और डेटा भेजें लाइफलाइन्स। इसने पहले देखी गई अव्यवस्थित समय को समाप्त कर दिया जब संचरण बस व्यस्त थी।

📈 प्रदर्शन में सुधार का मापन

समय मॉडल से निकाले गए परिवर्तनों को लागू करने के बाद, प्रणाली का मूल मापदंडों के अनुसार पुनर्मूल्यांकन किया गया। नए UML समय आरेख ने अनुकूलित अवस्था के लिए नक्शा तैयार किया।

तुलनात्मक मापदंड

- औसत लेटेंसी: गति के पता लगाने के लिए 450μs से घटाकर 120μs कर दी गई।

- जिटर: विचरण 200μs से घटाकर 20μs कर दिया गया।

- CPU उपयोगिता: स्लीप मोड के कारण 85% से घटाकर 40% कर दी गई।

- थ्रूपुट: समानांतर प्रसंस्करण के कारण 15% बढ़ा दिया गया।

CPU उपयोगिता में कमी एक द्वितीयक लाभ था। सेंसर के अंतराल के दौरान प्रोसेसर को सोने देने से ऊर्जा खपत में काफी कमी आई। इससे गेटवे इकाई के बैटरी जीवन को बढ़ाया गया, जो दूरस्थ निर्माण के लिए एक महत्वपूर्ण कारक था।

समय आरेख द्वारा प्रमाणीकरण

अंतिम UML समय आरेख एक प्रमाणन दस्तावेज के रूप में कार्य किया। इसने सिद्ध किया कि नई वास्तुकला सभी समय सीमा आवश्यकताओं को पूरा करती है। पहले लाल चेतावनी (समय सीमा का उल्लंघन) दिखाने वाला प्रत्येक घटना अब हरे स्वीकृति क्षेत्र के भीतर संरेखित हो गया। दृश्य पुष्टि ने रुचि रखने वाले पक्षों को प्रणाली की विश्वसनीयता में विश्वास दिलाया।

🛡️ समय विश्लेषण के लिए सर्वोत्तम प्रथाएं

समय आरेखों के सफल कार्यान्वयन के लिए अनुशासन और विशिष्ट मॉडलिंग मानकों का पालन करना आवश्यक है। निम्नलिखित प्रथाएं सुनिश्चित करती हैं कि आरेख विकास चक्र के दौरान सटीक और उपयोगी बने रहें।

1. विस्तार स्थिरता

सुनिश्चित करें कि आरेख में उपयोग की जाने वाली समय इकाइयाँ स्थिर हों। एक ही अक्ष पर मिलीसेकंड और माइक्रोसेकंड का मिश्रण गलत व्याख्या के कारण हो सकता है। पूरे मॉडल के लिए एक आधार समय इकाई निर्धारित करें।

2. स्पष्ट अवस्था संक्रमण

अवस्थाओं को ज्ञात मानने का प्रयास न करें। स्पष्ट रूप से संक्रमण चिह्नित करें जैसे कि “प्रतीक्षा करें, निष्पादित करें, और पूरा करें. अवस्था परिवर्तनों में अस्पष्टता सही समय गणना के लिए गलत निष्कर्ष निकालती है।

3. त्रुटि संभाल को शामिल करें

त्रुटि पुनर्स्थापना मार्गों के समय को मॉडल करें। यदि कोई सेंसर प्रतिक्रिया नहीं देता है, तो प्रणाली कितनी देर तक प्रतीक्षा करती है जब तक कि समय समाप्त नहीं हो जाता है? इस समय समाप्ति मान को आरेख में दिखाया जाना चाहिए।

4. वास्तविकता के अनुसार अद्यतन करें

एक समय आरेख केवल तभी मान्य है जब वह वास्तविक कोड व्यवहार के साथ मेल खाता हो। यदि कार्यान्वयन इंटरप्ट प्राथमिकता को बदलता है, तो आरेख को तुरंत अद्यतन किया जाना चाहिए। अद्यतन न किए गए आरेख गलत आत्मविश्वास पैदा करते हैं।

⚠️ बचने के लिए सामान्य त्रुटियाँ

यहाँ तक कि अनुभवी � ingineers भी समय आरेखों के उपयोग में जाल में फंस सकते हैं। इन सामान्य गलतियों के बारे में जागरूकता विश्लेषण की अखंडता को बनाए रखने में मदद करती है।

- झिंझकारी को नजरअंदाज करना:केवल औसत देरी पर ध्यान केंद्रित करना दुर्भाग्यपूर्ण परिस्थितियों को छिपा सकता है। हमेशा अधिकतम विचलन को मॉडल करें।

- अत्यधिक सरलीकरण:विभिन्न हार्डवेयर घटकों का प्रतिनिधित्व करने वाले जीवन रेखाओं को मिलाना संवाद की समस्याओं को छिपा सकता है। हार्डवेयर और सॉफ्टवेयर परतों को अलग रखें।

- इंटरप्ट देरी को नजरअंदाज करना:सीपीयू के संदर्भ बदलने में लगने वाला समय अक्सर शून्य नहीं होता है। इस लागत को आरेख में शामिल करें।

- स्थिर मॉडलिंग: सभी परिदृश्यों के लिए एक ही आरेख का उपयोग करना। विभिन्न लोड स्थितियाँ (उदाहरण के लिए, उच्च ट्रैफिक बनाम अनावश्यक) के लिए अलग-अलग समय मॉडल की आवश्यकता हो सकती है।

🔗 अन्य मॉडलों के साथ एकीकरण

जबकि यूएमएल समय आरेख शक्तिशाली है, यह अन्य मॉडलिंग तकनीकों के साथ एकीकृत होने पर सबसे प्रभावी होता है। इसे अकेले नहीं रखना चाहिए।

राज्य मशीन आरेखों के साथ अंतरक्रिया

लाइफलाइन के भीतर तर्क को परिभाषित करने के लिए राज्य मशीन आरेखों का उपयोग करें। फिर समय आरेख यह निर्धारित करता है कि संक्रमण कितना समय लेते हैं। इस संयोजन से तार्किक प्रवाह और समय सीमाओं दोनों की स्पष्टता होती है।

गतिविधि आरेखों के साथ अंतरक्रिया

गतिविधि आरेख नियंत्रण के प्रवाह को दिखाते हैं। समय आरेख समय के प्रवाह को दिखाते हैं। उनके साथ उपयोग करने से टीमों को यह देखने में मदद मिलती है कि तार्किक प्रवाह दिए गए समय सीमाओं के भीतर कुशल है या नहीं।

🎯 निष्कर्ष

सेंसर डेटा प्रसंस्करण प्रवाह को अनुकूलित करने के लिए समयगत गतिशीलता की गहन समझ की आवश्यकता होती है। मानक डेटा प्रवाह मॉडल अक्सर समय के महत्वपूर्ण आयाम को नजरअंदाज कर देते हैं। यूएमएल समय आरेखों को अपनाकर इंजीनियरिंग टीमें लेटेंसी, झिंझकारी और संसाधन प्रतिस्पर्धा को स्पष्ट रूप से देख सकती हैं।

केस स्टडी ने दिखाया कि पॉलिंग आर्किटेक्चर से इंटरप्ट-आधारित, प्राथमिकता-आधारित प्रणाली में स्थानांतरण से प्रदर्शन में महत्वपूर्ण सुधार हुआ। समय आरेख केवल दस्तावेज़ीकरण के रूप में नहीं, बल्कि अनुकूलन प्रक्रिया को निर्देशित करने वाले डिज़ाइन उपकरण के रूप में कार्य किया। इसने टीम को कोड लिखे जाने से पहले बॉटलनेक्स की भविष्यवाणी करने और कार्यान्वयन के बाद समाधानों की पुष्टि करने की अनुमति दी।

ऐसी प्रणालियों के लिए जहाँ समय सुरक्षा या प्रदर्शन की सीमा है, इस मॉडलिंग दृष्टिकोण अनिवार्य है। यह स्थिर समय आवश्यकताओं को वास्तविक दृश्य साक्ष्य में बदल देता है, जिससे सटीक इंजीनियरिंग निर्णय लेने में सक्षम होते हैं। जैसे-जैसे सेंसर नेटवर्क अधिक जटिल होते हैं और वास्तविक समय की आवश्यकताएँ अधिक कठोर होती हैं, समय को सटीक रूप से मॉडल करने की क्षमता सिस्टम वार्डों के लिए एक मूल क्षमता बनी रहेगी।

उल्लिखित सर्वोत्तम प्रथाओं का पालन करने और सामान्य त्रुटियों से बचने से संगठन UML समय आरेखों का उपयोग करके विश्वसनीय, कुशल और टिकाऊ एम्बेडेड प्रणालियाँ बनाने में सक्षम हो सकते हैं। सटीक मॉडलिंग में निवेश का लाभ डिबगिंग समय कम करने, कम हार्डवेयर लागत और अधिक प्रणाली विश्वसनीयता में देखा जा सकता है।