Dans le domaine des systèmes embarqués et du calcul en temps réel, la précision temporelle n’est pas simplement un souhait — c’est une exigence. Lorsqu’on traite des données de capteurs, l’instant auquel les informations arrivent est souvent aussi critique que les informations elles-mêmes. La latence, le jitter et les fenêtres de traitement déterminent si un système fonctionne en toute sécurité ou échoue de manière catastrophique. Ce guide explore une étude de cas pratique axée sur l’optimisation des flux de traitement des données des capteurs à l’aide des diagrammes de timing UML. Nous examinerons comment la visualisation des relations temporelles permet aux ingénieurs d’identifier les goulets d’étranglement et d’implémenter des changements structurels qui améliorent les performances sans engager de coûts matériels.

L’objectif ici n’est pas d’introduire un nouvel outil, mais de perfectionner l’approche de modélisation. En déplaçant l’attention du flux de données vers le flux temporel, les équipes peuvent découvrir des dépendances cachées que les diagrammes de séquence standards négligent souvent. Ce document détaille la méthodologie, le processus d’analyse et les résultats mesurables de l’application de contraintes temporelles à une architecture typique de réseau de capteurs IoT.

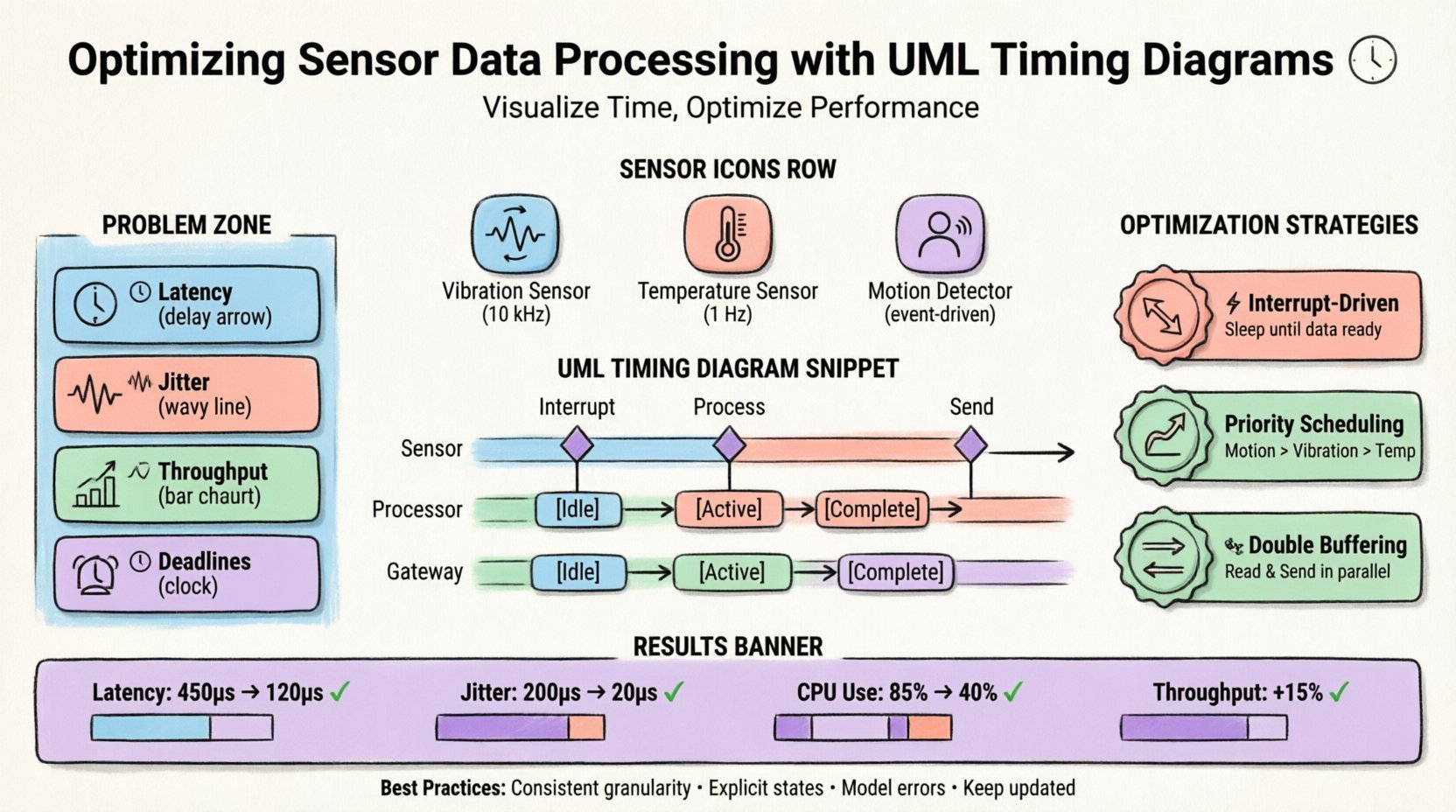

📊 Comprendre les contraintes temporelles dans les systèmes embarqués

Les systèmes embarqués fonctionnent sous des contraintes strictes de ressources. La mémoire, la puissance de traitement et l’énergie sont des ressources finies. Lorsque plusieurs capteurs alimentent une unité de traitement centrale, l’ordre et le moment de l’acquisition des données deviennent complexes. Un mécanisme d’interrogation peut manquer un événement à courte durée. Un gestionnaire d’interruption peut privilégier une tâche au détriment d’une tâche critique. Sans une carte claire du temps, ces problèmes restent invisibles jusqu’au déploiement.

Les diagrammes de flux standards décrivent ce quise produit. Les diagrammes de séquence décrivent quiparle à qui. Les diagrammes de timing décrivent quandles choses se produisent les unes par rapport aux autres. Cette distinction est essentielle pour les réseaux de capteurs où la fenêtre d’opportunité pour traiter un signal est définie par le monde physique.

Indicateurs temporels clés

- Latence : Le délai total depuis le déclenchement du capteur jusqu’à la disponibilité des données.

- Jitter : La variance de la latence sur plusieurs événements.

- Débit : Le volume de données traitées par unité de temps.

- Délais : Le temps maximum autorisé pour qu’une tâche soit terminée avant que les données ne deviennent invalides.

Aborder ces indicateurs nécessite un modèle qui capture le temps de manière explicite. Le diagramme de timing UML fournit un système de coordonnées pour cette analyse, permettant de placer les événements le long d’un axe temporel horizontal.

🛠️ Anatomie du diagramme de timing UML

Pour utiliser efficacement cette technique de modélisation, il faut comprendre ses composants. Contrairement au diagramme de séquence, qui se concentre sur les interactions entre objets, le diagramme de timing se concentre sur l’état des objets au fil du temps. L’axe horizontal représente le temps, qui progresse de gauche à droite. L’axe vertical représente des objets distincts, des lignes de vie ou des variables.

Éléments fondamentaux

- Ligne de vie : Représente l’existence d’un objet ou d’une variable sur une durée.

- Occurrence d’état : Indique quand un objet est dans un état spécifique (par exemple, Inactif, Actif, Endormi).

- Condition : Un intervalle de temps pendant lequel une condition doit être vraie ou fausse.

- Événement : Un moment précis dans le temps où une action se produit (par exemple, Interruption déclenchée).

- Signal : Messages échangés entre les lignes de vie, annotés avec leur chronologie.

Lors de la construction d’un diagramme pour le traitement des capteurs, les lignes de vie représentent généralement le matériel du capteur, le contrôleur d’interruption, le thread principal de traitement et le bus de communication. Les relier avec des contraintes de timing précises révèle où les données attendent et où la puissance de traitement est gaspillée.

📡 Le scénario du réseau de capteurs

Considérons un système de surveillance déployé dans un environnement industriel. Ce système agrège des données provenant de trois sources distinctes :

- Capteur de vibration : Échantillonnage à haute fréquence (10 kHz) pour l’état de santé des machines.

- Capteur de température : Échantillonnage à basse fréquence (1 Hz) pour les seuils de sécurité.

- Détection de mouvement : Déclenchement déclenché par événement pour les alertes de sécurité.

Ces capteurs sont connectés à un microcontrôleur qui doit agrégé les données et les transmettre à une passerelle cloud. La conception initiale utilisait une boucle de sondage unique pour vérifier tous les capteurs séquentiellement. Bien que simple à implémenter, cette approche a introduit une variation importante dans la latence.

Aperçu de l’architecture du système

| Composant | Rôle | Exigence de temporisation |

|---|---|---|

| Capteur de vibration | Acquisition à haute vitesse | Latence maximale de 100 μs |

| Capteur de température | Surveillance périodique | Latence maximale de 100 ms |

| Détection de mouvement | Détection d’événements | Latence maximale de 500 μs |

| Passerelle cloud | Transmission de données | Latence maximale de 2 s |

Le défi réside dans le bus partagé. Lorsque le capteur de vibration demandait un accès à haute vitesse, les capteurs de température et de mouvement subissaient des délais. Le modèle initial ne tenait pas compte de la contention du bus ni de la priorité des interruptions, ce qui entraînait des échéances manquées dans des scénarios critiques.

🔍 Identification des problèmes de latence et de jitter

La première étape de l’optimisation a consisté à créer un diagramme de timing UML de base basé sur le code d’interrogation existant. Cette représentation visuelle a mis en évidence plusieurs inefficiences critiques.

Bouchons observés

- Surcharge d’interrogation : La boucle principale interrogeait le capteur de vibration 10 000 fois par seconde, même lorsque aucune nouvelle donnée n’était disponible. Cela consommait des cycles du processeur qui auraient pu être utilisés pour d’autres tâches.

- Blocage des interruptions : Le détecteur de mouvement reposait sur les interruptions, mais le capteur de vibration détenait le bus pendant de longues périodes, retardant le signal de mouvement.

- Mise en mémoire tampon des données : Les données intermédiaires étaient stockées dans un seul tampon, ce qui créait un bouchon lorsque la transmission vers la passerelle se produisait simultanément avec la lecture du capteur.

Le diagramme de timing a rendu le jitter visible. Le temps entre le déclenchement du mouvement et le traitement réel variait de 200 μs à 400 μs selon la phase d’échantillonnage de la vibration. Cette variation était inacceptable pour un système de sécurité nécessitant des alertes immédiates.

Analyse visuelle

En cartographiant les événements sur l’axe du temps, l’équipe a identifié que la routine d’échantillonnage de la vibration était non préemptive. Elle retenait le processeur jusqu’à ce que le tampon entier soit rempli, empêchant ainsi l’interruption de mouvement de se déclencher immédiatement. Le diagramme montrait un écart clair entre l’état Signal reçu et l’état Signal traité pour le détecteur de mouvement.

🚀 Stratégies d’optimisation par modélisation

Une fois les bouchons identifiés, l’équipe a proposé des changements architecturaux modélisés directement dans le diagramme de timing UML. L’objectif était de réduire la latence pour les événements à haute priorité et de lisser le jitter à travers le système.

Stratégie 1 : Acquisition pilotée par interruption

Au lieu de sonder le capteur de vibration, l’équipe a configuré le matériel pour générer des interruptions à la fréquence d’échantillonnage. Ce changement a permis à la boucle principale de rester inactive jusqu’à ce que les données soient disponibles.

- Avant :Le CPU vérifie activement le registre d’état à chaque cycle.

- Après :Le CPU dort jusqu’à ce que le matériel active le drapeau d’interruption.

Le diagramme de temporisation reflète cela en supprimant les événements répétés Vérifier l’état et en les remplaçant par un seul événement Déclenchement d’interruption aligné avec l’horloge du capteur.

Stratégie 2 : Planification basée sur la priorité

Pour résoudre le délai du détecteur de mouvement, l’équipe a mis en place une file d’attente de priorité pour les interruptions. Le signal de mouvement a été attribué une priorité supérieure à l’opération d’écriture des données de vibration.

- Priorité 1 :Détection de mouvement (réponse immédiate)

- Priorité 2 :Stockage des données de vibration (en arrière-plan)

- Priorité 3 :Journalisation de la température (basse priorité)

Cette modification a assuré que lorsque le détecteur de mouvement se déclenchait, le gestionnaire d’interruption de vibration mettait temporairement en pause son opération d’écriture en cours et cédait immédiatement le contrôle. Le diagramme de temporisation a montré la ligne de vie Traiter le mouvement chevauchant la ligne de vie Stocker la vibration mais la tâche de mouvement s’est terminée en premier.

Stratégie 3 : Double tamponnage

Pour éviter que le processus de transmission ne bloque la lecture du capteur, un système de double tamponnage a été introduit. Pendant qu’un tampon était rempli par les capteurs, l’autre était lu par le module de transmission.

| État du tampon | Lecteur | Écrivain |

|---|---|---|

| Tampon A plein | Module de transmission | Capteurs |

| Tampon B plein | Capteurs | Module de transmission |

Le diagramme de timing mis à jour pour montrer l’exécution parallèle des Lire le capteur et Envoyer les données lignes de vie. Cela a éliminé le temps d’inactivité observé précédemment lorsque le bus de transmission était occupé.

📈 Mesure des améliorations des performances

Après avoir mis en œuvre les modifications issues du modèle de timing, le système a été réévalué par rapport aux métriques initiales. Le nouveau diagramme de timing UML a servi de plan directeur pour l’état optimisé.

Métriques comparatives

- Latence moyenne : Réduite de 450μs à 120μs pour la détection de mouvement.

- Jitter : Variance passée de 200μs à 20μs.

- Utilisation du CPU : Diminuée de 85 % à 40 % grâce aux modes veille.

- Débit : Augmenté de 15 % grâce au traitement parallèle.

La réduction de l’utilisation du CPU a été un bénéfice secondaire. En permettant au processeur de dormir pendant les intervalles des capteurs, la consommation d’énergie a considérablement diminué. Cela a prolongé la durée de vie de la batterie de l’unité passagère, un facteur critique pour le déploiement à distance.

Validation via le diagramme de timing

Le diagramme de timing UML final a agi comme document de validation. Il a prouvé que la nouvelle architecture respectait toutes les exigences de délais. Chaque événement qui affichait auparavant un avertissement rouge (délai manqué) était désormais aligné dans la zone verte d’acceptation. La confirmation visuelle a donné aux parties prenantes une confiance en la fiabilité du système.

🛡️ Meilleures pratiques pour l’analyse de timing

La mise en œuvre réussie des diagrammes de timing exige de la discipline et le respect de normes spécifiques de modélisation. Les pratiques suivantes garantissent que les diagrammes restent précis et utiles tout au long du cycle de développement.

1. Cohérence de la granularité

Assurez-vous que les unités de temps utilisées dans le diagramme sont cohérentes. Mélanger millisecondes et microsecondes sur le même axe peut entraîner une mauvaise interprétation. Définissez une unité de temps de base pour l’ensemble du modèle.

2. Transitions d’état explicites

Ne supposez pas que les états sont connus. Marquez explicitement les transitions telles que “Attendez, Exécuter, et Terminer. L’ambiguïté dans les changements d’état entraîne des calculs de temporisation incorrects.

3. Inclure la gestion des erreurs

Modélisez le temporisation des chemins de récupération d’erreurs. Si un capteur ne répond pas, combien de temps le système attend-il avant d’expirer ? Cette valeur d’expiration doit être visible sur le diagramme.

4. Mettre à jour avec la réalité

Un diagramme de temporisation n’est valable que s’il correspond au comportement réel du code. Si l’implémentation modifie la priorité des interruptions, le diagramme doit être mis à jour immédiatement. Les diagrammes obsolètes créent une fausse confiance.

⚠️ Pièges courants à éviter

Même les ingénieurs expérimentés peuvent tomber dans des pièges lors de l’utilisation des diagrammes de temporisation. La prise de conscience de ces erreurs courantes aide à préserver l’intégrité de l’analyse.

- Ignorer les variations de jitter : Se concentrer uniquement sur la latence moyenne peut masquer les scénarios les plus défavorables. Modélisez toujours la variance maximale.

- Sur-simplification : Combiner des lignes de vie représentant des composants matériels différents peut masquer les problèmes de contention. Gardez les couches matérielles et logicielles distinctes.

- Ne pas tenir compte de la latence des interruptions : Le temps nécessaire au CPU pour basculer de contexte est souvent non nul. Incluez ce coût dans le diagramme.

- Modélisation statique : Utiliser un seul diagramme pour toutes les scénarios. Des conditions de charge différentes (par exemple, fort trafic contre inactivité) peuvent nécessiter des modèles de temporisation distincts.

🔗 Intégration avec d’autres modèles

Bien que le diagramme de temporisation UML soit puissant, il est le plus efficace lorsqu’il est intégré à d’autres techniques de modélisation. Il ne doit pas exister en isolation.

Interaction avec les diagrammes d’états

Utilisez les diagrammes d’états pour définir la logique au sein d’une ligne de vie. Le diagramme de temporisation indique alors la durée des transitions. Cette combinaison clarifie à la fois le flux logique et les contraintes temporelles.

Interaction avec les diagrammes d’activité

Les diagrammes d’activité montrent le flux de contrôle. Les diagrammes de temporisation montrent le flux du temps. Leur utilisation conjointe permet aux équipes de vérifier si le flux logique est efficace dans les contraintes de temps données.

🎯 Conclusion

Optimiser les flux de traitement des données des capteurs exige une compréhension approfondie des dynamiques temporelles. Les modèles standards de flux de données négligent souvent la dimension critique du temps. En adoptant les diagrammes de temporisation UML, les équipes d’ingénierie peuvent visualiser explicitement la latence, le jitter et la contention des ressources.

L’étude de cas a démontré que passer d’une architecture d’interrogation à un système piloté par interruption et basé sur la priorité améliorait considérablement les performances. Le diagramme de temporisation n’a pas seulement servi de documentation, mais aussi d’outil de conception qui a guidé le processus d’optimisation. Il a permis à l’équipe de prévoir les goulets d’étranglement avant l’écriture du code et de vérifier les solutions après mise en œuvre.

Pour les systèmes où le temps est une contrainte de sécurité ou de performance, cette approche de modélisation est indispensable. Elle transforme les exigences de temporisation abstraites en preuves visuelles concrètes, permettant des décisions d’ingénierie précises. À mesure que les réseaux de capteurs deviennent plus complexes et que les exigences en temps réel s’accentuent, la capacité à modéliser le temps avec précision restera une compétence fondamentale pour les architectes de systèmes.

En suivant les meilleures pratiques décrites et en évitant les pièges courants, les organisations peuvent tirer parti des diagrammes de timing UML pour concevoir des systèmes embarqués robustes, efficaces et fiables. L’investissement dans une modélisation précise porte ses fruits sous forme de temps de débogage réduit, de coûts matériels inférieurs et d’une fiabilité système accrue.