Le temps est le fil invisible qui relie matériel et logiciel. Dans les systèmes embarqués, les microcontrôleurs et les dispositifs IoT, chaque milliseconde compte. Un retard de quelques microsecondes peut entraîner une panne système, une perte de données ou un risque de sécurité. Pour visualiser ces relations temporelles, les ingénieurs se tournent versles diagrammes de temporisation UML. Ces diagrammes offrent une méthode rigoureuse pour modéliser le comportement des signaux au fil du temps, garantissant que les composants matériels et la logique logicielle fonctionnent en synchronisation.

La modélisation des interfaces matériel-logiciel exige une précision. Contrairement aux diagrammes d’interaction standards, les diagrammes de temporisation se concentrent sur l’instant exact où les signaux changent d’état. Ce guide explore comment construire, interpréter et appliquer ces diagrammes dans des scénarios d’ingénierie réels. Nous examinerons les transitions de signal, les régions actives et les contraintes de temporisation sans dépendre d’outils spécifiques.

⚙️ Comprendre le but fondamental

Un diagramme de temporisation UML est un diagramme comportemental qui met l’accent sur les contraintes de temporisation des objets et des signaux. Il est particulièrement utile lorsque la correction d’un système dépend du moment des événements, et non seulement de la séquence des messages.

- Précision temporelle : Il définit à quel moment un signal doit monter ou descendre.

- Surveillance d’état : Il suit l’état d’un objet sur un intervalle de temps spécifique.

- Vérification d’interface : Il vérifie si le matériel répond aux attentes du logiciel.

Lors de la conception d’un contrôleur embarqué, le logiciel envoie une commande, et le matériel doit répondre dans une fenêtre spécifique. Si le matériel met trop de temps, le logiciel peut expirer. Si la réponse arrive trop tôt, les données pourraient être illisibles. Les diagrammes de temporisation capturent cette danse.

📉 Composants clés d’un diagramme de temporisation

Pour construire un diagramme valide, vous devez comprendre la syntaxe. La notation est standardisée, garantissant que tout ingénieur peut lire le modèle.

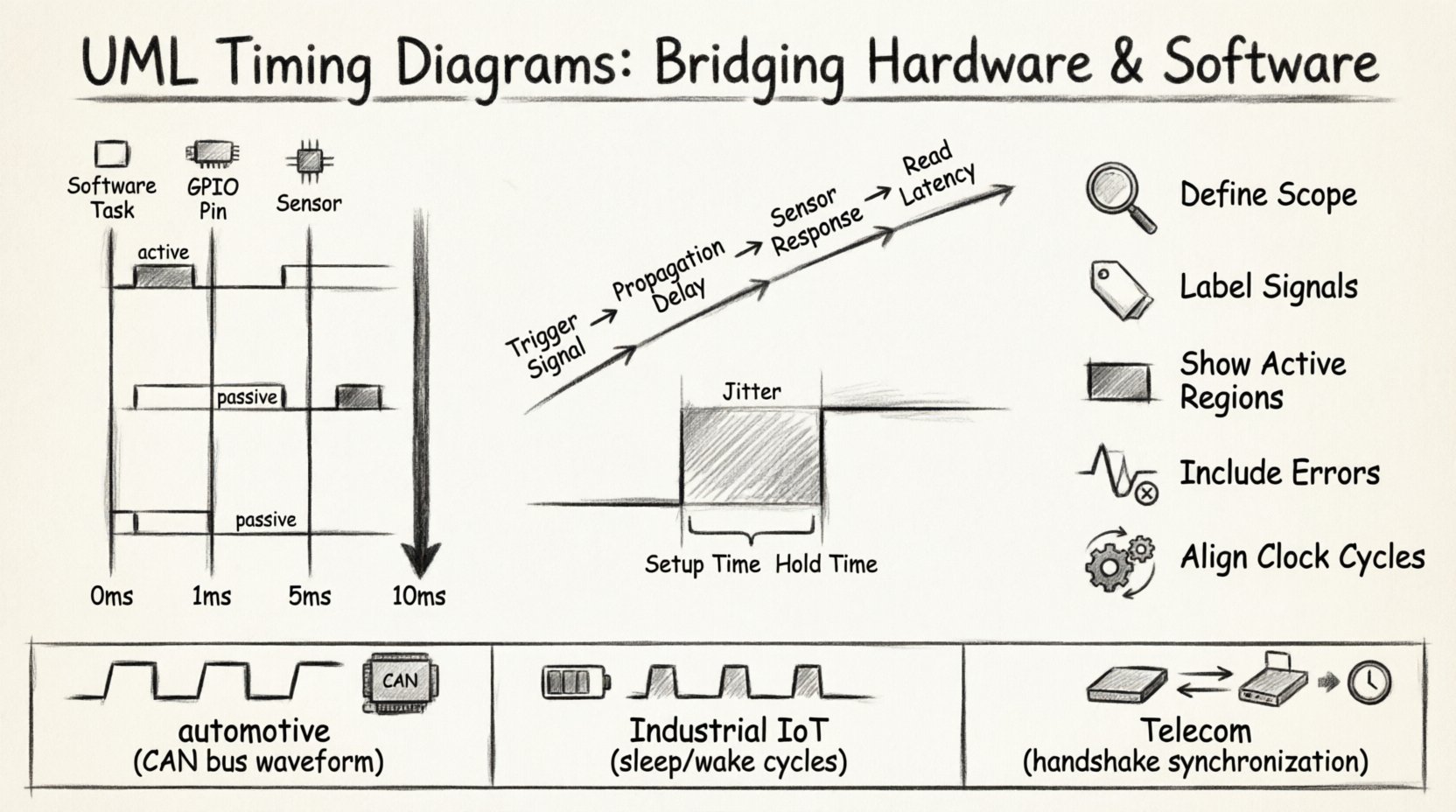

1. Lignes de vie

Une ligne de vie représente un objet ou une interface. Dans les contextes matériel-logiciel, les lignes de vie correspondent souvent à :

- Tâches logicielles : La boucle principale, les gestionnaires d’interruption ou les pilotes.

- Signaux matériels : Broches GPIO, lignes de bus (SPI, I2C) ou lignes d’interruption.

- Périphériques externes : Capteurs, actionneurs ou modules de communication.

Chaque ligne de vie est une ligne verticale s’étendant vers le bas du diagramme. Le temps s’écoule du haut vers le bas.

2. L’axe du temps

Contrairement aux diagrammes de séquence, où l’accent est mis sur l’ordre des messages, les diagrammes de temporisation disposent d’un axe du temps explicite. Celui-ci peut être du temps absolu (par exemple, millisecondes) ou du temps relatif (par exemple, cycles d’horloge).

- Temps absolu : Utile pour les exigences au niveau du système, comme « la réponse doit avoir lieu dans un délai de 50 ms ».

- Temps relatif : Utile pour la logique interne, par exemple « attendre 3 cycles d’horloge après le démarrage ».

3. États et valeurs des signaux

Les signaux passent d’un état défini à un autre. En logique numérique, ces états sont généralement 0 et 1. Dans le diagramme, ils sont représentés par des barres horizontales sur la ligne de vie.

- État actif : Une barre remplie indiquant que le signal est à haut niveau ou activé.

- État passif : Un espace vide ou une ligne pointillée indiquant que le signal est à bas niveau ou désactivé.

- Inconnu : Un point d’interrogation ou un symbole spécifique lorsque l’état est indéfini.

4. Valeurs des signaux

Pour des signaux complexes tels que les bus de données, le diagramme peut montrer la valeur réelle transmise. Cela est crucial lors de la modélisation de protocoles où des motifs de données spécifiques déclenchent des comportements matériels précis.

🔌 Modélisation des interfaces matériel-logiciel

L’intersection entre matériel et logiciel est là où se produisent la plupart des erreurs de temporisation. Le logiciel suppose que le matériel se comporte de manière prévisible ; le matériel réagit aux contraintes physiques. Un diagramme de temporisation comble cet écart.

Scénario : Contrôle GPIO et gestion des interruptions

Considérons un système où un microcontrôleur contrôle un capteur via une broche d’entrée/sortie générale (GPIO). Le logiciel doit lire les données du capteur immédiatement après un déclenchement.

Les éléments suivants sont critiques :

- Signal de déclenchement : Le logiciel écrit une valeur sur le GPIO.

- Délai de propagation : Le temps nécessaire au signal pour traverser le circuit.

- Réponse du capteur : Le temps que met le capteur à stabiliser les données.

- Latence de lecture : Le temps nécessaire au processeur pour récupérer les données.

Un diagramme de temporisation visualise l’écart entre l’écriture logicielle et la lecture matérielle. Si cet écart est trop petit, la lecture pourrait échouer. Si l’écart est trop grand, le système devient inefficace.

Scénario : Latence des interruptions

Les interruptions sont des événements asynchrones. Le diagramme doit montrer la transition du flux d’exécution normal vers la routine de service d’interruption (ISR).

- Activation de l’interruption : La broche matérielle passe à un niveau haut.

- Changement de contexte : Le logiciel enregistre l’état actuel.

- Exécution de la routine d’interruption : Le gestionnaire s’exécute.

- Restauration du contexte : Le logiciel reprend la tâche précédente.

Modéliser cette séquence aide les ingénieurs à calculer la latence maximale, un indicateur critique pour les systèmes temps réel.

📊 Analyse des contraintes de temporisation

Les contraintes sont les règles qui régissent le diagramme. Elles garantissent que la conception répond aux exigences de performance. Elles sont souvent exprimées sous forme d’inégalités ou de fenêtres de temps spécifiques.

Temps de préparation et temps de maintien

Dans les systèmes synchrones, les données doivent être stables avant et après une transition d’horloge. Les diagrammes de temporisation montrent explicitement ces fenêtres.

| Type de contrainte | Description | Impact sur la conception |

|---|---|---|

| Temps de préparation | Le temps pendant lequel les données doivent être stables avant l’arête d’horloge. | Exige une horloge plus lente ou un matériel plus rapide. |

| Temps de maintien | Le temps pendant lequel les données doivent rester stables après l’arête d’horloge. | Exige un tampon ou une horloge plus lente. |

| Délai de propagation | Temps nécessaire au signal pour voyager de la source à la destination. | Influence la fréquence maximale d’horloge. |

Jitter et variabilité

Tous les événements ne se produisent pas exactement au même moment. Le jitter est la variation dans le moment d’un signal. Dans un diagramme, cela est souvent représenté par une région ombragée ou une plage de bords possibles.

- Grand jitter :Indique une instabilité, souvent due au bruit ou à des problèmes d’alimentation.

- Faible jitter :Indique un système stable et prévisible.

Lors de la modélisation des interfaces, les concepteurs doivent tenir compte du jitter maximal. Si la fenêtre de temporisation est trop étroite, le système devient instable.

🛠️ Meilleures pratiques pour une modélisation efficace

Créer un diagramme est facile ; en créer un utile exige de la discipline. Suivez ces directives pour garantir clarté et utilité.

- Définissez clairement le périmètre : Déterminez si vous modélisez des microsecondes ou des secondes. N’utilisez pas plusieurs niveaux de granularité sans échelle claire.

- Libellez les signaux explicitement : Utilisez des noms correspondant au schéma matériel (par exemple,

INT0,CS_N). - Montrez les régions actives : Mettez en évidence où le signal charge la charge par rapport au moment où il est flottant.

- Incluez les conditions d’erreur : Montrez ce qui se produit en cas de défaillance de temporisation. Cela aide au débogage.

- Alignez-vous sur les cycles d’horloge : Si le système est synchronisé, alignez les lignes verticales de la grille sur les fronts d’horloge pour référence.

Péchés courants à éviter

Évitez ces erreurs pour gagner du temps pendant le processus de revue.

- Surcomplexité : Ne modélisez pas chaque cycle d’instruction individuellement, sauf si nécessaire. Concentrez-vous sur le comportement de l’interface.

- Ignorer les événements asynchrones : Les interruptions et les déclencheurs externes rompent souvent le flux. Assurez-vous qu’ils sont représentés.

- Mélanger les niveaux : N’utilisez pas simultanément le timing du protocole de haut niveau et le signal électrique de bas niveau dans la même vue.

- Supposer des conditions idéales : Le matériel réel présente une résistance et une capacité. Modélisez les délais de manière réaliste.

🔄 Intégration avec d’autres diagrammes

Les diagrammes de timing n’existent pas en isolation. Ils complètent d’autres diagrammes UML pour offrir une vue complète du système.

Diagrammes de séquence

Les diagrammes de séquence montrent l’ordre des messages. Les diagrammes de timing ajoutent la dimension du temps. Utilisez un diagramme de séquence pour définir le flux, puis utilisez un diagramme de timing pour valider le timing des messages critiques.

Diagrammes d’états-machine

Les machines d’état définissent la logique d’un objet. Les diagrammes de temporisation définissent la durée des états. Par exemple, une machine d’état peut indiquer « Attendre une entrée ». Le diagramme de temporisation montre exactement combien de temps dure cette attente.

Diagrammes d’activité

Les diagrammes d’activité montrent le flux de travail. Les diagrammes de temporisation peuvent être utilisés pour annoter des activités spécifiques avec leur temps d’exécution. Cela est utile pour l’analyse des performances.

📡 Scénarios du monde réel

Examinons maintenant comment ces diagrammes s’appliquent à des domaines industriels spécifiques.

1. Systèmes automobiles

Les électroniques automobiles nécessitent un contrôle strict du temps pour des raisons de sécurité. Un signal de freinage doit atteindre le contrôleur en quelques millisecondes. Les diagrammes de temporisation sont utilisés pour vérifier que le bus réseau de contrôle (CAN) respecte ces exigences de latence.

- Focus : Latence et jitter.

- Contrainte : Exigences de temps réel strict.

2. IoT industriel

Les dispositifs IoT fonctionnent souvent avec une alimentation limitée. Les diagrammes de temporisation aident à optimiser les cycles de veille. Le logiciel peut être modélisé pour réveiller le matériel uniquement lorsque cela est nécessaire, réduisant ainsi la consommation d’énergie.

- Focus : Transitions d’état d’alimentation.

- Contrainte : Efficacité énergétique.

3. Télécommunications

Les protocoles réseau reposent sur une synchronisation précise. Les diagrammes de temporisation modélisent l’échange de signaux entre les dispositifs afin de garantir l’intégrité des données sur de longues distances.

- Focus : Délai de propagation et synchronisation.

- Contrainte : Débit de données.

🔍 Vérification et validation

Une fois le diagramme créé, il doit être validé. Ce processus garantit que le modèle correspond à l’implémentation physique.

Simulation

Utilisez des environnements de simulation pour tester la logique de temporisation. Fournissez des signaux d’entrée et observez la sortie par rapport au diagramme. Les écarts indiquent des défauts de conception.

Analyse statique

Examinez le diagramme pour vérifier sa cohérence logique. Y a-t-il des signaux qui changent d’état sans déclencheur ? Y a-t-il des blocages où un état d’attente dure indéfiniment ?

Revue de code

Comparez le code d’implémentation avec le schéma. Le code inclut-il les délais nécessaires ? Gère-t-il les interruptions avec la priorité correcte ? Le schéma sert de document de référence.

📝 Résumé des bonnes pratiques

Une modélisation efficace des interfaces matériels-logiciels exige une compréhension approfondie des deux domaines. Les diagrammes de temporisation fournissent la clarté nécessaire.

- Clarté : Assurez-vous que les lignes de vie et les signaux sont clairement étiquetés.

- Précision : Utilisez des unités de temps et des contraintes précises.

- Complétude : Incluez les chemins d’erreur et les événements asynchrones.

- Conformité : Maintenez le schéma synchronisé avec le code et les schémas.

En suivant ces principes, les équipes peuvent réduire les risques d’intégration et garantir des performances systèmes robustes. L’effort investi dans la modélisation se révèle payant lors des phases de débogage et de maintenance.

🚀 Considérations finales

Le paysage des systèmes embarqués continue d’évoluer. À mesure que les dispositifs deviennent plus complexes, la nécessité de modèles de temporisation précis augmente. Les diagrammes de temporisation UML offrent un langage standardisé pour discuter de ces complexités.

Lorsque vous commencez votre prochain projet, commencez par cartographier les interfaces critiques. Identifiez les points où le timing est impératif. Utilisez le schéma pour fixer les attentes des équipes matérielles et logicielles. Cette compréhension partagée prévient les malentendus et accélère le développement.

Souvenez-vous qu’un schéma est un document vivant. Mettez-le à jour au fur et à mesure des changements de conception. Si une nouvelle contrainte est ajoutée, reflétez-la dans le modèle. Cela maintient la documentation précise et utile tout au long du cycle de vie du produit.

Avec la bonne approche, les diagrammes de temporisation deviennent bien plus que de simples documents. Ils deviennent un outil d’analyse, une référence pour l’implémentation et une norme d’assurance qualité. Adoptez la précision qu’ils offrent pour construire des systèmes fiables, efficaces et robustes.