設計即時系統需要精確性。當訊號必須在特定時間窗內到達,且狀態變更必須可預測時,標準建模方法往往無法滿足需求。你面對的是不僅僅是流動的邏輯;它會脈衝、等待並過期。在這個領域中,選擇正確的統一模型語言(UML)符號不僅僅是美學上的選擇,更是一項影響系統正確性的關鍵工程決策。

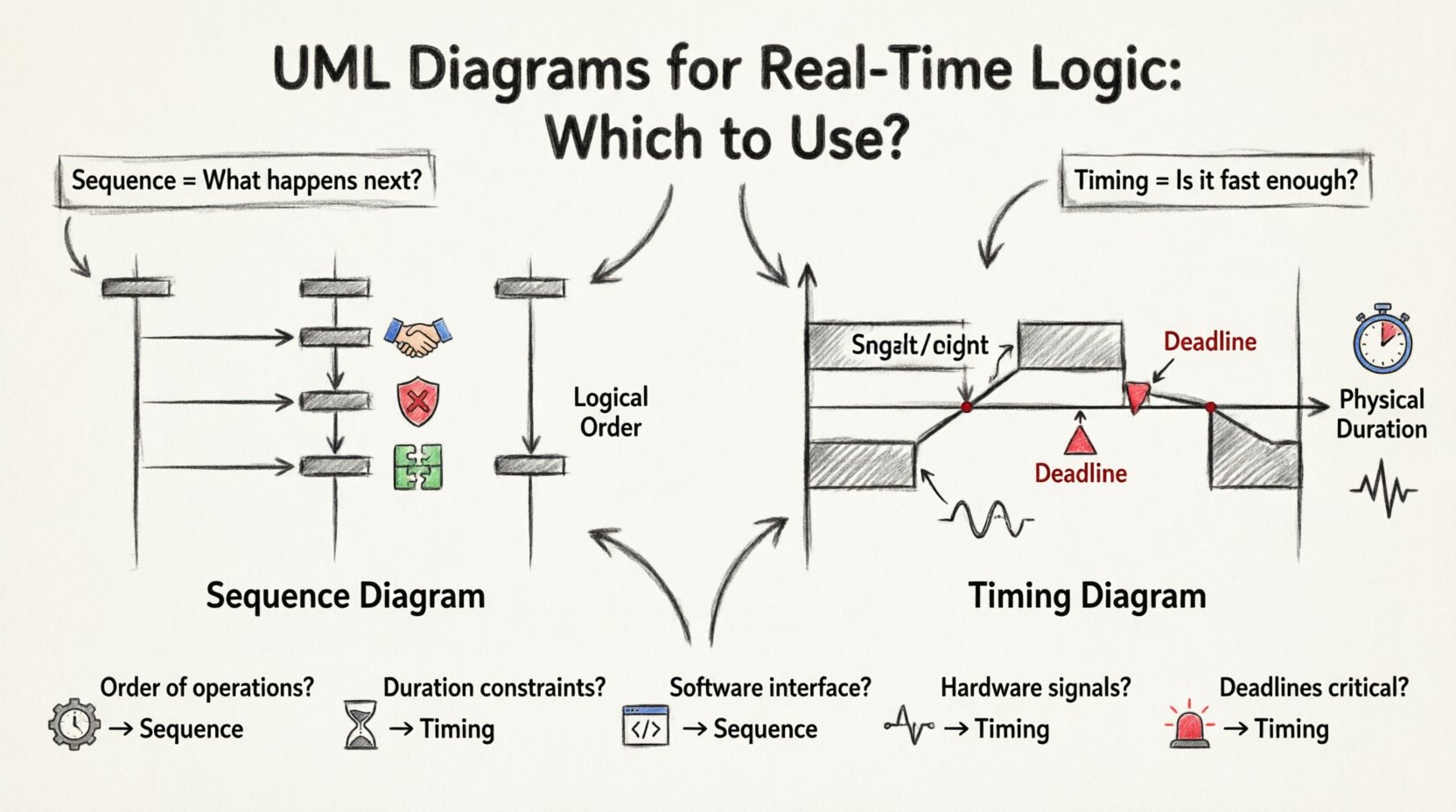

在互動建模討論中,兩種主要的圖表類型佔據主導地位:UML 序列圖 以及 UML 時序圖兩者都能呈現行為,但捕捉的是系統現實的不同面向。一種專注於訊息的順序;另一種則專注於物件在時間上的持續時間與狀態。

本指南提供深入的技術比較。我們將剖析每種圖表如何處理同步、延遲與狀態約束。結束後,你將清楚了解在何種情況下應使用時序圖,何種情況下應使用序列圖來建構你的即時邏輯架構。

📡 在即時環境中理解序列圖

UML 序列圖是業界標準,用於呈現互動順序。它以垂直排列物件、水平排列訊息的方式,呈現物件在時間上的溝通方式。在即時邏輯的脈絡中,它擅長定義 邏輯流程 而非 實際持續時間.

- 重點:訊息傳遞與控制流程。

- 時間軸:隱含的。時間由上而下流動,但時間尺度未明確定義。

- 關鍵元素:生命線、激活條、訊息(同步/非同步)以及回傳值。

- 最適合:定義演算法、握手協定以及操作順序。

在建模即時系統時,序列圖回答的問題是:「接下來會發生什麼?」它對於調試依賴執行順序而非執行速度的競爭條件極為重要。

序列圖的關鍵元件

要有效使用此工具,你必須理解其結構性術語:

- 生命線:代表類別或組件的實例。在即時系統中,這些通常代表感測器、控制器或通訊匯流排。

- 激活條: 顯示物件執行動作的時機。這表示控制權的轉移。

- 同步訊息: 以實心箭頭表示。發送者會等待回應後才繼續執行。這對於阻塞式邏輯至關重要。

- 非同步訊息: 以空心箭頭表示。發送者會立即繼續執行。這用來模擬事件驅動架構中常見的「發送後忘記」情境。

- 合併片段: 方框如

alt,opt,以及loop讓您能在不使圖表混亂的情況下,模擬條件邏輯與迴圈。

⏱️ 在即時情境中理解時序圖

UML 時序圖經常被忽略,但它卻是模擬時間關鍵行為的決定性工具。與抽象時間的序列圖不同,時序圖將時間視為主要軸線。它顯示物件狀態如何在特定時間軸上變化。

- 重點: 隨時間變化的狀態變更與訊號值。

- 時間軸: 明確的。沿著圖表頂部水平延伸。

- 關鍵元素: 狀態機、數值範圍、訊號轉換與截止時間。

- 最適合應用於: 定義延遲限制、抖動分析與狀態有效性時間窗。

在即時邏輯中,時序圖回答的問題是:「這是否發生得足夠快,且持續多久?」 當系統必須在 5 毫秒內回應感測器輸入,或在特定時間內維持訊號電壓高於某閾值時,此圖表尤為重要。

時序圖的關鍵組成部分

掌握此圖表需要關注其時間機制:

- 時間尺度: 橫軸代表時間。可為絕對時間(時鐘時間)或相對時間(經過時間)。

- 狀態條:水平條表示物件的狀態(例如:啟用、閒置、錯誤)。條的長度代表持續時間。

- 數值範圍:與離散訊息不同,你經常會看到數值範圍(例如:電壓:0V 至 5V)。這對物理系統至關重要。

- 信號轉換:垂直線穿過狀態條表示數值或狀態的改變。

- 約束條件:文字方塊或註解可用來指定硬性截止時間(例如:

<截止時間>).

🆚 核心差異:技術性比較

為了做出明智的決策,我們必須觀察這兩種符號之間的結構與語義差異。下表概述了與即時系統設計相關的差異。

| 功能 | 序列圖 | 時序圖 |

|---|---|---|

| 時間表示 | 邏輯順序(由上至下) | 物理持續時間(水平軸) |

| 主要關注點 | 互動流程與控制 | 狀態演變與信號值 |

| 訊息對狀態 | 著重於訊息傳遞 | 著重於狀態變更與數值 |

| 並發性 | 清楚顯示平行的生命線 | 顯示隨時間推移的平行活動 |

| 截止時間 | 透過訊息順序隱含 | 透過時間尺度與約束條件明確表示 |

| 複雜性 | 長鏈條帶來高認知負荷 | 大量訊號帶來高認知負荷 |

🛠️ 何時應使用序列圖來描述實時邏輯

雖然時序圖在時間精確性方面表現出色,但序列圖仍是互動建模的基石。當出現以下情況時,應優先使用序列圖:

- 協定定義: 您正在定義通訊協定(例如 MQTT、TCP/IP 握手)。SYN、ACK 和 FIN 包的順序比精確的毫秒延遲更重要。

- 錯誤處理: 您需要視覺化系統對失敗的反應方式。控制器如何重試請求?它如何通知使用者?序列圖能更有效地處理分支邏輯(alt/opt 段)。

- 元件整合: 您正在繪製不同軟體模組之間的互動關係。誰呼叫誰,傳遞了哪些資料?

- 演算法邏輯: 核心複雜性在於決策樹,而非執行時間。如果邏輯是

if (x > 5) then do_y,序列圖能清楚地捕捉此流程。 - 非同步事件: 實時系統通常依賴中斷。只要使用合併片段,序列圖能很好地展示主迴圈執行期間發生中斷的情況。

範例情境: 自動煞車系統接收感測器輸入。序列圖會顯示感測器將資料傳送到控制器,控制器處理輸入,再向煞車致動器發送指令。它能清楚地呈現邏輯依賴關係。

🕒 何時應使用時序圖來描述實時邏輯

當時間本身成為邏輯中的變數時,時序圖就變得不可或缺。當出現以下情況時,應切換至此符號表示法:

- 存在硬性截止時間: 如果任務必須在 10 毫秒內完成,否則系統將失敗,時序圖能清楚地顯示這個時間窗口。您可以明確繪製一條垂直線來標示截止時間。

- 訊號穩定性至關重要: 在嵌入式系統中,訊號通常需要維持高電平一段特定時間才能被識別。時序圖能清楚顯示脈衝寬度的要求。

- 抖動分析: 如果系統必須處理變動的延遲(抖動),時序圖能顯示訊息可能到達時間的範圍。

- 資源競爭: 當兩個程序競爭同一個 CPU 核心時,時序圖能顯示調度間隙,以及一個任務如何阻塞另一個任務。

- 狀態機轉換 如果裝置必須在進入「啟動」模式前於「預熱」狀態中等待 5 秒,則持續時間是關鍵限制。時序圖能明確呈現此點。

範例情境: 溫度感測器每 100 毫秒傳送一次資料。控制器必須在下一次讀取到達前處理完此資料。時序圖可顯示讀取間隔與處理時間之間的重疊(或無重疊)情況。

🔍 深入探討:處理併發與同步

即時邏輯很少是線性的。併發才是常態。兩種圖表類型處理此問題的方式不同,理解其中細節對架構設計至關重要。

序列圖中的併發

序列圖使用平行的生命線來顯示併發。若兩個物件同時處於活躍狀態,其激活條會並排運行。然而,這並不代表它們在時間上同時執行,僅表示邏輯上的交錯執行。

- 限制: 無論順序如何,若兩個程序位於不同執行緒上,你很難清楚顯示 Process A 必須在 Process B 開始前完成。

- 最佳實務: 使用

par使用「par」片段來標示並行執行區塊。這能清楚表明系統預期多個執行緒或程序同時運行。

時序圖中的併發

時序圖以空間方式處理併發。由於時間水平流動,你可以疊加多個生命線,精確觀察它們在時間上的重疊位置。

- 優勢: 你可以判斷「忙碌等待」迴圈是否真的阻塞了其他任務。你也能視覺化一個任務開始與另一個任務結束之間的時間差距。

- 限制: 若併發執行緒數量較多,它們會迅速變得雜亂。隨著訊號數量增加,視覺干擾也隨之增加。

🧩 兩種圖表的整合

在穩健的工程實務中,你很少會只選擇其中一種而捨棄另一種。最有效的文件策略是整合兩者。它們在設計生命週期中扮演互補的角色。

- 高階設計: 從 序列圖 開始使用序列圖來定義架構、訊息傳遞流程與組件邊界。這能建立邏輯合約。

- 低階規格: 使用 時序圖 來優化關鍵路徑。邏輯定義完成後,對關鍵區段套用時間約束。這能定義性能合約。

- 驗證: 測試期間,請使用時序圖來驗證延遲。使用順序圖來確認正確的訊息以正確的順序進行交換。

⚠️ 應避免的常見陷阱

即使經驗豐富的架構師在建模即時系統時也會犯錯。請對這些常見錯誤保持警覺。

- 假設順序代表持續時間: 一個常見的錯誤是查看順序圖時,假設訊息之間的垂直距離代表時間。事實並非如此。這會導致錯誤的延遲假設。

- 忽略空閒狀態: 在時序圖中,未能呈現「空閒」或「睡眠」狀態可能會隱藏功耗問題。請確保您的狀態欄涵蓋整個生命週期。

- 過度使用合併片段: 在順序圖中,過度嵌套太多

alt或opt片段會使圖表難以閱讀。應將複雜邏輯拆分為子圖。 - 混合邏輯時間與物理時間: 除非明確標示,否則不要在同一張圖中混合邏輯排序(順序)與物理時間約束(時序)。應將它們區分開來,以避免混淆。

- 忽略訊號雜訊: 在針對實體硬體的時序圖中,不要假設訊號轉換是完美的。若雜訊範圍或去彈跳時間影響邏輯,請明確標示。

📝 文件編寫的最佳實務

為確保您的圖表增加價值而非造成混亂,請遵循以下指引。

- 命名一致性: 對生命線和訊號使用一致的命名規範。若在一個圖中稱某訊號為「ReadSensor」,在另一個圖中就不應稱為「GetData」。

- 專注於關鍵路徑: 不要試圖繪製每一個功能。專注於涉及時序約束或關鍵失敗的路徑。簡要記錄正常流程,但詳細說明邊界情況。

- 使用註解: 兩種圖表類型都支援註解。請使用它們來定義單位(毫秒、微秒)、容差和特定需求。在即時設計中,沒有單位的數字毫無意義。

- 版本控制: 將圖表視為程式碼。將它們儲存在版本控制中。時序約束的變更應像程式碼變更一樣經過審查。

- 與利害關係人共同審查: 與開發人員(邏輯)審查順序圖,與系統工程師(效能)審查時序圖。確保受眾與圖表類型相符。

🚀 進階考量:狀態機

即時系統通常是由事件驅動的。這使我們進入狀態機與UML圖表的交集處。

- 序列圖 + 狀態機:使用序列圖來顯示狀態機轉換如何由外部訊息觸發。顯示訊息進入生命線,以及內部狀態變化的發生。

- 時序圖 + 狀態機:使用時序圖來顯示狀態的持續時間。例如,「逾時」狀態可能恰好持續3秒。時序圖會將此持續時間相對於其他事件進行視覺化。

在建模複雜的嵌入式邏輯時,將狀態機圖與時序圖結合,通常是對時間上行為最準確的呈現。

📊 決策因素總結

為協助您的決策過程,請考慮此檢查清單。

- 主要關注的是操作的順序嗎? ➝ 使用序列圖。

- 主要關注的是操作的持續時間嗎? ➝ 使用時序圖。

- 您是否在定義軟體介面? ➝ 使用序列圖。

- 您是否在定義硬體訊號需求? ➝ 使用時序圖。

- 邏輯是否依賴於截止時間? ➝ 使用時序圖。

- 邏輯是否依賴於訊息協定? ➝ 使用序列圖。

🔚 最後想法

在UML時序圖與序列圖之間做選擇,並非出於偏好,而是對系統限制的忠實度。序列圖描繪互動的邏輯,時序圖則描繪執行的物理特性。

在即時邏輯領域中,模糊性是敵人。透過選擇正確的工具,您能減少模糊性。您為團隊提供了一個清晰的藍圖,區分系統做什麼以及必須在何時執行。這種清晰度直接轉化為穩健、可靠且安全的系統。

從流程開始。驗證時序。雙方皆需記錄。這種雙重方法確保您的即時邏輯不僅功能正確,而且時序上也穩妥。