La conception de systèmes en temps réel exige une précision. Lorsque les signaux doivent arriver dans des fenêtres spécifiques, et que les changements d’état doivent se produire de manière prévisible, la modélisation classique est souvent insuffisante. Vous avez affaire à une logique qui ne se contente pas de s’écouler ; elle pulse, attend et expire. Dans ce contexte, choisir la bonne notation du langage de modélisation unifié (UML) n’est pas simplement une question de style. C’est une décision d’ingénierie cruciale qui affecte la correction du système.

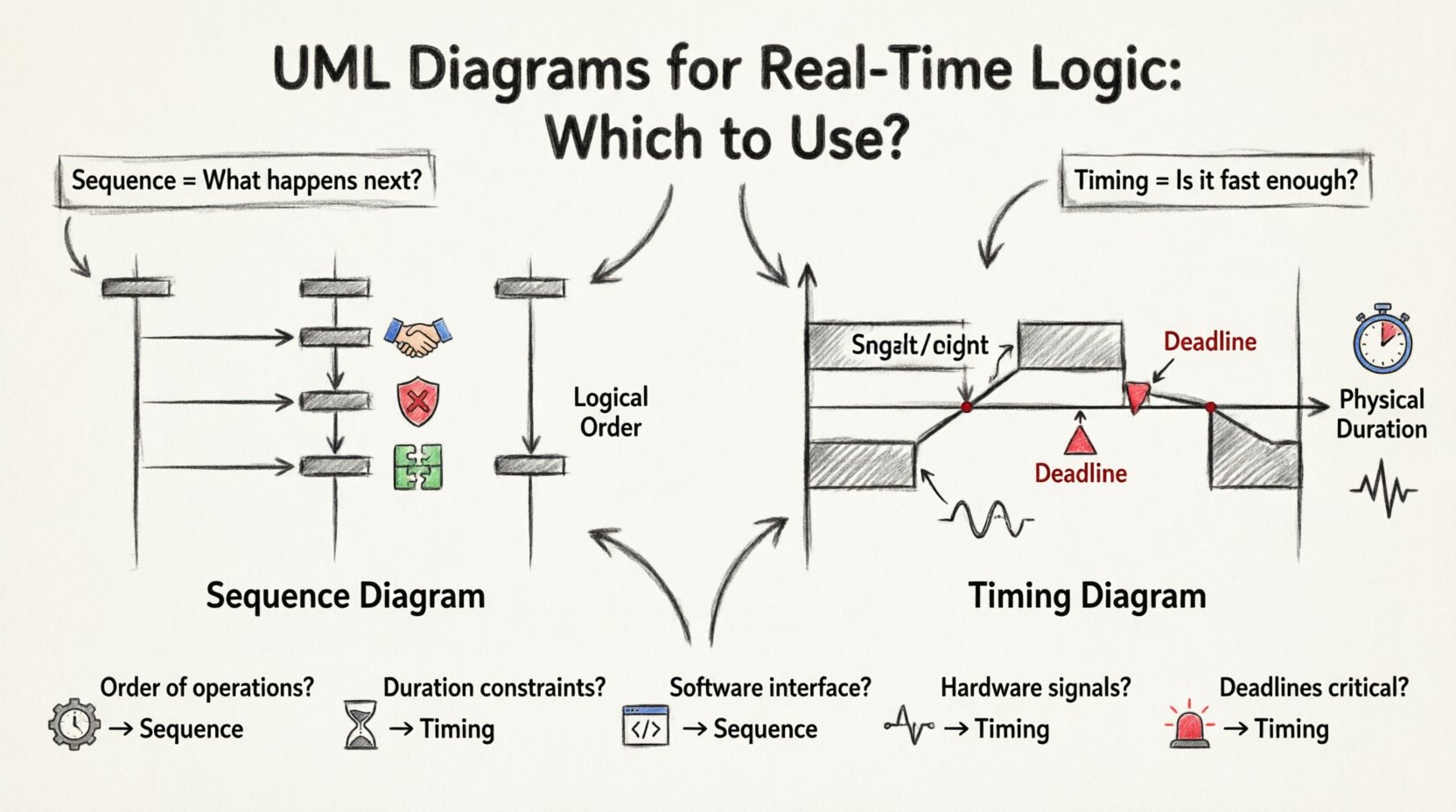

Deux types principaux de diagrammes dominent les discussions sur la modélisation des interactions : le Diagramme de séquence UML et le Diagramme de temporisation UML. Les deux visualisent le comportement, mais captent des dimensions différentes de la réalité du système. L’un se concentre sur l’ordre des messages ; l’autre se concentre sur la durée et l’état des objets au fil du temps.

Ce guide propose une comparaison technique approfondie. Nous analyserons comment chaque diagramme gère la synchronisation, la latence et les contraintes d’état. À la fin, vous comprendrez exactement quand déployer un diagramme de temporisation plutôt qu’un diagramme de séquence dans votre architecture logicielle en temps réel.

📡 Comprendre le diagramme de séquence dans un contexte en temps réel

Le diagramme de séquence UML est la norme de l’industrie pour visualiser l’ordre des interactions. Il montre comment les objets communiquent au fil du temps, en disposant les objets verticalement et les messages horizontalement. Dans le contexte de la logique en temps réel, il excelle à définir le flux logique plutôt que le durée physique.

- Focus :Passage des messages et flux de contrôle.

- Axe du temps :Implicite. Le temps s’écoule du haut vers le bas, mais l’échelle n’est pas définie.

- Éléments clés :Lignes de vie, barres d’activation, messages (synchrone/asynchrone) et valeurs de retour.

- Idéal pour :Définir l’algorithme, les protocoles d’échange, et la séquence des opérations.

Lors de la modélisation d’un système en temps réel, le diagramme de séquence répond à la question :« Qu’est-ce qui se passe ensuite ? » Il est inestimable pour le débogage des conditions de course qui dépendent de l’ordre d’exécution plutôt que de la vitesse d’exécution.

Composants clés d’un diagramme de séquence

Pour utiliser cet outil efficacement, vous devez comprendre son vocabulaire structurel :

- Lignes de vie : Représentent des instances de classes ou de composants. Dans les systèmes en temps réel, ils représentent souvent des capteurs, des contrôleurs ou des bus de communication.

- Barres d’activation : Affiche quand un objet effectue une action. Cela indique un transfert de contrôle.

- Messages synchrones : Représentés par des flèches pleines. L’expéditeur attend une réponse avant de poursuivre. Cela est crucial pour la logique bloquante.

- Messages asynchrones : Représentés par des flèches ouvertes. L’expéditeur continue immédiatement. Cela modélise des scénarios de type « déclencher et oublier », courants dans les architectures orientées événements.

- Fragments combinés : Boîtes telles que

alt,opt, etbouclevous permettent de modéliser la logique conditionnelle et les itérations sans encombrer le diagramme.

⏱️ Comprendre le diagramme de temporisation dans un contexte temps réel

Le diagramme de temporisation UML est souvent négligé, pourtant il est l’outil incontournable pour modéliser les comportements critiques en temps. Contrairement au diagramme de séquence, qui abstrait le temps, le diagramme de temporisation considère le temps comme un axe principal. Il montre comment l’état d’un objet évolue au fil d’une timeline spécifique.

- Focus : Évolutions d’état et valeurs des signaux au fil du temps.

- Axe du temps : Explicite. Il s’étend horizontalement en haut du diagramme.

- Éléments clés : Machines à états, plages de valeurs, transitions de signaux et délais.

- Idéal pour : Définir des contraintes de latence, analyser le jitter et déterminer les fenêtres de validité des états.

Dans la logique temps réel, le diagramme de temporisation répond à la question :« Cela se produit-il assez rapidement, et pendant combien de temps ? » Il est essentiel lorsque le système doit répondre à une entrée de capteur en moins de 5 millisecondes ou maintenir une tension de signal au-dessus d’un seuil pendant une durée spécifique.

Composants clés d’un diagramme de temporisation

Maitriser ce diagramme exige une attention particulière à ses mécanismes temporels :

- Échelle du temps : L’axe horizontal représente le temps. Il peut être absolu (heure du chronomètre) ou relatif (temps écoulé).

- Barres d’état :Les barres horizontales indiquent l’état d’un objet (par exemple, Actif, Inactif, Erreur). La longueur de la barre représente la durée.

- Plages de valeurs :Plutôt que des messages discrets, on voit souvent des plages de valeurs (par exemple, Tension : 0 V à 5 V). Cela est crucial pour les systèmes physiques.

- Transitions de signal :Les lignes verticales traversant les barres d’état indiquent un changement de valeur ou d’état.

- Contraintes :Les zones de texte ou les annotations peuvent spécifier des délais stricts (par exemple,

<délai>).

🆚 Différences fondamentales : Une comparaison technique

Pour prendre une décision éclairée, nous devons examiner les différences structurelles et sémantiques entre ces deux notations. Le tableau suivant décrit les distinctions pertinentes pour la conception de systèmes temps réel.

| Fonctionnalité | Diagramme de séquence | Diagramme de timing |

|---|---|---|

| Représentation du temps | Ordre logique (du haut vers le bas) | Durée physique (axe horizontal) |

| Focus principal | Flux d’interaction et de contrôle | Évolution de l’état et valeurs des signaux |

| Message vs. État | Se concentre sur le passage de messages | Se concentre sur les changements d’état et les valeurs |

| Concurrence | Montre clairement les lignes de vie parallèles | Montre les activités parallèles au fil du temps |

| Délais | Implicite via l’ordre des messages | Explicite via l’échelle de temps et les contraintes |

| Complexité | Charge cognitive élevée pour les chaînes longues | Charge cognitive élevée pour de nombreux signaux |

🛠️ Quand utiliser un diagramme de séquence pour la logique en temps réel

Alors que les diagrammes de timing excellent en précision temporelle, les diagrammes de séquence restent la base de la modélisation des interactions. Vous devez privilégier le diagramme de séquence lorsque :

- Définition du protocole : Vous définissez un protocole de communication (par exemple, MQTT, handshake TCP/IP). L’ordre des paquets SYN, ACK et FIN est plus important que le délai exact en millisecondes.

- Gestion des erreurs : Vous devez visualiser la réaction du système aux défaillances. Comment le contrôleur réessaie-t-il une requête ? Comment informe-t-il l’utilisateur ? Les diagrammes de séquence gèrent mieux la logique conditionnelle (fragments alt/opt).

- Intégration des composants : Vous cartographiez l’interaction entre des modules logiciels distincts. Qui appelle qui, et quelles données sont échangées ?

- Logique de l’algorithme : La complexité fondamentale réside dans l’arbre de décision, et non dans le temps d’exécution. Si la logique est

si (x > 5) alors faire_y, un diagramme de séquence représente clairement ce flux. - Événements asynchrones : Les systèmes en temps réel reposent souvent sur des interruptions. Les diagrammes de séquence sont excellents pour montrer une interruption survenant pendant l’exécution d’une boucle principale, à condition d’utiliser des fragments combinés.

Scénario d’exemple : Un système de freinage automatique reçoit une entrée du capteur. Le diagramme de séquence montrerait le capteur envoiant des données au contrôleur, le contrôleur traitant l’entrée, puis envoyant une commande à l’actionneur de frein. Il modélise la dépendance logique.

🕒 Quand utiliser un diagramme de timing pour la logique en temps réel

Le diagramme de timing devient obligatoire lorsque le temps lui-même est une variable dans la logique. Vous devez passer à cette notation lorsque :

- Des délais stricts existent : Si une tâche doit être terminée en moins de 10 ms, sinon le système échoue, un diagramme de timing visualise la fenêtre. Vous pouvez dessiner explicitement une ligne verticale marquant la date limite.

- La stabilité du signal est importante : Dans les systèmes embarqués, les signaux doivent souvent rester à l’état haut pendant une durée spécifique pour être reconnus. Un diagramme de timing montre les exigences de largeur d’impulsion.

- Analyse du jitter : Si le système doit gérer des délais variables (jitter), un diagramme de timing peut montrer la plage de temps d’arrivée possible d’un message.

- Contestation des ressources : Lorsque deux processus s’affrontent pour un cœur de processeur, un diagramme de timing peut montrer les intervalles d’ordonnancement et comment une tâche bloque l’autre.

- Transitions de machine à états Si un périphérique doit attendre dans un état « Démarrage » pendant 5 secondes avant d’entrer en mode « Actif », la durée est la contrainte critique. Un diagramme de timing rend cela explicite.

Scénario d’exemple : Un capteur de température envoie des données toutes les 100 ms. Le contrôleur doit traiter ces données avant que la prochaine lecture n’arrive. Un diagramme de timing montre le chevauchement (ou l’absence de chevauchement) entre l’intervalle de lecture et la durée de traitement.

🔍 Approfondissement : Gestion de la concurrence et de la synchronisation

La logique en temps réel est rarement linéaire. La concurrence est la règle. Les deux types de diagrammes gèrent cela différemment, et comprendre cette nuance est essentiel pour l’architecture.

La concurrence dans les diagrammes de séquence

Les diagrammes de séquence utilisent des lignes de vie parallèles pour montrer la concurrence. Si deux objets sont actifs simultanément, leurs barres d’activation s’exécutent côte à côte. Toutefois, cela ne garantit pas une exécution simultanée dans le temps. Il ne garantit que le chevauchement logique.

- Limitation : Vous ne pouvez pas facilement montrer qu’un processus A doit se terminer avant que le processus B ne commence, indépendamment de l’ordre, s’ils sont sur des threads différents.

- Meilleure pratique : Utilisez

pardes fragments pour indiquer des blocs d’exécution parallèles. Cela clarifie que le système attend que plusieurs threads ou processus s’exécutent de manière concurrente.

La concurrence dans les diagrammes de timing

Les diagrammes de timing gèrent la concurrence de manière spatiale. Étant donné que le temps s’écoule horizontalement, vous pouvez empiler plusieurs lignes de vie et voir exactement où elles se chevauchent dans le temps.

- Avantage : Vous pouvez voir si une boucle « Busy Wait » bloque réellement d’autres tâches. Vous pouvez visualiser l’écart entre le début d’une tâche et la fin d’une autre.

- Limitation : Ils peuvent rapidement devenir encombrés si vous avez de nombreux threads concurrents. Le bruit visuel augmente avec le nombre de signaux.

🧩 Intégration des deux diagrammes

Dans une ingénierie robuste, vous choisissez rarement l’un et rejetez l’autre. La stratégie de documentation la plus efficace intègre les deux. Ils remplissent des rôles complémentaires tout au long du cycle de conception.

- Conception de haut niveau : Commencez par les diagrammes de séquence pour définir l’architecture, le flux de messages et les limites des composants. Cela établit le contrat logique.

- Spécification de bas niveau : Affinez les chemins critiques avec les diagrammes de timing. Une fois la logique définie, appliquez des contraintes temporelles aux sections critiques. Cela définit le contrat de performance.

- Vérification : Pendant les tests, utilisez le diagramme de timing pour vérifier la latence. Utilisez le diagramme de séquence pour vérifier que les messages corrects ont été échangés dans le bon ordre.

⚠️ Pièges courants à éviter

Même les architectes expérimentés commettent des erreurs lors de la modélisation des systèmes en temps réel. Soyez vigilant face à ces erreurs courantes.

- Supposer que la séquence implique une durée : Une erreur courante consiste à regarder un diagramme de séquence et à supposer que la distance verticale entre les messages représente le temps. Ce n’est pas le cas. Cela conduit à des hypothèses erronées sur la latence.

- Ignorer les états inactifs : Dans les diagrammes de timing, l’omission de la représentation de l’état « Inactif » ou « Veille » peut masquer des problèmes de consommation d’énergie. Assurez-vous que vos barres d’état couvrent toute la durée de vie.

- Utilisation excessive des fragments combinés : Dans les diagrammes de séquence, imbriquer trop de

altouoptblocs rend le diagramme illisible. Divisez la logique complexe en sous-diagrammes. - Mélanger le temps logique et le temps physique : N’utilisez pas simultanément l’ordre logique (séquence) et les contraintes de temps physique (timing) dans le même diagramme, sauf si clairement indiqué. Gardez-les distincts pour éviter toute confusion.

- Ne pas tenir compte du bruit des signaux : Dans les diagrammes de timing pour le matériel physique, ne supposez pas de transitions de signal parfaites. Indiquez les marges de bruit ou les temps de débouncing si elles affectent la logique.

📝 Meilleures pratiques pour la documentation

Pour garantir que vos diagrammes apportent de la valeur plutôt que du désordre, suivez ces directives.

- Nommage cohérent : Utilisez des conventions de nommage cohérentes pour les lignes de vie et les signaux. Si vous appelez un signal « ReadSensor » dans un diagramme, ne l’appelez pas « GetData » dans un autre.

- Se concentrer sur les chemins critiques : N’essayez pas de diagrammer chaque fonction individuelle. Concentrez-vous sur les chemins impliquant des contraintes de temps ou des défaillances critiques. Documentez rapidement le parcours normal, mais détaillez les cas limites.

- Utilisez des annotations : Les deux types de diagrammes supportent les annotations. Utilisez-les pour définir les unités (ms, µs), les tolérances et les exigences spécifiques. Un nombre sans unité est sans signification en conception en temps réel.

- Contrôle de version : Traitez les diagrammes comme du code. Stockez-les dans un système de contrôle de version. Les modifications des contraintes de timing doivent être revues comme les modifications de code.

- Revisez avec les parties prenantes : Revisez les diagrammes de séquence avec les développeurs (logique). Revisez les diagrammes de timing avec les ingénieurs système (performance). Assurez-vous que le public correspond au type de diagramme.

🚀 Considérations avancées : Machines à états

Les systèmes temps réel sont souvent pilotés par des événements. Cela nous amène à l’intersection entre les machines d’état et les diagrammes UML.

- Diagrammes de séquence + Machines d’état :Utilisez les diagrammes de séquence pour montrer comment une transition de machine d’état est déclenchée par un message externe. Montrez le message entrant dans la ligne de vie et le changement d’état interne qui se produit.

- Diagrammes de temporisation + Machines d’état :Utilisez les diagrammes de temporisation pour montrer la durée d’un état. Par exemple, un état « Timeout » pourrait durer exactement 3 secondes. Le diagramme de temporisation visualise cette durée par rapport aux autres événements.

Lors de la modélisation de logiques embarquées complexes, combiner un diagramme de machine d’état avec un diagramme de temporisation est souvent la représentation la plus précise du comportement dans le temps.

📊 Résumé des facteurs de décision

Pour vous aider dans votre processus de décision, envisagez cette liste de vérification.

- La préoccupation principale est-elle l’ordre des opérations ? ➝ Utilisez le diagramme de séquence.

- La préoccupation principale est-elle la durée d’une opération ? ➝ Utilisez le diagramme de temporisation.

- Définissez-vous une interface logicielle ? ➝ Utilisez le diagramme de séquence.

- Définissez-vous une exigence de signal matériel ? ➝ Utilisez le diagramme de temporisation.

- La logique dépend-elle de délais ? ➝ Utilisez le diagramme de temporisation.

- La logique dépend-elle des protocoles de messages ? ➝ Utilisez le diagramme de séquence.

🔚 Réflexions finales

Le choix entre un diagramme de temporisation UML et un diagramme de séquence ne dépend pas de la préférence ; il s’agit de fidélité aux contraintes du système. Les diagrammes de séquence représentent la logique d’interaction. Les diagrammes de temporisation représentent la physique de l’exécution.

Dans le domaine de la logique temps réel, l’ambiguïté est l’ennemi. En choisissant l’outil approprié, vous réduisez l’ambiguïté. Vous fournissez à votre équipe un plan clair qui distingue ce que le système fait de quand il doit le faire. Cette clarté se traduit directement par des systèmes robustes, fiables et sûrs.

Commencez par le flux. Validez le timing. Documentez les deux. Cette approche double garantit que votre logique temps réel est non seulement correcte sur le plan fonctionnel, mais aussi cohérente dans le temps.