Diseñar sistemas en tiempo real robustos requiere una comprensión precisa de las relaciones temporales entre los componentes. Aunque los diagramas de secuencia ilustran el flujo lógico de mensajes, a menudo resultan insuficientes cuando las restricciones de tiempo se vuelven críticas. Es aquí donde el Diagrama de temporización UMLse vuelve indispensable para los arquitectos de sistemas. Proporciona una vista especializada de cómo los objetos interactúan con el tiempo, centrándose en los cambios de estado y las restricciones temporales.

En esta guía, exploramos la mecánica de modelar el manejo de interrupciones y los desencadenadores asíncronosdentro de esta notación. Estos conceptos son vitales para los sistemas embebidos, las aplicaciones críticas para la seguridad y las arquitecturas distribuidas, donde la latencia y la concurrencia determinan el éxito.

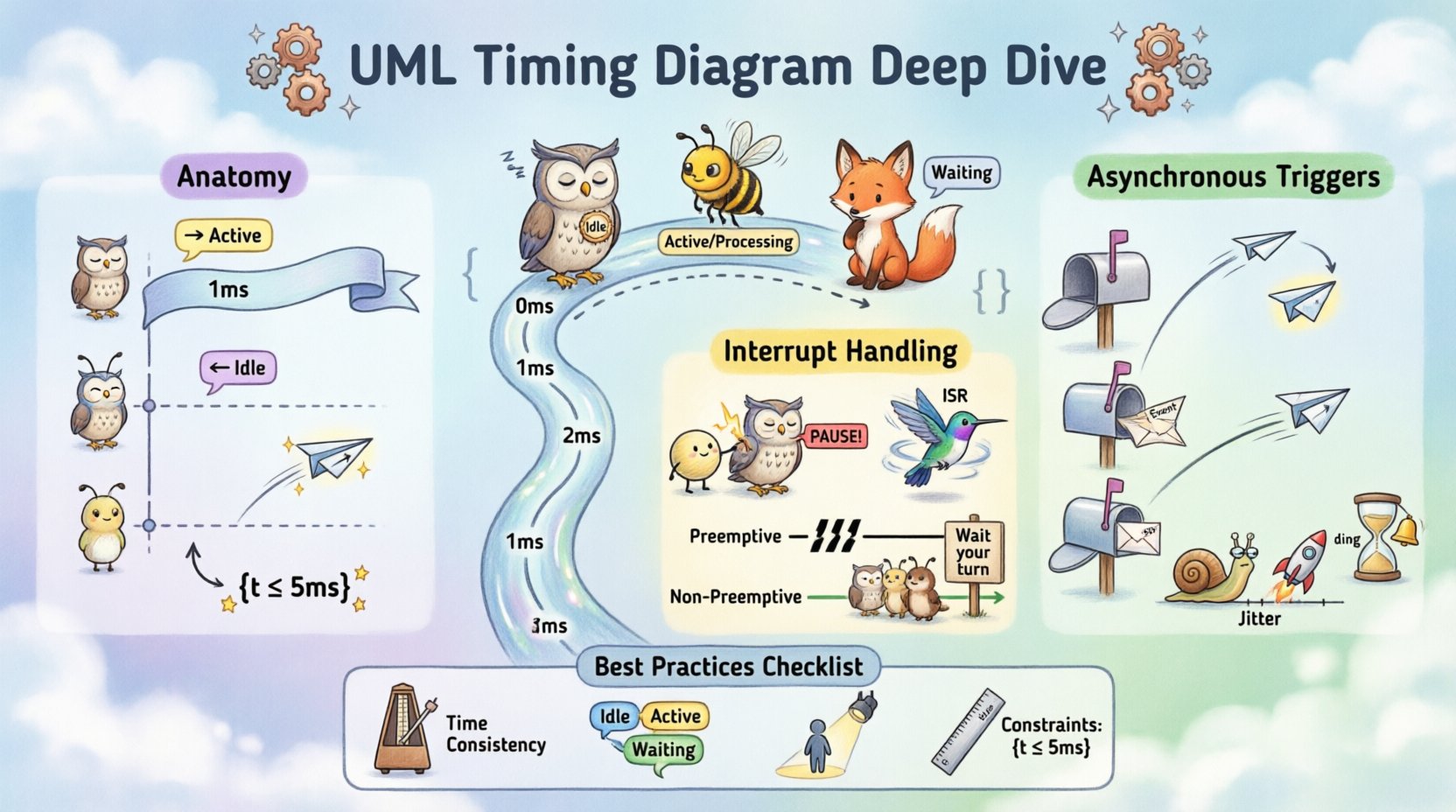

🔍 Anatomía del diagrama de temporización

Antes de adentrarnos en interacciones complejas como las interrupciones, es esencial comprender los elementos fundamentales. Un diagrama de temporización visualiza el comportamiento de objetos o líneas de vida durante una duración específica.

- Líneas de vida:Líneas verticales que representan la existencia de un objeto o componente. El tiempo avanza hacia abajo.

- Eje del tiempo:Un eje horizontal que representa la línea de tiempo, a menudo marcado con unidades como milisegundos o ciclos de reloj.

- Especificación de estado:Áreas rectangulares a lo largo de la línea de vida que indican el estado del objeto en un momento dado (por ejemplo, Activo, Inactivo, Dormido).

- Mensajes:Flechas que cruzan las líneas de vida, indicando la transmisión de señales o llamadas a métodos.

- Restricciones:Texto encerrado entre llaves

{...}que especifican requisitos temporales o condiciones.

A diferencia de otros diagramas UML, el diagrama de temporización es explícitamente temporal. No muestra únicamente *qué* ocurre, sino *cuándo* ocurre en relación con otros eventos.

⚙️ Modelado del manejo de interrupciones

Las interrupciones son señales externas que detienen temporalmente el flujo normal de ejecución para manejar un evento de alta prioridad. En los diagramas de temporización, representar estas requiere una distinción clara entre la tarea interrumpida y la rutina de servicio de interrupción.

1. Tipos de interrupciones

Comprender la naturaleza de la interrupción es crucial para un modelado preciso. Generalmente las clasificamos en dos tipos principales:

- Interrupciones de hardware:Activadas por eventos físicos (por ejemplo, una señal de sensor, llegada de un paquete de red).

- Interrupciones de software:Activadas por eventos internos (por ejemplo, división por cero, expiración del temporizador).

2. Representación visual

Para representar una interrupción, el diagrama debe mostrar la suspensión del proceso actual. Esto se logra mediante indicadores visuales específicos:

- Barras de activación:La barra del proceso actual se interrumpe con un pico o un desplazamiento hacia una barra de activación diferente que representa al manejador de interrupciones.

- Niveles de prioridad:Etiquetas que indican qué hilo o proceso posee la CPU en cualquier momento dado.

- Puntos de retorno:Indicación clara de dónde se reanuda la ejecución después de atender la interrupción.

3. Preemptivo frente a no preemptivo

El diagrama de temporización ayuda a aclarar la estrategia de programación. En un sistema preemptivo, el diagrama muestra una interrupción brusca en la tarea de baja prioridad. En un sistema no preemptivo, la solicitud de interrupción se coloca en cola hasta que la tarea actual cede voluntariamente el control.

| Característica | Interrupción preemptiva | Interrupción no preemptiva |

|---|---|---|

| Tiempo de respuesta | Inmediato | Diferido hasta la cesión |

| Cambio de contexto | Requerido | No siempre requerido |

| Complejidad del diagrama | Alta (múltiples activaciones) | Más baja (activación única) |

| Caso de uso | Bucles de control en tiempo real | Procesamiento por lotes |

📡 Disparadores asíncronos y señales

Los disparadores asíncronos ocurren cuando un emisor no espera a que el receptor esté listo. Esto es común en arquitecturas basadas en eventos. El diagrama de temporización es la herramienta ideal para visualizar la latencia entre el disparador y la respuesta.

1. La naturaleza de la asincronía

En una llamada síncrona, el llamador espera un valor de retorno. En un disparador asíncrono, el llamador envía una señal y continúa. El diagrama refleja esto mostrando la flecha de mensaje finalizando sin una flecha de retorno inmediata.

- Disparar y olvidar: El mensaje se envía y el remitente continúa de inmediato.

- Cola de eventos: El receptor procesa el evento más tarde, lo que puede mostrarse como un retraso en la barra de activación del receptor.

- Devoluciones de llamada: Un mensaje posterior vuelve al remitente después de que finaliza la tarea asíncrona.

2. Modelado de latencia

Una de las razones principales para usar un diagrama de tiempo es analizar la latencia. Al modelar disparadores asíncronos, se debe prestar atención específica al intervalo de tiempo entre la generación del evento y la ejecución del manejador.

- Jitter:Variabilidad en el tiempo que tarda en procesarse el disparador.

- Rendimiento: El volumen de eventos asíncronos que el sistema puede manejar dentro de una ventana de tiempo.

- Tiempo de espera agotado: Si no se recibe una respuesta dentro de un tiempo establecido, el diagrama debe indicar un estado de tiempo de espera agotado.

🔄 Combinación de interrupciones y disparadores asíncronos

Los sistemas complejos a menudo implican ambos mecanismos simultáneamente. Una interrupción de hardware podría desencadenar un evento de software, que luego coloca una tarea asíncrona en cola. Modelar esta interacción requiere una superposición cuidadosa de las líneas de vida.

1. La pila de interrupciones

Cuando ocurre una interrupción durante una operación asíncrona, el diagrama de tiempo debe mostrar el anidamiento. La tarea asíncrona actual se pausa, se ejecuta el manejador de interrupciones y luego la tarea original reanuda.

Esta situación destaca posibles condiciones de carrera. Si ocurren dos interrupciones de forma consecutiva, el diagrama ayuda a verificar si el sistema tiene la capacidad de manejar la profundidad de la pila sin desbordamiento.

2. Concurrencia y recursos compartidos

Los disparadores asíncronos a menudo acceden a recursos compartidos. Si una interrupción modifica un recurso mientras una tarea asíncrona lo está leyendo, puede ocurrir corrupción de datos. El diagrama de tiempo puede ilustrar los tiempos de adquisición y liberación de bloqueos.

- Bloqueo: Muestre la duración durante la cual se mantiene el recurso.

- Bloqueo: Muestre cuándo una tarea espera un bloqueo.

- Inversión de prioridad: Represente escenarios en los que una tarea de baja prioridad retiene un bloqueo necesario para una interrupción de alta prioridad.

🛠 Mejores prácticas para diagramas de tiempo

Crear diagramas de tiempo efectivos requiere disciplina. La claridad es más importante que los detalles exhaustivos en cada caso.

- Consistencia de escala de tiempo: Asegúrese de que el eje del tiempo sea consistente en todo el diagrama. Es aceptable acercarse a segmentos específicos, pero el contexto global es importante.

- Claridad de estado: Utilice colores distintos o sombreados para diferentes estados (por ejemplo, Inactivo, Procesando, Esperando).

- Líneas de vida mínimas: No incluya cada objeto del sistema. Enfóquese únicamente en aquellos involucrados en la relación de tiempo que se está analizando.

- Notación de restricciones: Utilice

{t <= 5ms}sintaxis para definir claramente plazos estrictos.

⚠️ Errores comunes y soluciones

Incluso modeladores con experiencia cometen errores al traducir la lógica temporal a diagramas. A continuación se presentan problemas comunes y cómo abordarlos.

| Error común | Impacto | Solución |

|---|---|---|

| Ignorar la latencia | El sistema no cumple con los plazos | Incluya el retardo de transmisión en las flechas de mensaje |

| Líneas de vida superpuestas | Confusión sobre el orden de ejecución | Utilice alineación vertical estricta; evite cruces de flechas cuando sea posible |

| Restricciones ambiguas | Ambigüedad en los requisitos | Utilice valores numéricos específicos (por ejemplo, 200ns en lugar de rápido) |

| Interrupciones omitidas | Latencia oculta en caminos críticos | Dibuje explícitamente las rutinas de servicio de interrupción como barras de activación separadas |

🧪 Verificación y validación

Una vez construido el diagrama de temporización, sirve como referencia para la verificación. Los ingenieros pueden comparar el comportamiento modelado con los registros reales del sistema.

- Rastreabilidad:Asocie los elementos del diagrama con funciones de código. Verifique que las restricciones de temporización en el diagrama coincidan con la implementación del código.

- Simulación:Utilice el diagrama para simular escenarios de peor caso. ¿Qué ocurre si la frecuencia de interrupción se duplica?

- Pruebas:Genere casos de prueba basados en las ventanas de tiempo definidas en el diagrama. Asegúrese de que el sistema se comporte correctamente dentro de los límites especificados.

🧠 Consideraciones avanzadas

Para sistemas altamente complejos, los diagramas de temporización estándar pueden requerir extensiones. Considere las siguientes técnicas de modelado avanzadas.

1. Diagramas de temporización jerárquicos

Cuando un subsistema tiene su propio comportamiento de temporización complejo, encápsulelo en un subdiagrama. El diagrama principal muestra el subsistema como una sola línea de vida con un resumen de su comportamiento de temporización. Esto reduce el desorden manteniendo los detalles.

2. Arquitecturas desencadenadas por tiempo

En sistemas desencadenados por tiempo, las acciones ocurren en ciclos de reloj específicos independientemente de los eventos. El diagrama debe mostrar una cuadrícula estricta o una señal de reloj que corra paralela a las líneas de vida para indicar estos momentos sincronizados.

3. Energía y temporización

En dispositivos alimentados por batería, la temporización afecta directamente el consumo de energía. Una tarea que se ejecuta más tiempo consume más energía. Agregar un eje de consumo de energía o una anotación al diagrama de temporización puede ayudar a optimizar la eficiencia energética junto con el rendimiento.

📝 Resumen de los conceptos clave

Para resumir los puntos clave de este análisis profundo:

- Diagramas de temporizaciónson el estándar para visualizar el comportamiento temporal en UML.

- Interrupcionesrequieren barras de activación distintas para mostrar la preemption y el cambio de contexto.

- Disparadores asíncronosdeben tener en cuenta la latencia y los mecanismos de cola.

- Restriccionesdeben ser explícitas y numéricas para evitar ambigüedades.

- Concurrenciaproblemas como condiciones de carrera se identifican mejor mediante líneas de vida superpuestas.

Al adherirse a estos principios de modelado, los arquitectos de sistemas pueden crear un plano claro para el comportamiento en tiempo real. Esto reduce el riesgo de defectos relacionados con el tiempo durante la fase de implementación. La inversión realizada en diagramas de temporización precisos se ve recompensada durante la integración del sistema y la depuración.

🚀 Avanzando

Implementar estos diagramas es un proceso iterativo. Comience con restricciones de tiempo de alto nivel y refine las mismas a medida que madura el diseño. La colaboración entre ingenieros de software y diseñadores de hardware es esencial, ya que el tiempo a menudo implica ambos dominios. El diagrama actúa como el lenguaje compartido entre estos grupos.

Recuerde que los diagramas son documentos vivos. A medida que el sistema evoluciona, los diagramas de tiempo deben actualizarse para reflejar nuevos requisitos o cambios en el hardware. Esto garantiza que la documentación siga siendo una referencia válida para el mantenimiento y la resolución de problemas futuros.

Una modelización eficaz de interrupciones y desencadenantes asíncronos garantiza que su sistema no solo sea funcionalmente correcto, sino también temporalmente robusto. Esta es la base de una arquitectura de software en tiempo real confiable.