La arquitectura de software depende en gran medida de la comunicación precisa entre componentes. Cuando se manejan interacciones sensibles al tiempo, el diagrama de tiempo UML se convierte en una herramienta indispensable. Sin embargo, muchos ingenieros tratan estos diagramas como una simple consideración posterior o los confunden con diagramas de secuencia. Esta confusión a menudo resulta en requisitos ambiguos, código inmanejable y un ciclo de desarrollo plagado de errores relacionados con el tiempo. Comprender los matices de las restricciones de tiempo no es opcional; es una necesidad para un diseño de sistema robusto.

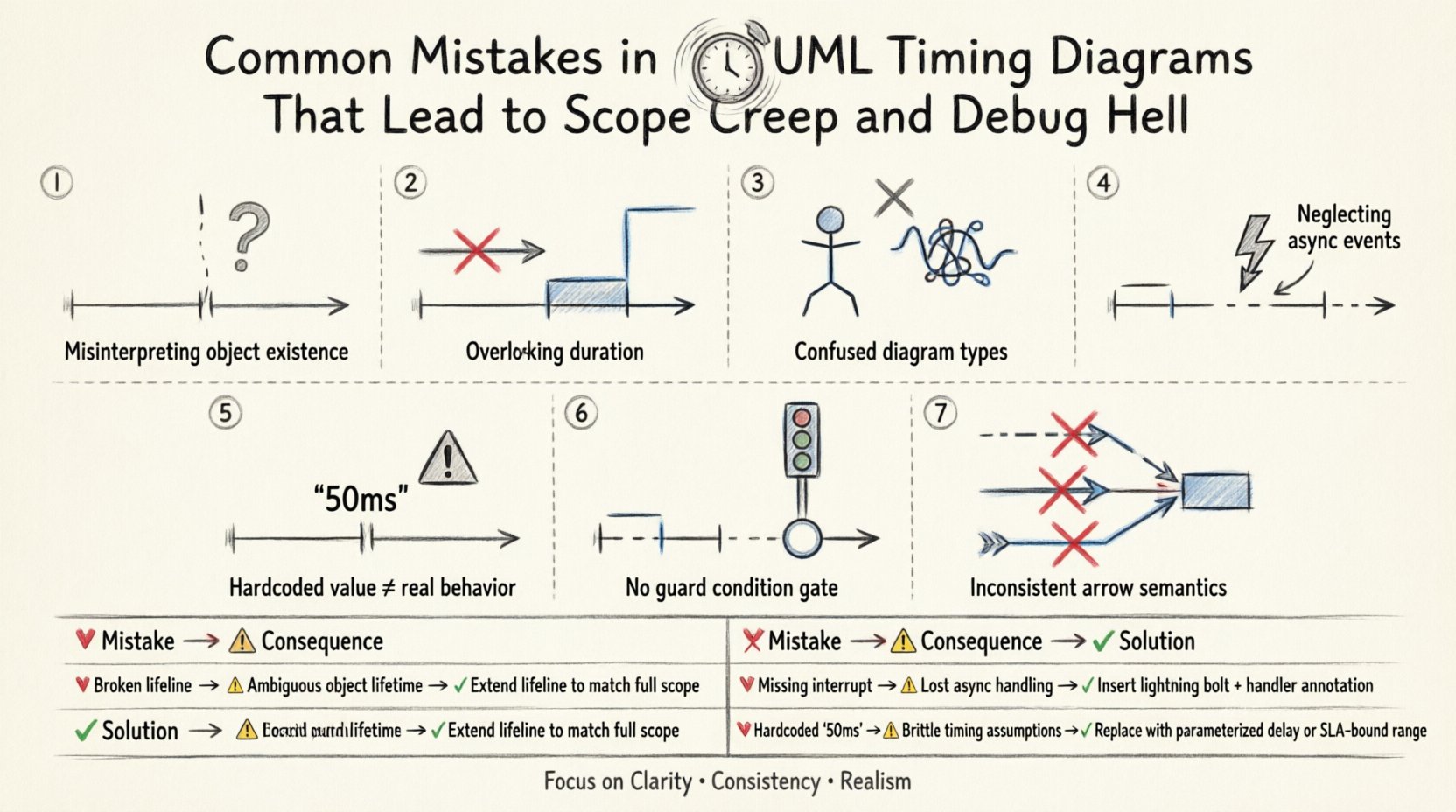

Esta guía explora los errores específicos que desvían los proyectos. Examinaremos cómo malinterpretar las líneas de vida, ignorar las duraciones de los mensajes y no documentar los cambios de estado pueden generar una cascada de problemas. Al abordar estos errores desde temprano, los equipos pueden prevenir el crecimiento de alcance y reducir el tiempo dedicado a depurar errores de tiempo esquivos.

1. Malinterpretación de las líneas de vida y la existencia de objetos 🕰️

La base de cualquier diagrama de tiempo es la línea de vida. Una línea de vida representa un objeto o componente durante un período de tiempo. Un error frecuente ocurre cuando los diseñadores no distinguen entre la creación de una instancia y su participación activa en un proceso.

- Asumiendo disponibilidad constante:Muchos diagramas implican que un componente existe y está listo para responder en cada marca de tiempo. En la realidad, los componentes pueden estar en estado de suspensión, en proceso de inicialización o experimentando contención de recursos.

- Ignorando la desactivación:Si una línea de vida permanece activa indefinidamente sin un estado final claro, sugiere que el objeto está siempre escuchando. Esto conduce a fugas de memoria o estados de hilo no manejados en la implementación.

- Confundiendo líneas de vida lógicas con físicas:Una línea de vida lógica podría representar una clase, pero una línea de vida física representa un hilo o proceso. Mezclarlas sin distinción causa errores de sincronización.

Cuando las líneas de vida no están definidas con precisión, los desarrolladores pueden asignar recursos que nunca se liberan o no manejar casos en los que un componente está temporalmente inaccesible. Esta ambigüedad obliga al equipo a añadir lógica para manejar casos extremos que no fueron anticipados en la fase de diseño, contribuyendo directamente al crecimiento de alcance.

2. Pasar por alto la duración de los mensajes y las barras de activación ⏱️

Las barras de activación indican el período durante el cual un objeto está realizando una acción. Un error crítico consiste en tratar los mensajes como eventos instantáneos. En sistemas del mundo real, el procesamiento toma tiempo. Ignorar la duración de una operación conduce a condiciones de carrera.

- Mensajes instantáneos:Dibujar una flecha de mensaje sin duración implica que el emisor recibe una respuesta inmediatamente. Si el receptor requiere un procesamiento significativo, el emisor podría experimentar un tiempo de espera o colapso.

- Faltan superposiciones:Si dos mensajes están programados para ejecutarse simultáneamente en el mismo objeto sin una cola adecuada, el sistema puede exhibir un comportamiento indefinido.

- Ignorando el bloqueo:Algunas operaciones bloquean el hilo hasta su finalización. Si el diagrama no muestra este período de bloqueo, el arquitecto podría asumir que el hilo está libre para manejar otras tareas, lo que conduce a bloqueos.

Al no modelar con precisión el ancho de las barras de activación, el equipo de implementación construye sistemas que no pueden manejar la latencia realista. Cuando surgen cuellos de botella de rendimiento, la culpa a menudo se traslada al código, cuando la causa raíz fue un diagrama que prometía una ejecución más rápida de la que el hardware podía entregar.

3. Confundir diagramas de tiempo con diagramas de secuencia 🔄

Aunque ambos diagramas muestran interacciones, cumplen propósitos diferentes. Un diagrama de secuencia se centra en el orden de los mensajes. Un diagrama de tiempo se centra en las restricciones de tiempo y los cambios de estado de los objetos. Mezclar estas responsabilidades genera confusión.

- Orden frente a tiempo:Un diagrama de secuencia muestra que el mensaje B ocurre después del mensaje A. Un diagrama de tiempo muestra que el mensaje B debe ocurrir dentro de los 50 milisegundos del mensaje A.

- Representación de estado:Los diagramas de tiempo deben mostrar explícitamente los cambios de estado (por ejemplo, una notación de máquina de estados) a lo largo de la línea de vida. Los diagramas de secuencia normalmente no se centran en este nivel de detalle.

- Paralelismo:Los diagramas de tiempo son superiores para mostrar caminos de procesamiento paralelo. Los diagramas de secuencia a menudo aplanan estas interacciones en una sola línea de tiempo, ocultando problemas de concurrencia.

Utilizar un diagrama de secuencia para lógica crítica en tiempo obliga a los desarrolladores a inferir restricciones de tiempo que nunca se establecieron explícitamente. Esta inferencia es un terreno fértil para errores. Los desarrolladores hacen suposiciones sobre la latencia y el rendimiento, y cuando esas suposiciones fallan, la depuración se convierte en una pesadilla.

4. Ignorar eventos asíncronos e interrupciones ⚡

Los sistemas rara vez son perfectamente síncronos. Los eventos externos, las interrupciones y las devoluciones de llamada asíncronas ocurren de forma impredecible. Un error común es modelar únicamente el camino feliz de forma lineal.

- Interrupciones omitidas:Si ocurre una interrupción de alta prioridad, puede preemtir una tarea de baja prioridad. Si el diagrama no muestra esta preemción, la implementación del planificador será incorrecta.

- Ignorar los tiempos límite:Cada llamada asíncrona debe tener un mecanismo de tiempo límite. No marcar el período de tiempo límite en el diagrama conduce a procesos bloqueados que consumen recursos del sistema indefinidamente.

- Cola de eventos:¿Cómo se almacenan en búfer los eventos? Si el diagrama muestra eventos que llegan más rápido de lo que pueden procesarse, el sistema debería mostrar una cola de espera. Ignorar esto conduce a pérdida de datos en producción.

Depurar problemas asíncronos es notoriamente difícil porque son no deterministas. Si el diseño no tiene en cuenta el momento de estos eventos, el código tendrá dificultades para mantener la consistencia. Esto a menudo da lugar a pruebas frágiles que pasan localmente pero fallan en entornos de producción con perfiles de carga diferentes.

5. Codificar en forma rígida las restricciones de tiempo en el diseño 📏

Uno de los errores más insidiosos es incorporar valores de tiempo específicos (por ejemplo, «50ms») directamente en el diagrama sin contexto. Esto crea un diseño frágil que no puede adaptarse a entornos cambiantes.

- Dependencia del entorno:Un retraso de 50ms podría ser aceptable en un servidor local, pero inaceptable en un dispositivo conectado con alta latencia. Codificar valores en forma rígida vincula el diseño a una infraestructura específica.

- Falta de escalabilidad:A medida que el sistema crece, las restricciones de tiempo suelen cambiar. Si el diagrama es rígido, actualizar el diseño requiere una reescritura completa de la documentación.

- Variables omitidas:En lugar de valores fijos, utilice variables o parámetros (por ejemplo, Max_Latencia). Esto permite que la implementación configure umbrales según el entorno de despliegue.

Cuando las restricciones se codifican en forma rígida, el equipo pierde flexibilidad. Si el requisito del negocio cambia para soportar una nueva región con mayor latencia, toda la arquitectura debe ser reevaluada. Un buen diseño separa la lógica de tiempo de los detalles de implementación.

6. Fallar en documentar las condiciones de protección 🚦

Los diagramas de temporización muestran a menudo un flujo de eventos, pero con frecuencia omiten las condiciones necesarias para que ocurran esos eventos. Un mensaje podría enviarse solo si se alcanza un estado específico. Sin este contexto, el receptor queda adivinando.

- Lógica implícita:Si un mensaje se envía solo cuando

error_code == 0, esto debe ser visible. Si está oculto, el desarrollador podría implementar la lógica del mensaje sin la condición de protección, causando errores. - Transiciones de estado:Los diagramas de temporización deben alinearse con los diagramas de máquinas de estado. Si el diagrama muestra que se envía un mensaje, pero la máquina de estado indica que ese estado es inalcanzable, el diseño es contradictorio.

- Lógica compleja:Las expresiones booleanas complejas deben documentarse en notas adjuntas al mensaje o a la línea de vida. Depender de modelos mentales de la lógica es insuficiente para sistemas complejos.

Cuando faltan condiciones de guardia, los desarrolladores escriben código que maneja estados que nunca deberían ocurrir. Esto agranda la base de código y aumenta el área de superficie para errores. También hace que el código sea más difícil de mantener porque la lógica para manejar excepciones está dispersa.

7. Notación y estándares inconsistentes 📝

UML es una norma, pero los equipos a menudo crean sus propias variaciones. La notación inconsistente conduce a malentendidos entre los miembros del equipo y los interesados.

- Estilos de flechas:Las líneas sólidas suelen significar llamadas síncronas, mientras que las líneas punteadas significan asíncronas. Mezclarlas confunde el modelo de ejecución.

- Notación para plazos: Algunos equipos usan corchetes, otros usan texto. La consistencia es clave para herramientas de análisis automático o generadores de documentación.

- Etiquetado: Los mensajes deben etiquetarse claramente con su propósito. Las etiquetas ambiguas como «Procesar datos» son insuficientes. Deberían ser «Validar entrada» o «Guardar registro».

La consistencia reduce la carga cognitiva del equipo. Cuando todos siguen las mismas reglas, leer un diagrama tarda segundos en lugar de minutos. Esta eficiencia es crítica al revisar diseños en busca de posibles problemas de temporización.

Errores comunes frente a buenas prácticas

La siguiente tabla resume los errores más frecuentes y sus soluciones correspondientes. Úsela como lista de verificación durante sus revisiones de diseño.

| 🔴 Error común | ⚠️ Consecuencia | ✅ Práctica correcta |

|---|---|---|

| Suponer mensajes instantáneos | Tiempo de espera agotado y condiciones de carrera | Dibuje las barras de activación con duraciones realistas |

| Ignorar interrupciones asíncronas | Bloqueos y fugas de recursos | Modelar la preemption y la cola explícitamente |

| Codificar valores específicos de milisegundos | Diseño frágil, mala escalabilidad | Use variables o parámetros para las restricciones de tiempo |

| Mezclar lógica de secuencia y temporización | Requisitos ambiguos | Use la secuencia para el orden, la temporización para las restricciones |

| Omitir condiciones de guardia | Rutas de código innecesarias | Anotar condiciones en las flechas de mensaje |

| Notación inconsistente | Malentendido por parte del equipo | Adoptar y hacer cumplir una norma general del equipo |

8. El impacto en la prueba y verificación 🧪

Un diagrama de temporización mal diseñado afecta directamente la estrategia de prueba. Si el diagrama no especifica las restricciones de temporización, los probadores no pueden escribir pruebas efectivas para esas restricciones.

- Falta de cobertura de pruebas:Sin objetivos de temporización explícitos, los probadores pueden centrarse en la corrección funcional y pasar por alto violaciones de temporización.

- Pruebas no deterministas:Si la temporización no se modela, las pruebas pueden pasar en una máquina y fallar en otra debido a diferencias de hardware.

- Problemas de integración:Las incompatibilidades de temporización entre módulos a menudo solo aparecen durante la integración. El modelado temprano detecta estos problemas antes de que se escriba el código.

Invertir tiempo en diagramas precisos tiene beneficios durante la fase de prueba. Permite crear pruebas de rendimiento que validen la arquitectura frente al diseño, y no solo frente al código.

9. Barreras de comunicación con los interesados 🗣️

Los diagramas de temporización no son solo para desarrolladores. A menudo se utilizan para comunicarse con gerentes de proyectos y clientes sobre las expectativas de rendimiento del sistema.

- Gestión de expectativas:Si el diagrama muestra un tiempo de respuesta de 1 segundo, pero la implementación tarda 5 segundos, se pierde la confianza. El diagrama debe reflejar capacidades realistas.

- Definición del alcance:Las restricciones de temporización definen el alcance. Si un cliente solicita un rendimiento en tiempo real, pero el diagrama muestra procesamiento por lotes, el alcance no coincide.

- Gestión de cambios:Cuando cambian los requisitos, el diagrama debe actualizarse de inmediato. Los diagramas desactualizados conducen a trabajo que no cumple con los nuevos requisitos.

Una documentación clara evita el crecimiento del alcance al hacer explícitos los límites del sistema. Si una característica requiere una restricción de temporización que no se modela, puede identificarse temprano como fuera de alcance.

10. El costo de depurar problemas de temporización 🐞

Depurar problemas de temporización es significativamente más costoso que depurar lógica funcional. A menudo no puedes reproducir el problema fácilmente porque depende de condiciones específicas de carga o condiciones de carrera.

- Dificultad de reproducción:Si un error ocurre solo cuando dos hilos interactúan dentro de 10 ms, reproducirlo requiere un entorno controlado.

- Requisitos de herramientas:Depurar la temporización a menudo requiere perfiles especializados o registradores, lo que añade complejidad al entorno de desarrollo.

- Riesgo en producción:Los errores de temporización a menudo aparecen bajo carga, lo que significa que podrían no detectarse hasta que el sistema esté en producción.

Al prevenir estos errores en la fase de diseño, los equipos ahorran recursos sustanciales. El costo de corregir un error en un diagrama es insignificante comparado con el costo de corregir un sistema desplegado con vulnerabilidades de temporización.

Consideraciones finales sobre la precisión del tiempo 🎯

Crear diagramas de tiempo UML precisos requiere disciplina y atención al detalle. No basta con dibujar líneas y flechas; uno debe comprender el comportamiento subyacente del sistema. Al evitar los errores comunes descritos en esta guía, los equipos pueden construir sistemas que sean robustos, mantenibles y eficientes.

Recuerda que el diagrama es un contrato entre el diseño y la implementación. Si el contrato es vago, la implementación sufrirá. Trata los diagramas de tiempo con la misma rigurosidad que las especificaciones funcionales. Este enfoque ahorrará a tu equipo los problemas del crecimiento de alcance y la frustración del infierno de depuración.

Enfócate en la claridad, la consistencia y la realismo. Estos tres pilares garantizarán que tus diagramas de tiempo cumplan su propósito de manera efectiva, guiando el proceso de desarrollo hacia el éxito sin desvíos innecesarios.