सॉफ्टवेयर आर्किटेक्चर घटकों के बीच सटीक संचार पर बहुत अधिक निर्भर करता है। समय-संवेदनशील बातचीत के साथ निपटते समय, UML समय आरेख एक अनिवार्य उपकरण बन जाता है। हालांकि, बहुत से � ingineers इन आरेखों को बस एक बाद की चिंता या अनुक्रम आरेखों के साथ भ्रमित करते हैं। इस भ्रम के कारण अस्पष्ट आवश्यकताएं, अनियंत्रित कोड और समय-संबंधी बगों से भरा विकास चक्र बनता है। समय सीमाओं के बारे में बातचीत करना वैकल्पिक नहीं है; यह लचीली डिजाइन के लिए एक आवश्यकता है।

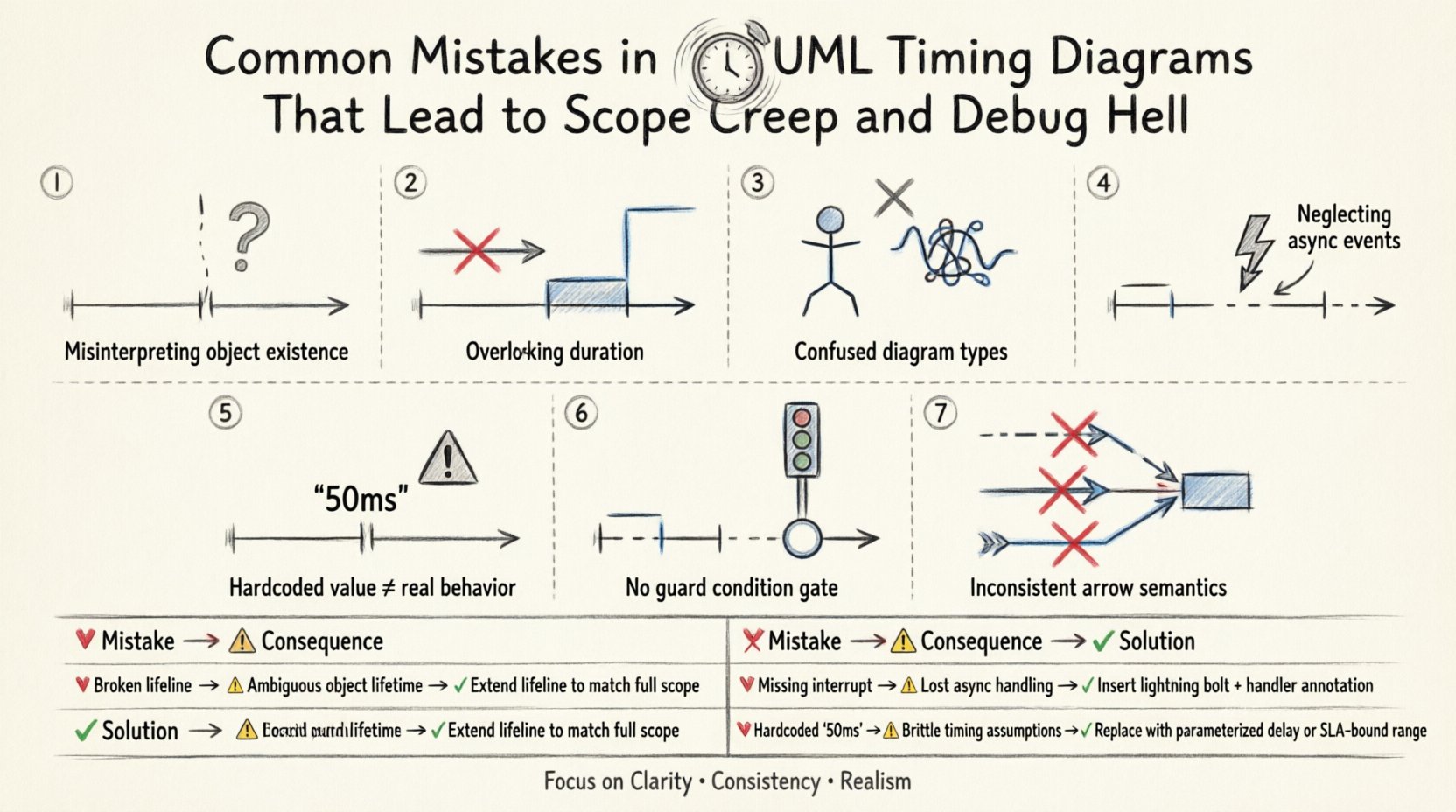

यह मार्गदर्शिका प्रोजेक्ट को विफल करने वाली विशिष्ट खामियों का अध्ययन करती है। हम देखेंगे कि लाइफलाइन के गलत अर्थ लगाना, संदेश की अवधि को नजरअंदाज करना और राज्य परिवर्तन को दर्ज न करना कैसे एक बार-बार उत्पन्न होने वाली समस्याओं का श्रृंखला बना सकता है। इन गलतियों को जल्दी से दूर करने से टीमें स्कोप क्रीप को रोक सकती हैं और भटकते हुए समय संबंधी त्रुटियों के निरीक्षण में लगने वाला समय कम कर सकती हैं।

1. लाइफलाइन और ऑब्जेक्ट उपस्थिति के गलत अर्थ लगाना 🕰️

किसी भी समय आरेख का आधार लाइफलाइन है। एक लाइफलाइन किसी ऑब्जेक्ट या घटक का समय के दौरान प्रतिनिधित्व करती है। डिजाइनरों द्वारा एक उदाहरण के निर्माण और एक प्रक्रिया में सक्रिय भागीदारी के बीच अंतर न करने की एक बार-बार गलती होती है।

- निरंतर उपलब्धता मानना:बहुत से आरेख इस बात का इशारा करते हैं कि एक घटक हर समय टिकट पर मौजूद है और प्रतिक्रिया करने के लिए तैयार है। वास्तविकता में, घटक स्लीप स्टेट में हो सकते हैं, प्रारंभीकरण के दौरान हो सकते हैं या संसाधन प्रतिस्पर्धा का सामना कर सकते हैं।

- डीएक्टिवेशन को नजरअंदाज करना:यदि एक लाइफलाइन बिना स्पष्ट अंत स्थिति के अनंतकाल तक सक्रिय रहती है, तो यह इंगित करता है कि ऑब्जेक्ट हमेशा सुन रहा है। इससे इम्प्लीमेंटेशन में मेमोरी लीक या अनसंभाले थ्रेड स्टेट्स की समस्या उत्पन्न होती है।

- तार्किक बनाम भौतिक लाइफलाइन के बीच भ्रम:एक तार्किक लाइफलाइन एक क्लास का प्रतिनिधित्व कर सकती है, लेकिन एक भौतिक लाइफलाइन एक थ्रेड या प्रक्रिया का प्रतिनिधित्व करती है। इन्हें अंतर बिना मिलाने से सिंक्रोनाइजेशन त्रुटियाँ उत्पन्न होती हैं।

जब लाइफलाइन को सही तरीके से परिभाषित नहीं किया जाता है, तो डेवलपर्स संसाधनों को आवंटित कर सकते हैं जिन्हें कभी रिलीज नहीं किया जाता है या ऐसे मामलों को संभालने में विफल रहते हैं जहां एक घटक अस्थायी रूप से उपलब्ध नहीं होता है। इस अस्पष्टता के कारण टीम को डिजाइन चरण में अनुमानित नहीं किए गए एज केस को संभालने के लिए लॉजिक जोड़ने के लिए मजबूर किया जाता है, जो स्कोप क्रीप के सीधे योगदान करता है।

2. संदेश की अवधि और एक्टिवेशन बार को नजरअंदाज करना ⏱️

एक्टिवेशन बार उस समय के अंतराल को इंगित करते हैं जब एक ऑब्जेक्ट किसी क्रिया को कर रहा होता है। एक महत्वपूर्ण गलती यह है कि संदेशों को तुरंत घटनाओं के रूप में लिया जाता है। वास्तविक दुनिया के प्रणालियों में, प्रोसेसिंग को समय लगता है। किसी ऑपरेशन की अवधि को नजरअंदाज करने से रेस कंडीशन उत्पन्न होती है।

- तुरंत संदेश:कोई अवधि नहीं वाले संदेश तीर को बनाने से इस बात का अर्थ निकलता है कि भेजने वाला तुरंत प्रतिक्रिया प्राप्त करता है। यदि प्राप्तकर्ता को महत्वपूर्ण प्रोसेसिंग की आवश्यकता है, तो भेजने वाला टाइमआउट हो सकता है या क्रैश हो सकता है।

- ओवरलैप की अनदेखी:यदि दो संदेश एक ही ऑब्जेक्ट पर एक साथ निष्पादित करने के लिए योजना बनाए गए हैं और उचित कतार नहीं बनाई गई है, तो प्रणाली अपरिभाषित व्यवहार दिखा सकती है।

- ब्लॉकिंग को नजरअंदाज करना:कुछ ऑपरेशन थ्रेड को पूरा होने तक ब्लॉक कर देते हैं। यदि आरेख इस ब्लॉकिंग अवधि को नहीं दिखाता है, तो आर्किटेक्ट यह मान सकता है कि थ्रेड अन्य कार्यों को संभालने के लिए मुक्त है, जिससे डेडलॉक उत्पन्न होते हैं।

एक्टिवेशन बार की चौड़ाई को सही तरीके से मॉडल न करने से इम्प्लीमेंटेशन टीम ऐसी प्रणालियाँ बनाती है जो वास्तविक लेटेंसी को हैंडल नहीं कर सकती हैं। जब प्रदर्शन की समस्या उत्पन्न होती है, तो आरोप अक्सर कोड पर डाल दिया जाता है, जबकि मूल कारण एक आरेख था जो हार्डवेयर द्वारा देय तेजी से निष्पादन की गारंटी देता था।

3. समय आरेखों को अनुक्रम आरेखों के साथ भ्रमित करना 🔄

जबकि दोनों आरेख बातचीत को दिखाते हैं, लेकिन उनके उद्देश्य अलग-अलग होते हैं। एक अनुक्रम आरेख संदेशों के क्रम पर ध्यान केंद्रित करता है। एक समय आरेख ऑब्जेक्टों की समय सीमाओं और राज्य परिवर्तन पर ध्यान केंद्रित करता है। इन जिम्मेदारियों को मिलाने से भ्रम उत्पन्न होता है।

- क्रम बनाम समय:एक अनुक्रम आरेख दिखाता है कि संदेश B संदेश A के बाद होता है। एक समय आरेख दिखाता है कि संदेश B को संदेश A के 50 मिलीसेकंड के भीतर होना चाहिए।

- राज्य प्रतिनिधित्व:समय आरेखों में लाइफलाइन के साथ राज्य परिवर्तनों को स्पष्ट रूप से दिखाना चाहिए (उदाहरण के लिए, राज्य मशीन नोटेशन)। अनुक्रम आरेख आमतौर पर इस स्तर की विस्तार से नहीं ध्यान केंद्रित करते हैं।

- समानांतरता:समय आरेख समानांतर प्रोसेसिंग पथों को दिखाने के लिए बेहतर हैं। अनुक्रम आरेख अक्सर इन बातचीतों को एकल समय रेखा में समेट देते हैं, जिससे समानांतरता की समस्याएं छिप जाती हैं।

समय-महत्वपूर्ण तर्क के लिए अनुक्रम आरेख का उपयोग करने से डेवलपर्स को उन समय सीमाओं को निष्कर्ष निकालने के लिए मजबूर किया जाता है जो कभी स्पष्ट रूप से नहीं बताई गई थीं। इस निष्कर्ष निकालना बगों के लिए एक उपजाऊ जगह है। डेवलपर्स लेटेंसी और थ्रूपुट के बारे में धारणाएं बनाते हैं, और जब ये धारणाएं विफल होती हैं, तो डीबगिंग एक नरक बन जाती है।

4. असिंक्रोनस घटनाओं और इंटरप्ट्स की उपेक्षा करना ⚡

प्रणालियाँ लगभग कभी भी पूरी तरह से समकालिक नहीं होती हैं। बाहरी घटनाएँ, इंटरप्ट्स और असिंक्रोनस कॉलबैक अप्रत्याशित रूप से घटित होते हैं। एक सामान्य गलती यह है कि एक रेखीय तरीके से केवल सफल मार्ग का मॉडलिंग करना।

- इंटरप्ट्स की लापरवाही: यदि उच्च प्राथमिकता वाला इंटरप्ट होता है, तो वह निम्न प्राथमिकता वाले कार्य को प्रतिस्थापित कर सकता है। यदि आरेख में इस प्रतिस्थापन को नहीं दिखाया गया है, तो स्केड्यूलर कार्यान्वयन गलत होगा।

- टाइमआउट की उपेक्षा करना: प्रत्येक असिंक्रोनस कॉल में टाइमआउट तंत्र होना चाहिए। आरेख में टाइमआउट अवधि को चिह्नित करने की विफलता से ऐसी बाधित प्रक्रियाएँ बनती हैं जो अनंतकाल तक सिस्टम संसाधनों का उपयोग करती हैं।

- घटना कतारबद्धता: घटनाओं को कैसे बफर किया जाता है? यदि आरेख घटनाओं के प्रक्रिया करने से तेजी से आने को दिखाता है, तो प्रणाली में बैकलॉग दिखाना चाहिए। इसकी उपेक्षा करने से उत्पादन में डेटा का नुकसान होता है।

असिंक्रोनस समस्याओं का निराकरण बहुत मुश्किल होता है क्योंकि वे अनिश्चित होती हैं। यदि डिज़ाइन इन घटनाओं के समय को ध्यान में नहीं रखता है, तो कोड संस्थिरता बनाए रखने में कठिनाई महसूस करेगा। इसके लिए अक्सर अस्थिर परीक्षण होते हैं जो स्थानीय रूप से सफल होते हैं लेकिन अलग लोड प्रोफाइल वाले उत्पादन वातावरण में विफल होते हैं।

5. डिज़ाइन में समय सीमा प्रतिबंधों को कड़ाई से निर्धारित करना 📏

सबसे घातक गलतियों में से एक यह है कि संदर्भ के बिना विशिष्ट समय मानों (उदाहरण के लिए, “50ms”) को सीधे आरेख में एम्बेड करना। इससे एक नाजुक डिज़ाइन बनता है जो बदलते वातावरण में अनुकूलित नहीं हो सकता।

- वातावरण पर निर्भरता: 50ms का देरी स्थानीय सर्वर पर स्वीकार्य हो सकता है, लेकिन उच्च लेटेंसी वाले नेटवर्क युक्त उपकरण पर अस्वीकार्य हो सकता है। मानों को कड़ाई से निर्धारित करने से डिज़ाइन एक विशिष्ट इंफ्रास्ट्रक्चर से जुड़ जाता है।

- स्केलेबिलिटी की कमी: जैसे-जैसे प्रणाली का पैमाना बढ़ता है, समय सीमा प्रतिबंध अक्सर बदल जाते हैं। यदि आरेख कठोर है, तो डिज़ाइन को अपडेट करने के लिए दस्तावेज़ीकरण को पूरी तरह से फिर से लिखने की आवश्यकता होती है।

- चर की लापरवाही: निश्चित मानों के बजाय, चर या पैरामीटर का उपयोग करें (उदाहरण के लिए, Max_Latency)। इससे कार्यान्वयन को डेप्लॉयमेंट वातावरण के आधार पर अवरोध सेट करने की अनुमति मिलती है।

जब प्रतिबंध कड़ाई से निर्धारित किए जाते हैं, तो टीम को लचीलापन खो देती है। यदि व्यावसायिक आवश्यकता उच्च लेटेंसी वाले नए क्षेत्र का समर्थन करने के लिए बदलती है, तो पूरी आर्किटेक्चर को फिर से मूल्यांकन करना होगा। अच्छा डिज़ाइन समय तर्क को कार्यान्वयन विवरण से अलग करता है।

6. गार्ड शर्तों को दस्तावेज़ीकरण करने में विफलता 🚦

समय आरेख अक्सर घटनाओं के प्रवाह को दिखाते हैं, लेकिन अक्सर उन घटनाओं के घटित होने के लिए आवश्यक शर्तों को छोड़ देते हैं। एक संदेश केवल तभी भेजा जा सकता है जब एक विशिष्ट स्थिति प्राप्त हो। इस संदर्भ के बिना, प्राप्तकर्ता अनुमान लगाने में फंस जाता है।

- अप्रकट तर्क: यदि संदेश केवल तभी भेजा जाता है जब

error_code == 0, तो इसे दिखाया जाना चाहिए। यदि यह छिपा है, तो डेवलपर संदेश तर्क को गार्ड के बिना लागू कर सकता है, जिससे त्रुटियाँ हो सकती हैं। - राज्य संक्रमण: समय आरेख को राज्य मशीन आरेख के साथ मेल बैठाना चाहिए। यदि आरेख एक संदेश भेजे जाने को दिखाता है, लेकिन राज्य मशीन कहती है कि वह राज्य प्राप्त नहीं किया जा सकता, तो डिज़ाइन विरोधाभासी है।

- जटिल तर्क: जटिल बूलियन व्यंजकों को संदेश या लाइफलाइन से जुड़े नोट्स में दस्तावेज़ीकृत किया जाना चाहिए। जटिल प्रणालियों के लिए तर्क के मानसिक मॉडल पर भरोसा करना पर्याप्त नहीं है।

जब गार्ड शर्तें गायब होती हैं, तो विकासकर्ता ऐसा कोड लिखते हैं जो उन स्थितियों को हैंडल करता है जो कभी नहीं होनी चाहिए। इससे कोडबेस बढ़ जाता है और बग्स के लिए सतह क्षेत्र बढ़ जाता है। इसके अलावा कोड को बनाए रखना मुश्किल हो जाता है क्योंकि अपवादों को हैंडल करने की तर्कविधि फैली होती है।

7. असंगत नोटेशन और मानकों 📝

UML एक मानक है, लेकिन टीमें अक्सर अपने स्वयं के विकल्प बनाती हैं। असंगत नोटेशन के कारण टीम सदस्यों और हितधारकों के बीच गलत व्याख्या होती है।

- तीर के शैली:ठोस रेखाएं आमतौर पर सिंक्रोनस कॉल्स का अर्थ होती हैं, जबकि डैश्ड रेखाएं एसिंक्रोनस का अर्थ होती हैं। इन्हें मिलाने से निष्पादन मॉडल में भ्रम पैदा होता है।

- समय सीमा के लिए नोटेशन: कुछ टीमें कोष्ठक का उपयोग करती हैं, जबकि अन्य टेक्स्ट का उपयोग करती हैं। स्वचालित पार्सिंग टूल्स या दस्तावेज़ उत्पादकों के लिए संगतता महत्वपूर्ण है।

- लेबलिंग: संदेशों को उनके उद्देश्य के साथ स्पष्ट रूप से लेबल किया जाना चाहिए। “डेटा प्रोसेस करें” जैसे अस्पष्ट लेबल पर्याप्त नहीं हैं। उन्हें “इनपुट की पुष्टि करें” या “रिकॉर्ड सहेजें” होना चाहिए।

संगतता टीम पर मानसिक भार को कम करती है। जब सभी एक ही नियमों का पालन करते हैं, तो एक आरेख को पढ़ने में सेकंड की बजाय मिनट लगते हैं। जब संभावित समय संबंधी समस्याओं के लिए डिज़ाइन की समीक्षा करते हैं, तो यह दक्षता महत्वपूर्ण है।

आम गलतियाँ बनाम सही व्यवहार

निम्नलिखित तालिका सबसे आम त्रुटियों और उनके संबंधित समाधानों का सारांश देती है। अपनी डिज़ाइन समीक्षा के दौरान इसका उपयोग चेकलिस्ट के रूप में करें।

| 🔴 आम गलती | ⚠️ परिणाम | ✅ सही व्यवहार |

|---|---|---|

| तत्काल संदेशों की धारणा करना | टाइमआउट और रेस कंडीशन्स | वास्तविक अवधि के साथ एक्टिवेशन बार बनाएं |

| असिंक्रोनस इंटरप्ट्स को नजरअंदाज करना | डेडलॉक्स और संसाधन लीक्स | प्रीएम्प्शन और क्यूइंग को स्पष्ट रूप से मॉडल करें |

| विशिष्ट मिलीसेकंड मानों को हार्डकोड करना | नाजुक डिज़ाइन, खराब स्केलेबिलिटी | समय सीमा के लिए चर या पैरामीटर का उपयोग करें |

| क्रम और समय संबंधी तर्क को मिलाना | अस्पष्ट आवश्यकताएं | क्रम के लिए क्रम का उपयोग करें, सीमाओं के लिए समय का उपयोग करें |

| गार्ड शर्तों को छोड़ना | अनावश्यक कोड पाथ | संदेश तीरों पर शर्तों को टिप्पणी करें |

| असंगत संकेतन | टीम द्वारा गलत व्याख्या | एक टीम-व्यापी मानक को अपनाएं और लागू करें |

8. परीक्षण और सत्यापन पर प्रभाव 🧪

एक खराब डिज़ाइन किए गए समय आरेख का परीक्षण रणनीति पर सीधा प्रभाव पड़ता है। यदि आरेख समय सीमाओं को निर्दिष्ट नहीं करता है, तो परीक्षक उन सीमाओं के लिए प्रभावी परीक्षण नहीं लिख सकते।

- परीक्षण कवरेज की कमी: स्पष्ट समय लक्ष्यों के बिना, परीक्षक कार्यात्मक सही ढंग से ध्यान केंद्रित कर सकते हैं और समय उल्लंघन को छोड़ सकते हैं।

- अनिर्णायक परीक्षण: यदि समय का मॉडलिंग नहीं किया गया है, तो परीक्षण एक मशीन पर सफल हो सकते हैं और दूसरे में विफल हो सकते हैं क्योंकि हार्डवेयर में अंतर होता है।

- एकीकरण की समस्याएं: मॉड्यूल के बीच समय के असंगत होने की समस्या अक्सर केवल एकीकरण के दौरान उभरती है। जल्दी मॉडलिंग के द्वारा इन समस्याओं को कोड लिखे जाने से पहले पकड़ा जा सकता है।

सटीक आरेखों में समय निवेश करना परीक्षण चरण में लाभ देता है। इससे विकास डिज़ाइन के विरुद्ध आर्किटेक्चर की पुष्टि करने वाले प्रदर्शन परीक्षण बनाने की अनुमति मिलती है, केवल कोड के बजाय।

9. हितधारकों के साथ संचार की बाधाएं 🗣️

समय आरेख केवल डेवलपर्स के लिए नहीं होते हैं। वे अक्सर प्रोजेक्ट मैनेजर्स और ग्राहकों के साथ सिस्टम प्रदर्शन की अपेक्षाओं के बारे में संचार के लिए उपयोग किए जाते हैं।

- अपेक्षाओं का प्रबंधन: यदि आरेख 1 सेकंड के प्रतिक्रिया समय को दिखाता है, लेकिन कार्यान्वयन में 5 सेकंड लगते हैं, तो विश्वास कमजोर हो जाता है। आरेख में वास्तविक क्षमताओं को दर्शाना चाहिए।

- सीमा निर्धारण: समय सीमाएं सीमा को परिभाषित करती हैं। यदि ग्राहक रियल-टाइम प्रदर्शन मांगता है लेकिन आरेख बैच प्रोसेसिंग दिखाता है, तो सीमा असंगत हो जाती है।

- परिवर्तन प्रबंधन: जब आवश्यकताएं बदलती हैं, तो आरेख को तुरंत अपडेट किया जाना चाहिए। अप्रचलित आरेख उस कार्य को बनाते हैं जो नए आवश्यकताओं को पूरा नहीं करता है।

स्पष्ट दस्तावेज़ीकरण सिस्टम की सीमाओं को स्पष्ट करके सीमा विस्तार को रोकता है। यदि किसी फीचर के लिए एक समय सीमा की आवश्यकता है जिसका मॉडलिंग नहीं किया गया है, तो इसे जल्दी ही सीमा से बाहर बताया जा सकता है।

10. समय संबंधी समस्याओं के डीबग की लागत 🐞

समय संबंधी समस्याओं के डीबग करना कार्यात्मक तर्क के डीबग करने की तुलना में काफी अधिक महंगा होता है। आप अक्सर समस्या को आसानी से पुनर्निर्मित नहीं कर पाते क्योंकि यह विशिष्ट लोड की स्थितियों या रेस कंडीशन पर निर्भर करती है।

- पुनर्निर्माण कठिनाई: यदि एक बग केवल तब उत्पन्न होता है जब दो थ्रेड 10 मिलीसेकंड के भीतर बातचीत करते हैं, तो इसके पुनर्निर्माण के लिए नियंत्रित वातावरण की आवश्यकता होती है।

- उपकरण आवश्यकताएं: समय संबंधी डीबग करने के लिए अक्सर विशेषज्ञ प्रोफाइलर या लॉगर की आवश्यकता होती है, जिससे विकास वातावरण में जटिलता बढ़ जाती है।

- उत्पादन जोखिम: समय संबंधी बग अक्सर लोड के तहत दिखाई देते हैं, जिसका अर्थ है कि वे सिस्टम लाइव होने तक पकड़े नहीं जा सकते।

डिज़ाइन चरण में इन गलतियों को रोककर टीमें महत्वपूर्ण संसाधनों की बचत करती हैं। समय संबंधी दोषों वाले डिज़ाइन के त्रुटि को ठीक करने की लागत डिप्लॉय किए गए सिस्टम के त्रुटि को ठीक करने की लागत की तुलना में नगण्य होती है।

समय सटीकता पर अंतिम विचार 🎯

सटीक UML समय आरेख बनाने के लिए अनुशासन और विस्तार से ध्यान देने की आवश्यकता होती है। केवल रेखाएं और तीर खींचना पर्याप्त नहीं है; एक को सिस्टम के आधारभूत व्यवहार को समझना चाहिए। इस गाइड में बताए गए सामान्य त्रुटियों से बचकर, टीमें ऐसे सिस्टम बना सकती हैं जो टिकाऊ, रखरखाव योग्य और प्रदर्शनकारी हों।

याद रखें कि आरेख डिजाइन और कार्यान्वयन के बीच एक संविदा है। यदि संविदा धुंधली है, तो कार्यान्वयन पीड़ा झेलेगा। समय आरेखों के प्रति फंक्शनल विनिर्देशों के समान अनुशासन का पालन करें। इस दृष्टिकोण से आपकी टीम को स्कोप क्रीप और डिबग हेल की तकलीफ से बचाया जा सकता है।

स्पष्टता, सांस्कृतिक स्थिरता और वास्तविकता पर ध्यान केंद्रित करें। इन तीनों स्तंभों से यह सुनिश्चित होगा कि आपके समय आरेख अपने उद्देश्य को प्रभावी ढंग से पूरा करेंगे, अनावश्यक विचलनों के बिना विकास प्रक्रिया को सफलता की ओर अग्रसर करेंगे।