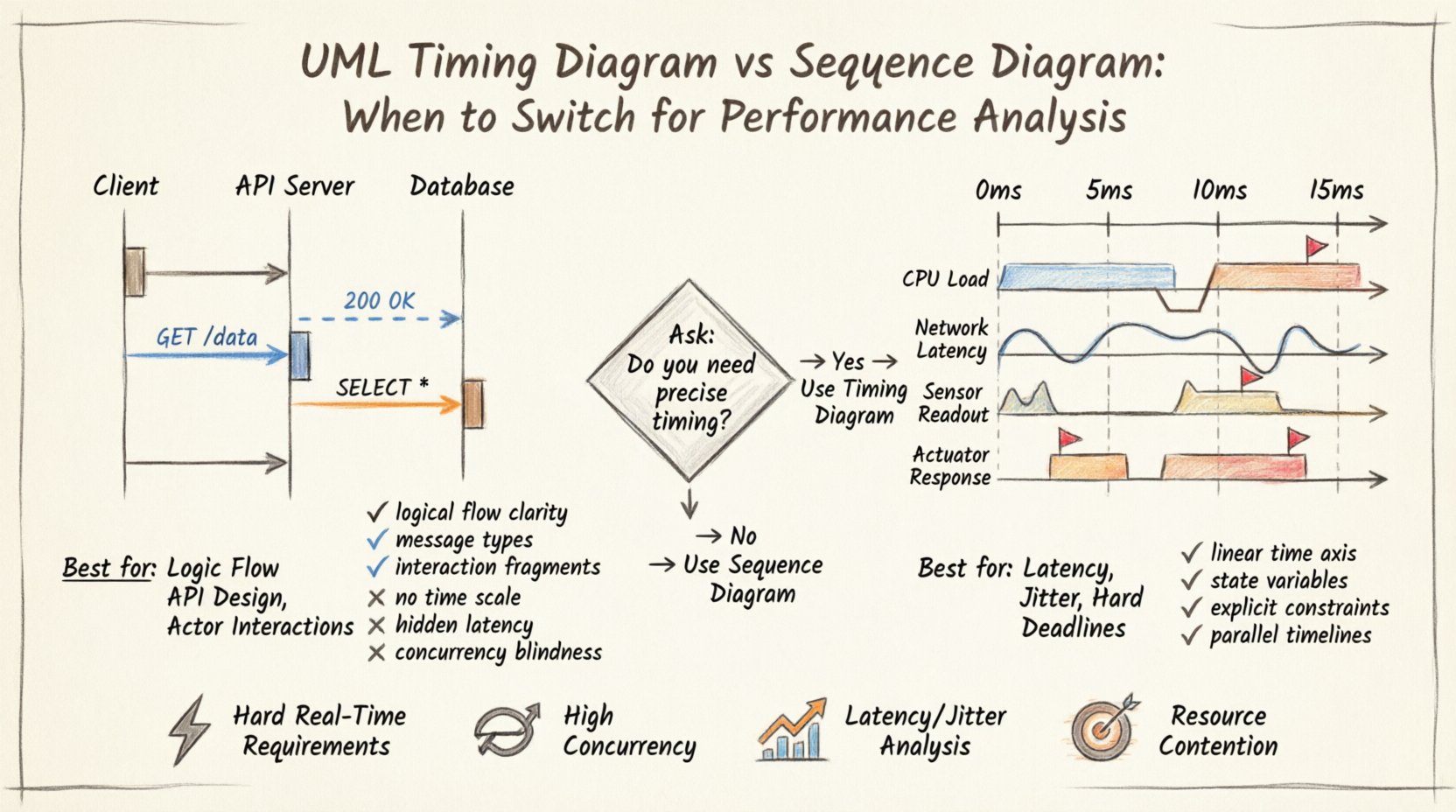

Concevoir des systèmes à haute performance exige une précision. Lors de la modélisation des interactions au sein d’architectures logicielles complexes, le choix du type de diagramme détermine la clarté de l’analyse. Le dilemme réside souvent entre le diagramme de séquence UML et le diagramme de timing UML. Bien que les diagrammes de séquence excellent à illustrer le flux logique, les diagrammes de timing offrent un contrôle fin sur les contraintes temporelles. Comprendre cette distinction est essentiel pour les ingénieurs chargés de l’optimisation de la latence, de la vérification des systèmes en temps réel et de la gestion de la concurrence.

Ce guide explore les subtilités techniques du passage des modèles de séquence aux modèles de timing. Il détaille quand la fidélité temporelle prime sur la logique d’interaction, ainsi que la manière de modéliser efficacement les métriques de performance sans dépendre d’outils propriétaires. Nous examinerons les différences structurelles, les cas d’utilisation spécifiques et les implications de modélisation pour la fiabilité du système.

Comprendre les diagrammes de séquence dans des contextes de performance ⏱️

Les diagrammes de séquence sont la norme de l’industrie pour modéliser les interactions entre objets au fil du temps. Ils se concentrent sur l’ordre des messages échangés entre les lignes de vie. Lors d’une revue de performance typique, les ingénieurs utilisent ces diagrammes pour suivre le parcours d’une requête à travers un système.

Forces de la modélisation de séquence

- Clarté du flux logique : Ils montrent clairement quel composant appelle quel autre, ce qui rend le flux de contrôle facile à comprendre.

- Types de messages : Ils distinguent visuellement les appels synchrones, les signaux asynchrones et les messages de retour.

- Fragments d’interaction : Ils supportent

alt,opt, etloopdes fragments pour modéliser la logique conditionnelle et les itérations. - Représentation des acteurs : Ils sont excellents pour montrer les déclencheurs externes, tels que des utilisateurs ou des systèmes, qui initient des processus.

Limites pour l’analyse des performances

Malgré leur popularité, les diagrammes de séquence présentent des limites intrinsèques lorsqu’ils sont utilisés pour une analyse des performances rigoureuse. L’axe temporel dans un diagramme de séquence est relatif, pas absolu. Il suggère une séquence, mais ne quantifie pas strictement la durée.

- Absence d’échelle temporelle : Il n’y a pas d’axe temporel horizontal. La distance entre les messages est arbitraire et ne représente pas de millisecondes ou de secondes.

- Latence masquée : Bien que les barres d’activation montrent la durée, elles ne permettent pas facilement de représenter des événements superposés sur la même ligne de vie, sauf si le diagramme devient encombré.

- Aveuglement face à la concurrence : Modéliser des chemins d’exécution parallèles est difficile. Les activations superposées peuvent suggérer une concurrence, mais les relations temporelles exactes sont difficiles à définir.

- Complexité des contraintes : L’ajout de contraintes temporelles (par exemple, « la réponse doit être inférieure à 50 ms ») nécessite des notes textuelles, souvent négligées lors des revues visuelles.

Lorsque les exigences de performance deviennent strictes, comme dans les systèmes embarqués ou les plateformes de trading à haute fréquence, l’ambiguïté du diagramme de séquence devient un fardeau. Les ingénieurs doivent savoir non seulement ce qui se produit, mais aussi exactement quand cela se produit par rapport à l’horloge.

Le cas pour les diagrammes de temporisation 📊

Le diagramme de temporisation UML offre une vue spécialisée où l’axe horizontal représente le temps. Ce déplacement de l’ordre des interactions vers la progression temporelle permet une modélisation précise des changements d’état et des échéances.

Fonctionnalités fondamentales pour les performances

- Axe du temps linéaire : Une échelle définie (par exemple, microsecondes, millisecondes) permet une mesure directe des intervalles.

- Variables d’état : Les diagrammes peuvent suivre l’état de variables spécifiques (par exemple, `cpu_load`, `queue_depth`) au fil du temps, et non seulement l’activation des objets.

- Contraintes de temporisation : Des annotations explicites définissent les durées minimales, maximales et exactes pour les transitions.

- Parallélisme : Plusieurs changements d’état peuvent être visualisés simultanément sur des lignes de vie différentes, rendant la concurrence visible.

Visualisation du comportement en temps réel

Les systèmes temps réel fonctionnent souvent sous des délais stricts ou souples. Un diagramme de temporisation permet aux ingénieurs de cartographier directement ces délais contre la chronologie d’exécution. Si une tâche doit être terminée en moins de 10 ms, le diagramme peut afficher l’heure de début, la durée de la tâche et le repère de délai.

Cette visualisation aide à identifier les goulets d’étranglement que les diagrammes de séquence pourraient cacher. Par exemple, une séquence de trois appels peut sembler séquentielle dans un diagramme de séquence. Dans un diagramme de temporisation, si deux appels ont lieu en parallèle sur des cœurs différents, la durée totale est réduite. Le diagramme de temporisation capture explicitement cette optimisation.

Analyse comparative : séquence vs. temporisation 📋

Pour comprendre les compromis, nous pouvons comparer les deux approches de modélisation selon plusieurs dimensions. Le tableau suivant décrit les différences structurelles et fonctionnelles.

| Fonctionnalité | Diagramme de séquence | Diagramme de temporisation |

|---|---|---|

| Objectif principal | Ordre des interactions | Durée des états |

| Représentation du temps | Relative / implicite | Échelle absolue / explicite |

| Lignes de vie | Objets / composants | Objets / variables / horloges |

| Visibilité de l’état | Barres d’activation | Invariants d’état / Valeurs des signaux |

| Concurrence | Barres chevauchantes | Chronologies parallèles |

| Meilleur cas d’utilisation | Flux logique / Conception d’API | Latence / Jitter / Délais |

| Complexité | Faible à moyenne | Moyenne à élevée |

Comme le montre le tableau, le choix dépend de la question spécifique posée. Si la question est « Le composant A appelle-t-il le composant B avant C ? », utilisez Sequence. Si la question est « Le composant A se termine-t-il avant le délai à 500 ms ? », utilisez Timing.

Cadre décisionnel : Quand passer 🔄

Passer d’une focalisation Sequence à une focalisation Timing n’est pas une décision binaire, mais une évolution fondée sur les exigences du système. Voici des scénarios spécifiques qui nécessitent un changement.

1. Exigences temps réel strict

Les systèmes qui doivent répondre dans un délai garanti (par exemple, les systèmes de freinage automobiles, les dispositifs médicaux) nécessitent des diagrammes de timing. Les diagrammes de séquence ne peuvent pas imposer les limites temporelles requises pour la certification. Le diagramme de timing permet la définition de contrainteTempséléments qui vérifient que le système respecte les normes de sécurité.

2. Environnements à haute concurrence

Dans les systèmes multithreadés ou distribués, l’ordre des événements peut varier, mais la relation temporelle doit rester cohérente. Un diagramme de timing peut montrer que, bien que le thread A et le thread B s’exécutent de manière concurrente, le thread A ne doit pas dépasser une durée spécifique avant que le thread B ne puisse continuer. Les diagrammes de séquence supposent souvent un ordre strict qui n’existe pas dans les architectures parallèles réelles.

3. Analyse de la latence et du jitter

Le jitter est la variation de la latence au fil du temps. Les diagrammes de séquence montrent un seul chemin. Les diagrammes de timing peuvent montrer plusieurs chemins avec des durées variables pour représenter le jitter. Si l’analyse des performances nécessite de comprendre la variation du temps de réponse (par exemple, la latence au 95e percentile), le diagramme de timing est l’outil approprié.

4. Modélisation de la contention des ressources

Lors de la modélisation de la contention des ressources, telles que l’utilisation du CPU ou la bande passante mémoire, les diagrammes de timing sont supérieurs. Ils peuvent afficher des variables d’état représentant la disponibilité des ressources. Les ingénieurs peuvent visualiser quand une ressource est occupée ou inactif, ce qui permet une meilleure planification de la capacité.

Modélisation des métriques de performance : approfondissement 📏

Une fois le passage aux diagrammes de timing effectué, l’attention se concentre sur des métriques spécifiques. Ces métriques doivent être modélisées avec précision pour garantir que le diagramme reflète la réalité.

Latence

La latence est le temps total allant de l’initiation de la requête à la complétion de la réponse. Dans un diagramme de timing, il s’agit de l’intervalle entre l’événement de déclenchement sur la première ligne de vie et l’événement de retour sur la dernière ligne de vie. Pour le modéliser :

- Marquez l’heure de début de l’événement de déclenchement.

- Marquez l’heure de fin de l’événement de réponse final.

- Utilisez une annotation de contrainte pour définir l’intervalle maximal autorisé.

Débit

Le débit mesure le nombre d’événements traités par unité de temps. La modélisation du débit dans un diagramme de temporisation implique des motifs répétés. Utilisez des fragments de boucle ou des marqueurs de répétition pour indiquer un flux constant de requêtes. La densité des événements le long de l’axe temporel représente visuellement le débit.

Délais et temporisations

Les délais sont cruciaux dans la modélisation des performances. Un diagramme de temporisation peut inclure une ligne verticale pointillée représentant un délai. Si un état de processus s’étend au-delà de cette ligne, cela indique une violation. Ce repère visuel est plus immédiat que la lecture d’une contrainte textuelle dans un diagramme de séquence.

Jitter et variance

Le jitter est représenté par l’incohérence des intervalles entre les événements. Si une tâche périodique doit être déclenchée toutes les 10 ms, mais que le temps réel varie entre 9 ms et 12 ms, le diagramme de temporisation peut montrer cette variation. Cela est crucial pour les systèmes de diffusion audio/vidéo ou le traitement des paquets réseau.

Éléments techniques des diagrammes de temporisation 🔧

Pour utiliser efficacement les diagrammes de temporisation, il faut comprendre les éléments UML spécifiques impliqués. Ces éléments diffèrent de la notation standard des diagrammes de séquence.

Variables d’état

Contrairement aux diagrammes de séquence qui se concentrent sur les lignes de vie des objets, les diagrammes de temporisation se concentrent souvent sur les variables d’état. Une variable peut être modélisée comme une ligne de vie où les changements d’état sont représentés par des étapes. Par exemple, une variabletempératurepeut avoir une transition d’état de normalà critiqueà un instant précis.

Contraintes de temporisation

Ce sont des annotations attachées aux transitions ou aux événements. Elles définissent la relation temporelle. Les contraintes courantes incluent :

- minimum : Le moment le plus tôt auquel un événement peut se produire.

- maximum : Le moment le plus tardif auquel un événement doit se produire.

- exact : Un instant précis pour un événement.

- plage : Une fenêtre de temps durant laquelle un événement doit se produire.

Valeurs des signaux

Les diagrammes de temporisation peuvent afficher la valeur des signaux au fil du temps. Cela est utile pour surveiller les charges des bus ou les débits de données. Une ligne continue peut représenter une valeur de signal, avec des sauts verticaux indiquant des changements dans le flux de données.

Erreurs courantes de modélisation ⚠️

Passer aux diagrammes de timing introduit de nouvelles complexités. Les ingénieurs tombent souvent dans des pièges qui réduisent l’utilité du modèle.

1. Sur-modélisation de la logique statique

Toute interaction n’exige pas un diagramme de timing. Si la logique est strictement séquentielle et que le timing est sans importance, un diagramme de timing ajoute une complexité inutile. Réservez-les aux chemins critiques en performance.

2. Ignorer les domaines d’horloge

Dans les systèmes distribués, différents composants peuvent fonctionner sur des domaines d’horloge différents. Un diagramme de timing suppose un axe temporel synchronisé. Si les composants sont asynchrones, le diagramme doit tenir compte du décalage d’horloge ou utiliser des chronologies séparées avec des points de synchronisation.

3. Unités d’échelle ambigües

Définissez toujours l’échelle temporelle clairement (par exemple, ms, µs, ns). Mélanger les unités sans étiquettes claires conduit à des malentendus. Une échelle de 100 peut signifier 100 millisecondes ou 100 nanosecondes. La clarté est primordiale.

4. Négliger les périodes d’inactivité

La performance est souvent définie par ce qui se produit lorsque le système est inactif. Les diagrammes de timing doivent montrer les périodes d’inactivité afin de calculer les taux d’utilisation. Négliger le temps d’inactivité peut conduire à une surévaluation de la capacité du système.

Intégration avec l’architecture du système 🏗️

Les diagrammes de timing n’existent pas en vase clos. Ils doivent s’intégrer à la documentation plus large de l’architecture du système.

Liens avec les diagrammes de déploiement

Les lignes de vie dans un diagramme de timing doivent correspondre aux nœuds physiques ou aux partitions logiques définies dans le diagramme de déploiement. Cela garantit que l’analyse du timing reflète la topologie réelle du matériel ou du réseau. Par exemple, un délai entre deux lignes de vie doit correspondre à la latence réseau entre les serveurs qu’elles représentent.

Traçabilité jusqu’aux exigences

Chaque contrainte de timing dans le diagramme doit remonter à une exigence non fonctionnelle. Cette traçabilité est essentielle pour la vérification et la validation. Si une exigence stipule « Le système doit répondre en 200 ms », le diagramme de timing doit explicitement afficher cette contrainte et la durée modélisée réelle.

Maintenance et évolution 🔄

Au fur et à mesure que les systèmes évoluent, les diagrammes de timing nécessitent une maintenance. Les caractéristiques de performance évoluent avec les mises à jour, les changements de charge et les évolutions d’infrastructure.

- Contrôle de version :Traitez les diagrammes de timing comme du code. Stockez-les dans des systèmes de contrôle de version pour suivre les modifications des contraintes de timing au fil des versions.

- Profiling des performances :Mettez à jour les diagrammes à partir des données réelles de profiling. Si un composant met plus de temps en production que prévu, mettez à jour la contrainte pour refléter la réalité.

- Mises à jour des scénarios :De nouvelles fonctionnalités introduisent de nouveaux chemins de timing. Assurez-vous que tous les chemins critiques sont mis à jour pour éviter des lacunes dans l’analyse.

Meilleures pratiques pour la modélisation des performances ✅

Pour maximiser la valeur des diagrammes de timing, suivez ces pratiques établies.

- Gardez les lignes de vie simples :Évitez trop de lignes de vie. Concentrez-vous sur le chemin critique. Regroupez les composants connexes si nécessaire.

- Utilisez une notation standard :Conformez-vous aux normes UML 2.5 pour les contraintes et les lignes de vie afin d’assurer une cohérence au sein de l’équipe.

- Mettez en évidence les chemins critiques : Utilisez la couleur ou le gras pour indiquer les chemins qui déterminent les performances globales du système.

- Documentez les hypothèses : Notez toutes les hypothèses formulées concernant la vitesse du réseau ou la puissance de traitement. Ces hypothèses influencent la validité de l’analyse de temporisation.

- Revoyez régulièrement : Prévoyez des revues des diagrammes de temporisation au cours des itérations de conception. La détection précoce des violations de temporisation permet d’économiser un effort important de restructuration ultérieurement.

Considérations finales pour les équipes d’ingénierie 👥

Choisir la bonne notation de modélisation est une décision stratégique. Les diagrammes de séquence restent la norme pour la logique et le flux. Les diagrammes de temporisation sont l’outil spécialisé pour la précision temporelle. Ce choix ne doit pas être arbitraire.

Les équipes doivent évaluer leurs exigences de performance avant de s’engager dans une stratégie de modélisation. Si le système est sensible aux latences, le surcroît de travail lié à la création des diagrammes de temporisation est justifié par la réduction du risque. Si le système est principalement piloté par la logique métier, les diagrammes de séquence restent suffisants.

En fin de compte, l’objectif est la clarté. Que vous utilisiez des diagrammes de séquence ou des diagrammes de temporisation, le diagramme doit transmettre avec précision le comportement du système aux parties prenantes, aux développeurs et aux testeurs. En comprenant les forces spécifiques du diagramme de temporisation, les ingénieurs peuvent s’assurer que les performances ne sont pas une considération secondaire, mais un élément fondamental de la conception.