L’architecture logicielle repose fortement sur une communication précise entre les composants. Lorsqu’il s’agit d’interactions sensibles au temps, le diagramme de timing UML devient un outil indispensable. Cependant, de nombreux ingénieurs considèrent ces diagrammes comme des éléments secondaires ou les confondent avec les diagrammes de séquence. Cette confusion entraîne souvent des exigences ambiguës, un code difficile à gérer et un cycle de développement hanté par des bogues liés au temps. Comprendre les subtilités des contraintes de timing n’est pas facultatif ; c’est une nécessité pour une conception de système robuste.

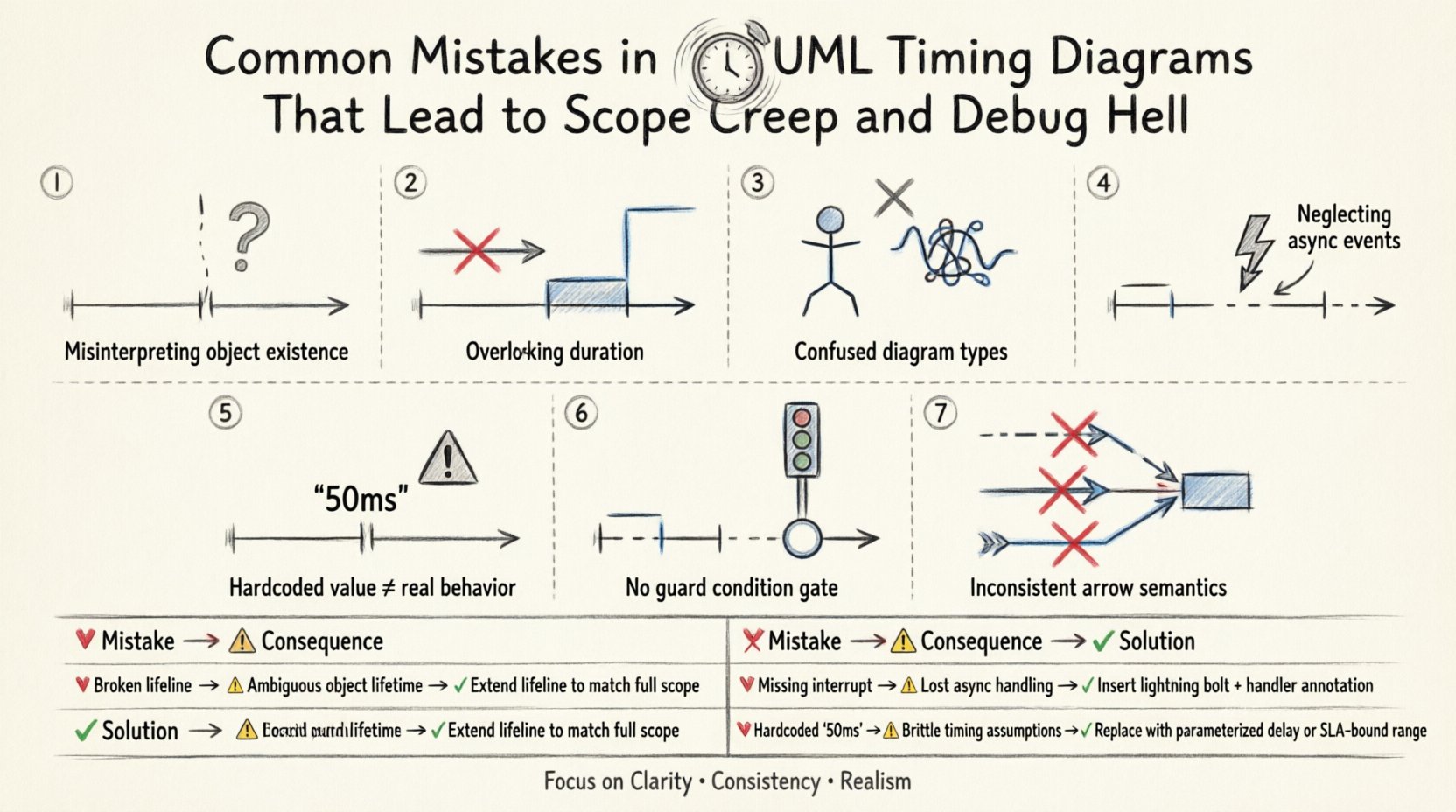

Ce guide explore les pièges spécifiques qui font échouer les projets. Nous examinerons comment mal interpréter les lignes de vie, ignorer les durées des messages ou négliger la documentation des changements d’état peuvent entraîner une cascade de problèmes. En corrigeant ces erreurs tôt, les équipes peuvent éviter l’expansion du périmètre et réduire le temps passé à déboguer des erreurs de timing insidieuses.

1. Mal interpréter les lignes de vie et l’existence des objets 🕰️

La base de tout diagramme de timing est la ligne de vie. Une ligne de vie représente un objet ou un composant au cours d’une période de temps. Une erreur fréquente survient lorsque les concepteurs ne parviennent pas à distinguer la création d’une instance de sa participation active à un processus.

- Supposer une disponibilité constante :De nombreux diagrammes suggèrent qu’un composant existe et est prêt à répondre à chaque instant. En réalité, les composants peuvent être en état d’attente, en cours d’initialisation ou confrontés à une contention de ressources.

- Ignorer la désactivation :Si une ligne de vie reste active indéfiniment sans état de fin clair, cela suggère que l’objet est toujours en écoute. Cela entraîne des fuites de mémoire ou des états de thread non gérés dans l’implémentation.

- Confondre les lignes de vie logiques et physiques :Une ligne de vie logique peut représenter une classe, mais une ligne de vie physique représente un thread ou un processus. Mélanger ces deux sans distinction provoque des erreurs de synchronisation.

Lorsque les lignes de vie ne sont pas correctement définies, les développeurs peuvent allouer des ressources qui ne sont jamais libérées ou échouer à gérer les cas où un composant est temporairement indisponible. Cette ambiguïté oblige l’équipe à ajouter de la logique pour gérer des cas limites non anticipés à l’étape de conception, contribuant directement à l’expansion du périmètre.

2. Ignorer la durée des messages et les barres d’activation ⏱️

Les barres d’activation indiquent la période pendant laquelle un objet effectue une action. Une erreur critique consiste à traiter les messages comme des événements instantanés. Dans les systèmes du monde réel, le traitement prend du temps. Ignorer la durée d’une opération entraîne des conditions de course.

- Messages instantanés :Tracer une flèche de message sans durée implique que l’expéditeur reçoit une réponse immédiatement. Si le destinataire nécessite un traitement important, l’expéditeur peut expirer ou planter.

- Absence de chevauchements :Si deux messages sont planifiés pour s’exécuter simultanément sur le même objet sans file d’attente appropriée, le système peut présenter un comportement indéfini.

- Ignorer le blocage :Certaines opérations bloquent le thread jusqu’à leur achèvement. Si le diagramme ne montre pas cette période de blocage, l’architecte peut supposer que le thread est libre pour gérer d’autres tâches, ce qui entraîne des blocages.

En ne modélisant pas avec précision la largeur des barres d’activation, l’équipe d’implémentation construit des systèmes incapables de gérer une latence réaliste. Lorsque des goulets d’étranglement de performance apparaissent, la faute est souvent attribuée au code, alors que la cause réelle était un diagramme qui promettait une exécution plus rapide que ce que le matériel pouvait fournir.

3. Confondre les diagrammes de timing avec les diagrammes de séquence 🔄

Bien que les deux diagrammes montrent des interactions, ils ont des objectifs différents. Un diagramme de séquence se concentre sur l’ordre des messages. Un diagramme de timing se concentre sur les contraintes temporelles et les changements d’état des objets. Mélanger ces responsabilités crée de la confusion.

- Ordre vs. Temps :Un diagramme de séquence montre que le message B a lieu après le message A. Un diagramme de timing montre que le message B doit avoir lieu dans les 50 millisecondes suivant le message A.

- Représentation de l’état :Les diagrammes de timing doivent montrer explicitement les changements d’état (par exemple, une notation de machine à états) le long de la ligne de vie. Les diagrammes de séquence ne se concentrent généralement pas à ce niveau de détail.

- Parallélisme :Les diagrammes de timing sont supérieurs pour montrer les chemins de traitement parallèle. Les diagrammes de séquence placent souvent ces interactions dans une seule chronologie, cachant les problèmes de concurrence.

Utiliser un diagramme de séquence pour une logique critique en temps oblige les développeurs à inférer des contraintes de timing qui n’ont jamais été explicitement énoncées. Cette inférence est un terreau fertile pour les bogues. Les développeurs font des hypothèses sur la latence et le débit, et lorsque ces hypothèses échouent, le débogage devient un cauchemar.

4. Ignorer les événements asynchrones et les interruptions ⚡

Les systèmes sont rarement parfaitement synchrones. Les événements externes, les interruptions et les rappels asynchrones se produisent de manière imprévisible. Une erreur courante consiste à modéliser uniquement le parcours idéal de manière linéaire.

- Interruptions manquantes : Si une interruption de haute priorité se produit, elle peut interrompre une tâche de basse priorité. Si le diagramme ne montre pas cette interruption, l’implémentation du planificateur sera incorrecte.

- Ignorer les délais d’attente : Chaque appel asynchrone doit disposer d’un mécanisme de délai d’attente. Omettre de marquer la période de délai dans le diagramme entraîne des processus bloqués qui consomment indéfiniment des ressources système.

- File d’attente des événements : Comment les événements sont-ils mis en mémoire tampon ? Si le diagramme montre des événements arrivant plus vite qu’ils ne peuvent être traités, le système doit afficher une file d’attente. Ignorer cela entraîne une perte de données en production.

Déboguer les problèmes asynchrones est particulièrement difficile car ils sont non déterministes. Si la conception ne tient pas compte du moment de ces événements, le code aura des difficultés à maintenir une cohérence. Cela entraîne souvent des tests instables qui passent localement mais échouent dans des environnements de production avec des profils de charge différents.

5. Durcir les contraintes de temporisation dans la conception 📏

L’une des erreurs les plus insidieuses consiste à intégrer directement dans le diagramme des valeurs temporelles spécifiques (par exemple, « 50 ms ») sans contexte. Cela crée une conception fragile incapable de s’adapter aux environnements changeants.

- Dépendance de l’environnement : Un délai de 50 ms peut être acceptable sur un serveur local, mais inacceptable sur un périphérique réseau présentant une latence élevée. Le durcissement des valeurs attache la conception à une infrastructure spécifique.

- Manque de scalabilité : Au fur et à mesure que le système évolue, les contraintes de temporisation changent souvent. Si le diagramme est rigide, mettre à jour la conception exige une refonte complète de la documentation.

- Variables manquantes : Au lieu de valeurs fixes, utilisez des variables ou des paramètres (par exemple, Max_TempsDeLatence). Cela permet à l’implémentation de configurer les seuils en fonction de l’environnement de déploiement.

Lorsque les contraintes sont durcies, l’équipe perd de la flexibilité. Si la demande métier change pour prendre en charge une nouvelle région avec une latence plus élevée, toute l’architecture doit être réévaluée. Une bonne conception sépare la logique de temporisation des détails d’implémentation.

6. Oublier de documenter les conditions de garde 🚦

Les diagrammes de temporisation montrent souvent un flux d’événements, mais ils omettent fréquemment les conditions nécessaires à la survenue de ces événements. Un message pourrait être envoyé uniquement si un état spécifique est atteint. Sans ce contexte, le destinataire est laissé dans l’incertitude.

- Logique implicite : Si un message est envoyé uniquement lorsque

code_erreur == 0, cela doit être visible. Si cela est caché, le développeur pourrait implémenter la logique du message sans la condition de garde, ce qui entraîne des erreurs. - Transitions d’état :Les diagrammes de temporisation doivent être alignés avec les diagrammes d’états. Si le diagramme montre l’envoi d’un message, mais que le diagramme d’états indique que cet état est inatteignable, la conception est contradictoire.

- Logique complexe :Les expressions booléennes complexes doivent être documentées dans des notes attachées au message ou à la ligne de vie. Se fier à des modèles mentaux de la logique est insuffisant pour les systèmes complexes.

Lorsqu’il manque des conditions de garde, les développeurs écrivent du code pour gérer des états qui ne devraient jamais se produire. Cela alourdit la base de code et augmente la surface d’erreurs. Cela rend également le code plus difficile à maintenir, car la logique de gestion des exceptions est répartie.

7. Notation et normes incohérentes 📝

UML est une norme, mais les équipes créent souvent leurs propres variantes. Une notation incohérente entraîne des malentendus entre les membres de l’équipe et les parties prenantes.

- Styles des flèches :Les lignes pleines signifient généralement des appels synchrones, tandis que les lignes pointillées signifient des appels asynchrones. Les mélanger confond le modèle d’exécution.

- Notation pour les délais : Certaines équipes utilisent des crochets, d’autres du texte. La cohérence est essentielle pour les outils de traitement automatique ou les générateurs de documentation.

- Libellés : Les messages doivent être clairement étiquetés avec leur objectif. Des libellés ambigus comme « Traiter les données » sont insuffisants. Ils devraient être « Valider l’entrée » ou « Enregistrer la fiche ».

La cohérence réduit la charge cognitive de l’équipe. Lorsque tout le monde suit les mêmes règles, la lecture d’un diagramme ne prend que quelques secondes au lieu de plusieurs minutes. Cette efficacité est cruciale lors de la revue des conceptions pour des problèmes de synchronisation potentiels.

Péchés courants vs. Bonnes pratiques

Le tableau suivant résume les erreurs les plus fréquentes et leurs solutions correspondantes. Utilisez-le comme liste de contrôle lors de vos revues de conception.

| 🔴 Erreur courante | ⚠️ Conséquence | ✅ Bonne pratique |

|---|---|---|

| Supposer que les messages sont instantanés | Délais d’attente et conditions de course | Dessiner les barres d’activation avec des durées réalistes |

| Ignorer les interruptions asynchrones | Bloquages et fuites de ressources | Modéliser explicitement la préemption et la file d’attente |

| Durcir des valeurs spécifiques en millisecondes | Conception fragile, faible évolutivité | Utiliser des variables ou des paramètres pour les contraintes de temps |

| Mélanger la logique de séquence et la logique de temporisation | Exigences ambigües | Utiliser la séquence pour l’ordre, la temporisation pour les contraintes |

| Omettre les conditions de garde | Chemins de code inutiles | Annoter les conditions sur les flèches de message |

| Notation incohérente | Mauvaise interprétation par l’équipe | Adopter et imposer une norme commune à toute l’équipe |

8. L’impact sur les tests et la vérification 🧪

Un schéma de timing mal conçu affecte directement la stratégie de test. Si le schéma ne précise pas les contraintes de timing, les testeurs ne peuvent pas rédiger des tests efficaces pour ces contraintes.

- Manque de couverture de test : Sans objectifs de timing explicites, les testeurs peuvent se concentrer sur la correction fonctionnelle et manquer les violations de timing.

- Tests non déterministes : Si le timing n’est pas modélisé, les tests peuvent réussir sur une machine et échouer sur une autre en raison de différences matérielles.

- Problèmes d’intégration : Les incompatibilités de timing entre les modules apparaissent souvent uniquement lors de l’intégration. Une modélisation précoce permet de détecter ces problèmes avant l’écriture du code.

Investir du temps dans des diagrammes précis rapporte des bénéfices lors de la phase de test. Cela permet de créer des tests de performance qui valident l’architecture par rapport au design, et non seulement au code.

9. Barrières de communication avec les parties prenantes 🗣️

Les diagrammes de timing ne sont pas uniquement destinés aux développeurs. Ils sont souvent utilisés pour communiquer avec les chefs de projet et les clients concernant les attentes de performance du système.

- Gestion des attentes : Si le schéma indique un temps de réponse de 1 seconde, mais que l’implémentation prend 5 secondes, la confiance s’effrite. Le schéma doit refléter des capacités réalistes.

- Définition du périmètre :Les contraintes de timing définissent le périmètre. Si un client demande une performance en temps réel mais que le schéma montre un traitement par lots, le périmètre est mal défini.

- Gestion des changements : Lorsque les exigences changent, le schéma doit être mis à jour immédiatement. Les schémas obsolètes entraînent des travaux réalisés qui ne répondent pas aux nouvelles exigences.

Une documentation claire empêche le débordement de périmètre en rendant les limites du système explicites. Si une fonctionnalité nécessite une contrainte de timing non modélisée, elle peut être identifiée comme hors périmètre dès le début.

10. Le coût du débogage des problèmes de timing 🐞

Le débogage des problèmes de timing est nettement plus coûteux que le débogage de la logique fonctionnelle. Vous ne pouvez souvent pas reproduire facilement le problème car il dépend de conditions de charge spécifiques ou de conditions de course.

- Difficulté de reproduction : Si un bug ne survient que lorsque deux threads interagissent en moins de 10 ms, sa reproduction nécessite un environnement contrôlé.

- Exigences en outillage :Le débogage du timing nécessite souvent des profilers ou des outils d’audit spécialisés, ce qui ajoute de la complexité à l’environnement de développement.

- Risque en production :Les bogues de timing apparaissent souvent sous charge, ce qui signifie qu’ils pourraient ne pas être détectés avant que le système soit mis en production.

En évitant ces erreurs à la phase de conception, les équipes économisent des ressources considérables. Le coût de correction d’une erreur dans un diagramme est négligeable par rapport au coût de correction d’un système déployé présentant des vulnérabilités de timing.

Réflexions finales sur la précision du timing 🎯

Créer des diagrammes de timing UML précis exige de la discipline et une attention aux détails. Il ne suffit pas de dessiner des lignes et des flèches ; il faut comprendre le comportement fondamental du système. En évitant les pièges courants décrits dans ce guide, les équipes peuvent construire des systèmes robustes, maintenables et performants.

Souvenez-vous que le diagramme est un contrat entre la conception et l’implémentation. Si ce contrat est flou, l’implémentation en pâtira. Traitez les diagrammes de timing avec le même rigueur que les spécifications fonctionnelles. Cette approche épargnera à votre équipe les maux de tête dus au débordement de portée et la frustration du chaos du débogage.

Concentrez-vous sur la clarté, la cohérence et la réalisme. Ces trois piliers garantiront que vos diagrammes de timing remplissent efficacement leur rôle, guidant le processus de développement vers le succès sans détours inutiles.